本帖最后由 天涯行客 于 2014-12-4 12:37 编辑

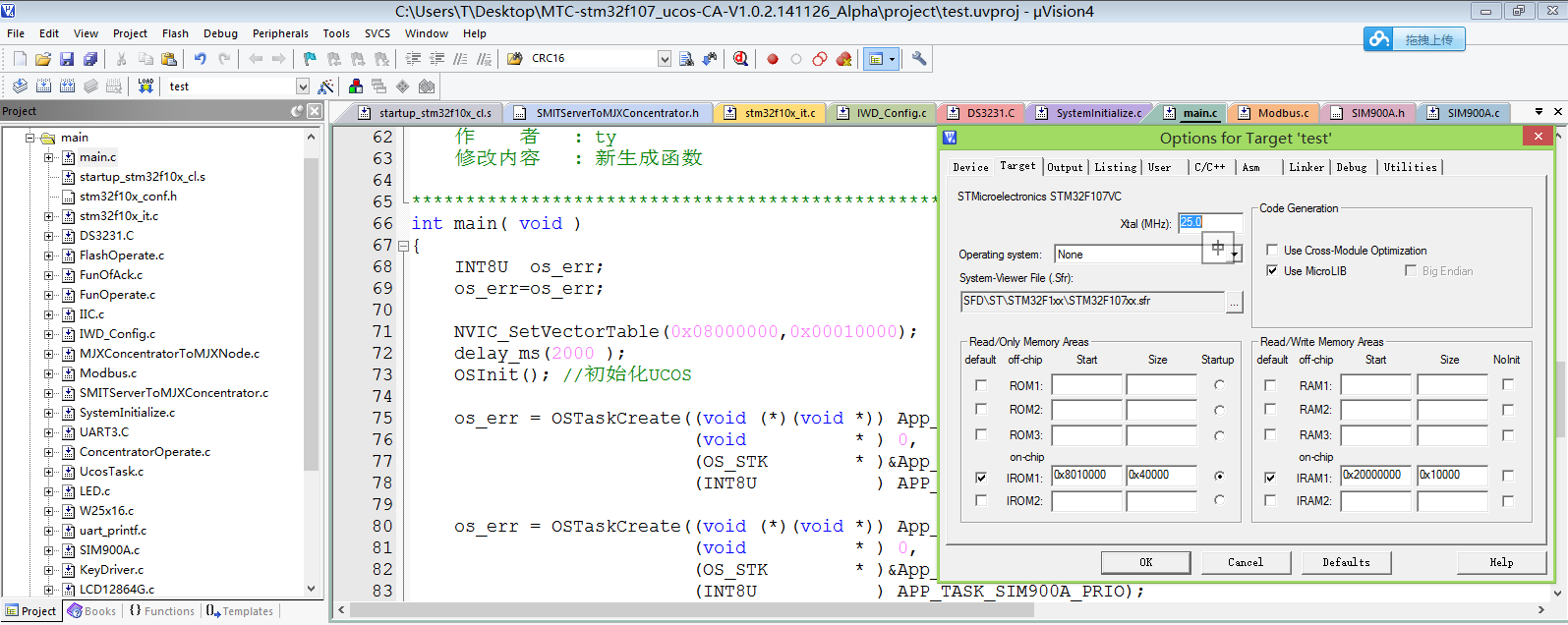

程序所有配置都没有问题,就是不执行APP程序,不知道怎么回事啊

2014-12-04_105927.png (77.37 KB, 下载次数: 4)

下载附件

2014-12-4 11:00 上传

2014-12-04_105927.png (77.37 KB, 下载次数: 4)

下载附件

2014-12-4 11:00 上传

程序跳转代码

if (((*(__IO uint32_t*)ApplicationAddress) & 0x2FFE0000 ) == 0x20000000)

{

SerialPutString("Execute user Program ");

JumpAddress = *(__IO uint32_t*) (ApplicationAddress + 4);

Jump_To_Application = (pFunction) JumpAddress;

__set_MSP(*(__IO uint32_t*) ApplicationAddress);

Jump_To_Application();

}

#define ApplicationAddress 0x8010000

我APP程序比较大 生成的BIN文件有60K左右,会是堆栈溢出的问题吗?

正解在5楼

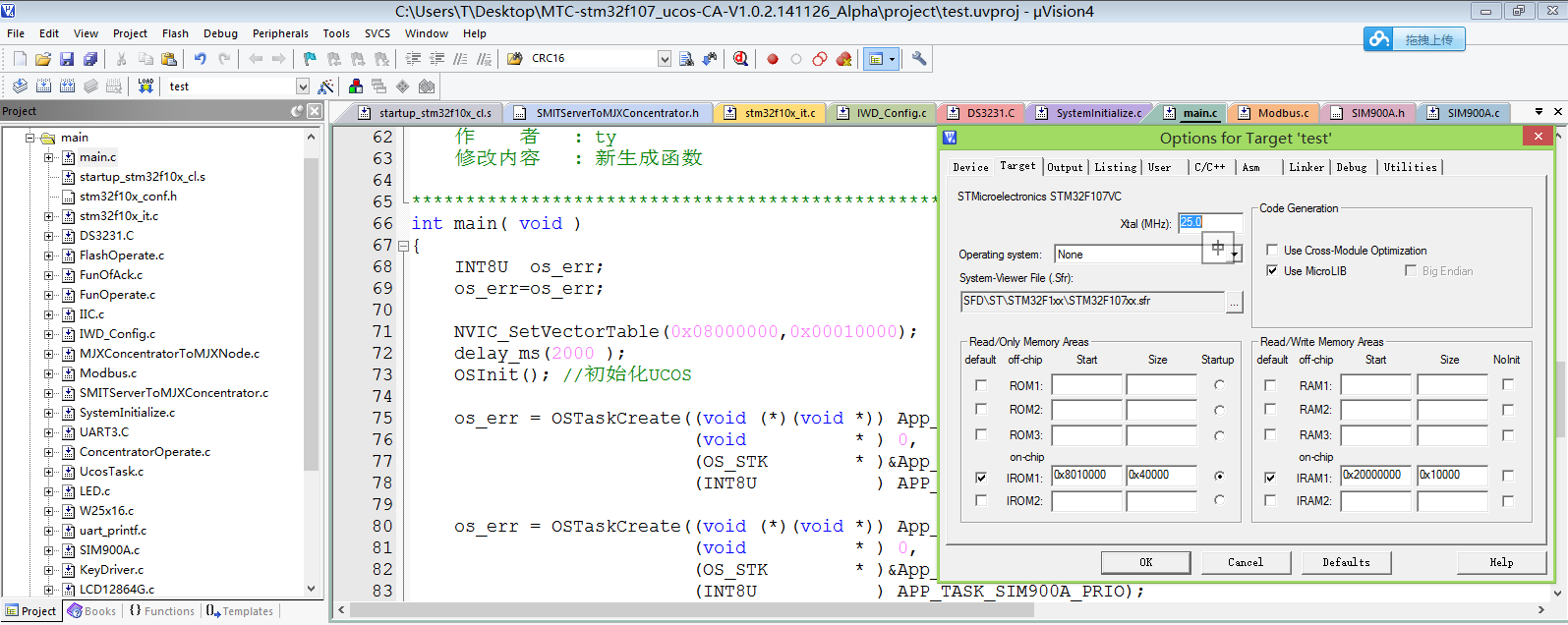

程序所有配置都没有问题,就是不执行APP程序,不知道怎么回事啊

2014-12-04_105927.png (77.37 KB, 下载次数: 4)

下载附件

2014-12-4 11:00 上传

2014-12-04_105927.png (77.37 KB, 下载次数: 4)

下载附件

2014-12-4 11:00 上传

程序跳转代码

if (((*(__IO uint32_t*)ApplicationAddress) & 0x2FFE0000 ) == 0x20000000)

{

SerialPutString("Execute user Program ");

JumpAddress = *(__IO uint32_t*) (ApplicationAddress + 4);

Jump_To_Application = (pFunction) JumpAddress;

__set_MSP(*(__IO uint32_t*) ApplicationAddress);

Jump_To_Application();

}

#define ApplicationAddress 0x8010000

我APP程序比较大 生成的BIN文件有60K左右,会是堆栈溢出的问题吗?

正解在5楼

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

找到原因了 就是在 NVIC_SetVectorTable(0x08000000,0x0010000);之后 不能再调用函数void SystemInit (void)

void SystemInit (void)

{

/* Reset the RCC clock configuration to the default reset state(for debug purpose) */

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001;

/* Reset SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits */

#ifndef STM32F10X_CL

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else

RCC->CFGR &= (uint32_t)0xF0FF0000;

#endif /* STM32F10X_CL */

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF;

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF;

/* Reset PLLSRC, PLLXTPRE, PLLMUL and USBPRE/OTGFSPRE bits */

RCC->CFGR &= (uint32_t)0xFF80FFFF;

#ifdef STM32F10X_CL

/* Reset PLL2ON and PLL3ON bits */

RCC->CR &= (uint32_t)0xEBFFFFFF;

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x00FF0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#else

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

#endif /* STM32F10X_CL */

#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)

#ifdef DATA_IN_ExtSRAM

SystemInit_ExtMemCtl();

#endif /* DATA_IN_ExtSRAM */

#endif

/* Configure the System clock frequency, HCLK, PCLK2 and PCLK1 prescalers */

/* Configure the Flash Latency cycles and enable prefetch buffer */

SetSysClock();

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM. */

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH. */

#endif

}

一周热门 更多>