无标题.png (93.97 KB, 下载次数: 0)

下载附件

2019-8-18 23:01 上传

无标题.png (93.97 KB, 下载次数: 0)

下载附件

2019-8-18 23:01 上传

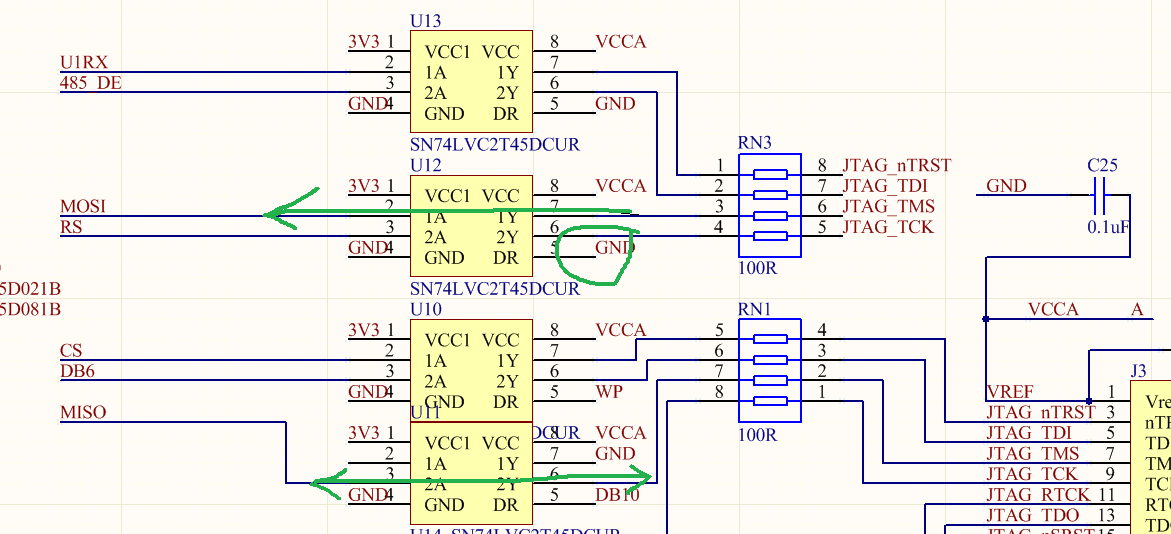

如图,我看这个接口就是使用的STM32F205的SPI1,CLK是JLINK发出的,那就是使用的SPI主机模式了,

JATG_TMS是SWDIO引脚,可是U12的方向控制接地,意味着MOSI这个位置上,缓冲器始终是输入状态,可以主机的MOSI不应该是输出吗。

难道是表面上使用的是SPI实际上却是IO模拟的接口,把SPI的主机和从机引脚反过来使用了。好蛋疼的结论。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

看SWD的时序,并不是标准的8-16-32位,比如那个ACK就只有3位,我估计这个应该用标准的SPI实现不了,所以尽管JLINK的硬件是接在了205的SPI1上,但是实际上还是IO模拟来实现的SWD协议吧。

这个用作输出的IO,在SWDIO接收状态下应该是设置为高阻状态了或者开漏输出1,真正负责接收的是另外一个用作输入的IO,

一周热门 更多>