本帖最后由 FSL_FAE_JiCheng 于 2016-3-27 13:23 编辑

坐在上海回北京的高铁上,漫长的旅途着实让人感到无聊(没买到直达的高铁,只能慢悠悠的走一站停一站,晕,都高铁时代了,竟然还这样,想起了大学放假回家站十几个小时绿皮车的时光啊,哈哈),遂有点“写心萌动”,不由感叹——“春”天真是来了,春为啥加引号捏,我相信大家都懂的,哈哈。这样也好,俺又可以慢悠悠的写作抒情了,走着。。。

其实都搞了这么长时间的ARM开发,关于其至关重要的中断优先级问题我早就想跟大家伙分享分享了,可惜一方面想真正的讲清楚这个问题估计又得大费周章和墨水,另一方面自己越来越忙进一步导致写文章倒是越来越懒了,呵呵。所以趁着坐高铁无聊赶紧撸胳膊抹袖子整吧,不然把这么重要的内容放在自己脑子里封存落灰实在是颇为浪费呀,哈哈。那就不多扯淡了,再多扯火车到站了就尴尬了,咳咳。。。

对于中断优先级配置的需求实际上主要体现在系统存在多个可能的中断源情况下,这时为了保证代码的可靠执行,我们不得不考虑很现实的两个问题,一个是如果两个以上中断同时发生,pending请求到CPU,CPU决策该先进哪一个相应的中断服务Routine,第二个问题是CPU当前已经在响应某个中断服务,此时来了另一个中断请求,是否允许其打断当前中断服务转而响应新的中断请求即我们常说的中断嵌套问题,不要告诉我没考虑过哈(如果真是这样,我只能不客气的说,这样搞单片机是不负责任的,很可能给项目带来潜在的风险bug),那样的话俺也白写了,呵呵。那正题来了,对现在红红火火的ARM Cortex-M4和M0+两个核来说,他们是如何解决这两个问题的呢,因为这两个核在中断优先级管理上略有些区别(虽然都是NVIC和SCB两个寄存器来管理),所以下面我分开来说,另外由于中断优先级管理属于内核问题,所以这方面的信息你不会在各大半导体厂家的官方手册中找到,我们只能追根溯源直接到内核的老家ARM官网去找,建议大家有兴趣的到ARM官网把M4和M0+的内核手册下载下来简单瞅瞅,可能会有意想不到的收获哦,呵呵:

ARM Cortex-M0+中断优先级和嵌套

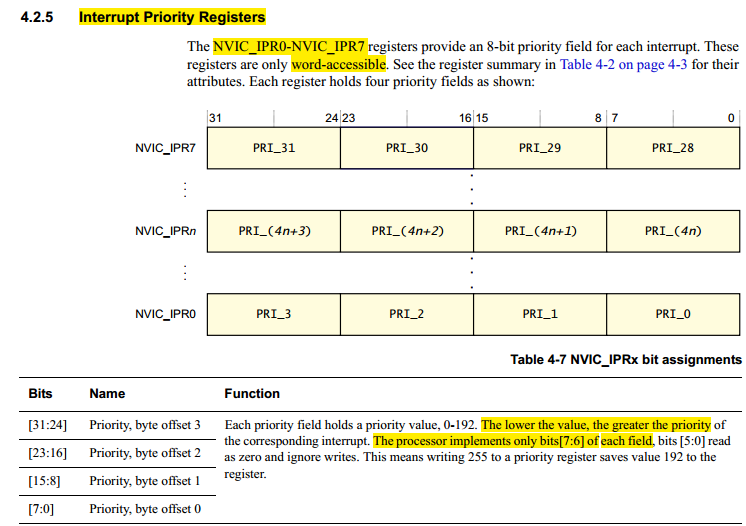

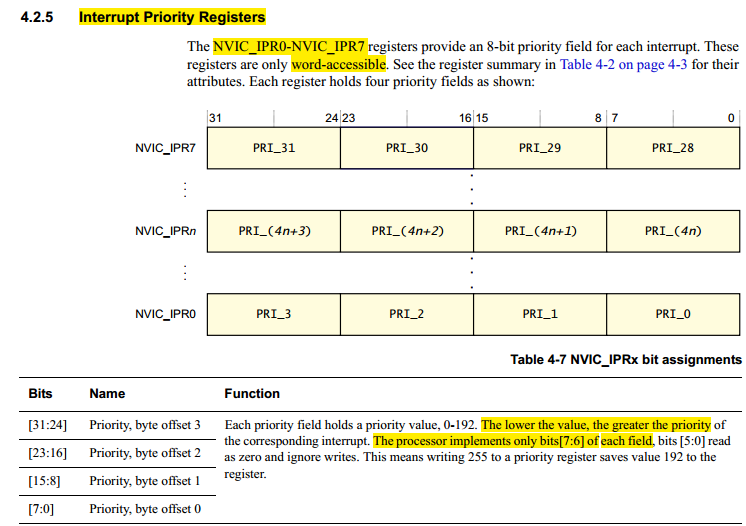

无论是M0+或者是M4内核,实际上他们两个的中断优先级都是由NVIC和SCB两个寄存器来管理的,在这里我默认大家都知道ARM的中断源分为内核中断和IRQ中断了哈(我怕再细讲下去又没完了,呵呵),而对IRQ的中断管理是由NVIC来主导的,内核的中断管理则是由SCB来主导的,我们先讲IRQ中断的优先级问题(关于中断使能和禁能不在本篇讨论范围内),打开M0+的内核手册找到NVIC_IPR寄存器(Interrupt Priority Registers)如下图所示:

Capture6.PNG (25.15 KB, 下载次数: 0)

下载附件

2016-3-26 22:20 上传

Capture6.PNG (25.15 KB, 下载次数: 0)

下载附件

2016-3-26 22:20 上传

呼。。。终于搞完了,总算把这个问题给写出来了,我脑袋里可以腾出点地方给其他问题了,哈哈。另外实际上我上面写了这么多理论的东西,但是ARM早已在CMSIS库里的头文件中把这部分函数API给出来了(core_cm4.h和core_cm0plus.h),而我之所以不闲麻烦的还是把这个写出来,还是我这个知其然也要知其所以然的思想在作怪了。不过最后,我还是给出M0+和M4的中断优先级配置的两个配置供广大博友参考吧,然后其他就不多聊了,未完待续:

M0+

NVIC_SetPriority(PORTA_IRQn, 1);

NVIC_SetPriority(PORTB_IRQn, 2);

M4+

NVIC_SetPriorityGrouping(0x03);

NVIC_SetPriority(PORTA_IRQn, NVIC_EncodePriority(0x03,1, 2));

NVIC_SetPriority(PORTB_IRQn, NVIC_EncodePriority(0x03, 2, 2));

坐在上海回北京的高铁上,漫长的旅途着实让人感到无聊(没买到直达的高铁,只能慢悠悠的走一站停一站,晕,都高铁时代了,竟然还这样,想起了大学放假回家站十几个小时绿皮车的时光啊,哈哈),遂有点“写心萌动”,不由感叹——“春”天真是来了,春为啥加引号捏,我相信大家都懂的,哈哈。这样也好,俺又可以慢悠悠的写作抒情了,走着。。。

其实都搞了这么长时间的ARM开发,关于其至关重要的中断优先级问题我早就想跟大家伙分享分享了,可惜一方面想真正的讲清楚这个问题估计又得大费周章和墨水,另一方面自己越来越忙进一步导致写文章倒是越来越懒了,呵呵。所以趁着坐高铁无聊赶紧撸胳膊抹袖子整吧,不然把这么重要的内容放在自己脑子里封存落灰实在是颇为浪费呀,哈哈。那就不多扯淡了,再多扯火车到站了就尴尬了,咳咳。。。

对于中断优先级配置的需求实际上主要体现在系统存在多个可能的中断源情况下,这时为了保证代码的可靠执行,我们不得不考虑很现实的两个问题,一个是如果两个以上中断同时发生,pending请求到CPU,CPU决策该先进哪一个相应的中断服务Routine,第二个问题是CPU当前已经在响应某个中断服务,此时来了另一个中断请求,是否允许其打断当前中断服务转而响应新的中断请求即我们常说的中断嵌套问题,不要告诉我没考虑过哈(如果真是这样,我只能不客气的说,这样搞单片机是不负责任的,很可能给项目带来潜在的风险bug),那样的话俺也白写了,呵呵。那正题来了,对现在红红火火的ARM Cortex-M4和M0+两个核来说,他们是如何解决这两个问题的呢,因为这两个核在中断优先级管理上略有些区别(虽然都是NVIC和SCB两个寄存器来管理),所以下面我分开来说,另外由于中断优先级管理属于内核问题,所以这方面的信息你不会在各大半导体厂家的官方手册中找到,我们只能追根溯源直接到内核的老家ARM官网去找,建议大家有兴趣的到ARM官网把M4和M0+的内核手册下载下来简单瞅瞅,可能会有意想不到的收获哦,呵呵:

ARM Cortex-M0+中断优先级和嵌套

无论是M0+或者是M4内核,实际上他们两个的中断优先级都是由NVIC和SCB两个寄存器来管理的,在这里我默认大家都知道ARM的中断源分为内核中断和IRQ中断了哈(我怕再细讲下去又没完了,呵呵),而对IRQ的中断管理是由NVIC来主导的,内核的中断管理则是由SCB来主导的,我们先讲IRQ中断的优先级问题(关于中断使能和禁能不在本篇讨论范围内),打开M0+的内核手册找到NVIC_IPR寄存器(Interrupt Priority Registers)如下图所示:

Capture6.PNG (25.15 KB, 下载次数: 0)

下载附件

2016-3-26 22:20 上传

Capture6.PNG (25.15 KB, 下载次数: 0)

下载附件

2016-3-26 22:20 上传

呼。。。终于搞完了,总算把这个问题给写出来了,我脑袋里可以腾出点地方给其他问题了,哈哈。另外实际上我上面写了这么多理论的东西,但是ARM早已在CMSIS库里的头文件中把这部分函数API给出来了(core_cm4.h和core_cm0plus.h),而我之所以不闲麻烦的还是把这个写出来,还是我这个知其然也要知其所以然的思想在作怪了。不过最后,我还是给出M0+和M4的中断优先级配置的两个配置供广大博友参考吧,然后其他就不多聊了,未完待续:

M0+

NVIC_SetPriority(PORTA_IRQn, 1);

NVIC_SetPriority(PORTB_IRQn, 2);

M4+

NVIC_SetPriorityGrouping(0x03);

NVIC_SetPriority(PORTA_IRQn, NVIC_EncodePriority(0x03,1, 2));

NVIC_SetPriority(PORTB_IRQn, NVIC_EncodePriority(0x03, 2, 2));

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>