本帖最后由 FSL_FAE_JiCheng 于 2016-3-26 22:25 编辑

高铁模式继续开启,喝了一口凉白开,啃了口肯德基鸡腿,开始码字啦(这画面太美好了有木有…)。写到这,我突然感觉自己越来越有宅男的气质了。说起宅的话不得不提一下最近网络比较火的“御宅”一词,笔者刚看完最强大脑最新的一期,玩俄罗斯方块的日本天才,号称“御宅”一族,真是把我惊到了,人家真是宅出技术宅出境界来了啊,在拜服的同时又有点小小的得意自豪啊,俺这宅在高铁上也是宅呀,起码从这点上来看,俺跟这些天才还是站在一个高度上了,咳咳。。。

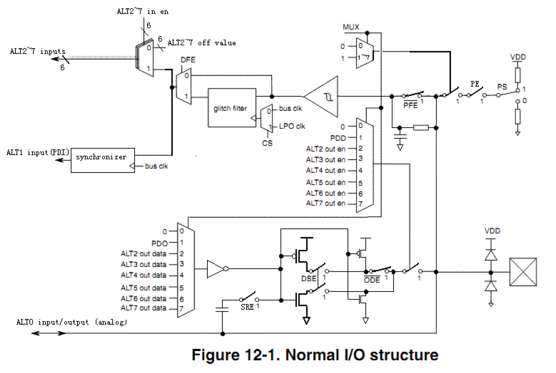

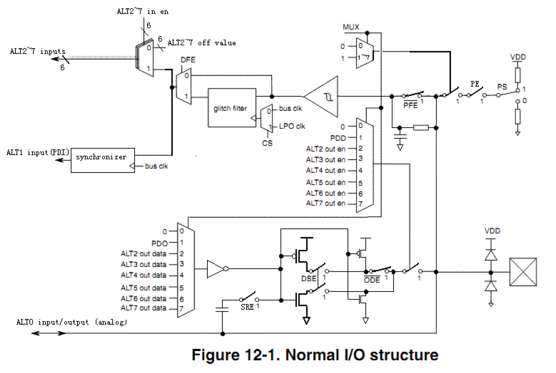

好了,聊完“宅”之后(聊宅?聊斋?咳咳,看来蒲松龄老人家估计也是宅的够呛)咱还是继续聊技术吧。本篇博文的题目俺之所以后加了个“内附祥图”这几个关键词实际上是有点小心机的,呵呵,就像大家看新闻头条都喜欢看带图片的一样。毕竟一提到要讲芯片的IO结构,估计好多人会觉着GPIO有啥好讲的没有啥技术含量,而我的目的就是把这些人也吸引进来,等到大家看完整篇文章之后就会明白俺的良苦用心了,我们之前使用IO都是知其然不知其所以然(配置个方向寄存器和输入输出寄存器就完了,却没有了解到芯片内部逻辑是怎么做到的),而我写这篇文章的目的就是想让大家知其所以然,在以后使用的过程中出现一些比较隐藏的问题时我们也可以有据可依,按图索骥找到问题的根本所在。下面我先上个飞思卡尔(NXP)ARM家族的Kinetis系列内部IO的结构框图(新鲜出炉哦)和其用户手册中的PORT管脚配置寄存器的内容,大家先看看图把图中的一些字符和寄存器的配置位对上号,然后下面我就列出几个平时大家都会用到几个问题,以及这些问题是如何通过下面IO结构框图来解释的,Ready。。。Go:

Capture10.PNG (48.41 KB, 下载次数: 0)

下载附件

2016-3-26 22:13 上传

Capture10.PNG (48.41 KB, 下载次数: 0)

下载附件

2016-3-26 22:13 上传

好了,今天就写到这里了,IO这个问题虽然看似简单,但是实际上深究起来还是很多学问的是吧,希望大家看下来能有所收获,哈哈。另外,在这里我需要再提一下关于转载我博客的问题,一直有很多博友转载分享我的文章,首先是灰常感谢的(这说明俺写的还是深得民意滴),不过还是希望大家在转载时注意加上文章的出处原链接和俺这个作者的大名啊(俺自己转就不用了哈,嘿嘿),不然的话……,不然我也没办法了,呵呵,虽然很无奈但是我心里还是有点深深的那份执着,希望我们国内对知识产权的重视能越来越重视,这个还是靠我们广大工程师们的共同努力地,fighting。。。

再聊,未完待续~

高铁模式继续开启,喝了一口凉白开,啃了口肯德基鸡腿,开始码字啦(这画面太美好了有木有…)。写到这,我突然感觉自己越来越有宅男的气质了。说起宅的话不得不提一下最近网络比较火的“御宅”一词,笔者刚看完最强大脑最新的一期,玩俄罗斯方块的日本天才,号称“御宅”一族,真是把我惊到了,人家真是宅出技术宅出境界来了啊,在拜服的同时又有点小小的得意自豪啊,俺这宅在高铁上也是宅呀,起码从这点上来看,俺跟这些天才还是站在一个高度上了,咳咳。。。

好了,聊完“宅”之后(聊宅?聊斋?咳咳,看来蒲松龄老人家估计也是宅的够呛)咱还是继续聊技术吧。本篇博文的题目俺之所以后加了个“内附祥图”这几个关键词实际上是有点小心机的,呵呵,就像大家看新闻头条都喜欢看带图片的一样。毕竟一提到要讲芯片的IO结构,估计好多人会觉着GPIO有啥好讲的没有啥技术含量,而我的目的就是把这些人也吸引进来,等到大家看完整篇文章之后就会明白俺的良苦用心了,我们之前使用IO都是知其然不知其所以然(配置个方向寄存器和输入输出寄存器就完了,却没有了解到芯片内部逻辑是怎么做到的),而我写这篇文章的目的就是想让大家知其所以然,在以后使用的过程中出现一些比较隐藏的问题时我们也可以有据可依,按图索骥找到问题的根本所在。下面我先上个飞思卡尔(NXP)ARM家族的Kinetis系列内部IO的结构框图(新鲜出炉哦)和其用户手册中的PORT管脚配置寄存器的内容,大家先看看图把图中的一些字符和寄存器的配置位对上号,然后下面我就列出几个平时大家都会用到几个问题,以及这些问题是如何通过下面IO结构框图来解释的,Ready。。。Go:

Capture10.PNG (48.41 KB, 下载次数: 0)

下载附件

2016-3-26 22:13 上传

Capture10.PNG (48.41 KB, 下载次数: 0)

下载附件

2016-3-26 22:13 上传

好了,今天就写到这里了,IO这个问题虽然看似简单,但是实际上深究起来还是很多学问的是吧,希望大家看下来能有所收获,哈哈。另外,在这里我需要再提一下关于转载我博客的问题,一直有很多博友转载分享我的文章,首先是灰常感谢的(这说明俺写的还是深得民意滴),不过还是希望大家在转载时注意加上文章的出处原链接和俺这个作者的大名啊(俺自己转就不用了哈,嘿嘿),不然的话……,不然我也没办法了,呵呵,虽然很无奈但是我心里还是有点深深的那份执着,希望我们国内对知识产权的重视能越来越重视,这个还是靠我们广大工程师们的共同努力地,fighting。。。

再聊,未完待续~

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

一周热门 更多>