{if =='编辑问题'}

一、I.MX6U处理器GPIO的命名

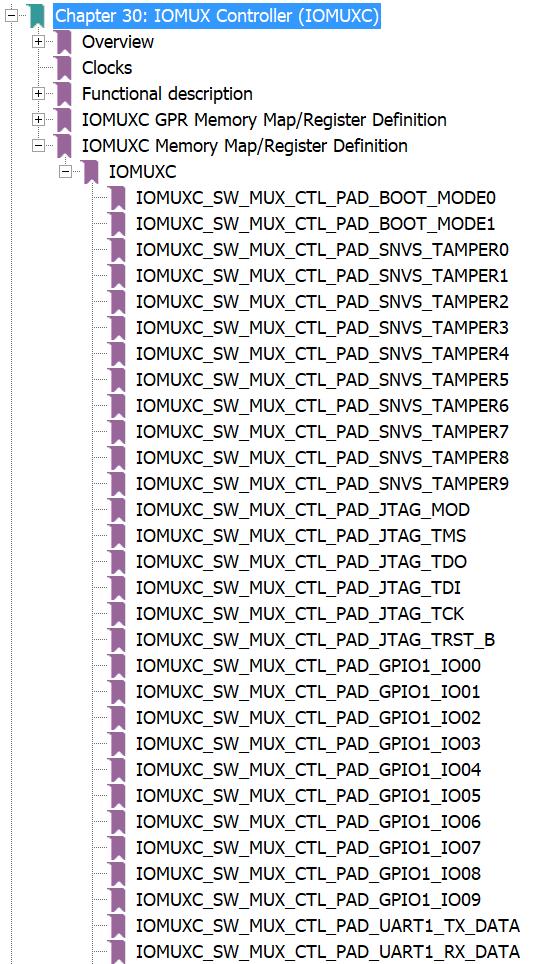

STM32 中的 IO 都是 PA0~15、PB0~15 这样命名的,I.MX6U 的 IO 是怎么命名的呢?打开NXP官方提供的《I.MX6UL 参考手册》的第 30 章“Chapter 30: IOMUX Controller(IOMUXC)”,第 30 章的目录如图所示:

I.MX6U GPIO的命名

图中的形如“IOMUXC_SW_MUC_CTL_PAD_GPIO1_IO00”的就是 GPIO 命名,命名形式就是“IOMUXC_SW_MUC_CTL_PAD_XX_XX”,后面的“XX_XX”就是 GPIO 命名,比如:GPIO1_IO01、UART1_TX_DATA、JTAG_MOD、SNVS_TAMPER1 等等。I.MX6U 的GPIO并不像 STM32 一样以 PA0~15 这样命名,它是根据某个 IO 所拥有的功能来命名的。比如我们一看到 GPIO1_IO01 就知道这个肯定能做 GPIO,看到 UART1_TX_DATA 肯定就知道这个 IO肯定能做为 UART1 的发送引脚。官方参考手册中“Chapter 30: IOMUX Controller(IOMUXC)”这一章列出了I.MX6U 的 所 有 IO , 如 果 你 找 遍 第 30 章 的 书 签 , 你 会 发 现 貌 似 GPIO 只有 GPIO1_IO00~GPIO_IO09,难道 I.MX6U 的GPIO 只有这 10 个?显然不是的,我们知道 STM32的很多 IO 是可以复用为其它功能的,那么 I.MX6U 的其它 IO 也是可以复用为 GPIO 功能。同样的,GFPIO1_IO00~GPIO_IO09 也是可以复用为其它外设引脚的,接下来就是 I.MX6U IO 复用。

二、I.MX6U处理器GPIO的复用

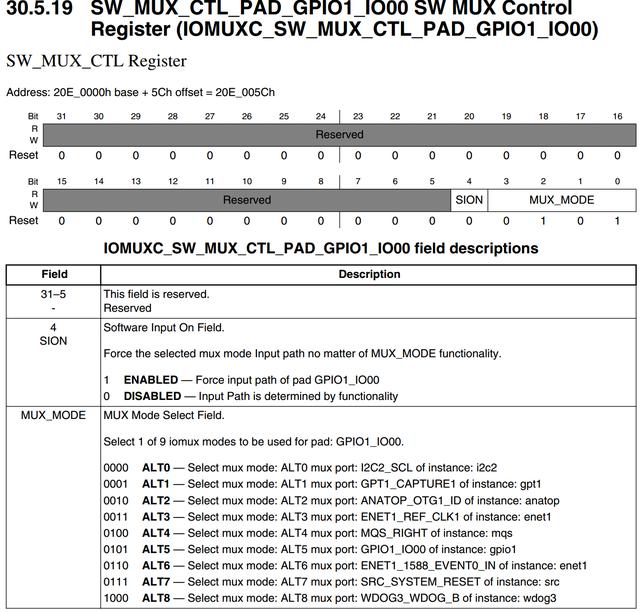

以 IO“IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO00”为例,打开参考手册的 1329 页,如图所示:

GPIO1_IO00 复用

从图中可以看到有个名为:IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO00 的寄存器,寄存器地址为 0X020E005C,这个寄存器是 32 位的,但是只用到了最低 5 位, 其中bit0~bit3(MUX_MODE)就是设置 GPIO1_IO00 的复用功能的。GPIO1_IO00 一共可以复用为 9种功能 IO,分别对应 ALT0~ALT8,其中 ALT5 就是作为 GPIO1_IO00。GPIO1_IO00 还可以作为 I2C2_SCL、GPT1_CAPTURE1、ANATOP_OTG1_ID 等。这个就是 I.MX6U 的 IO 复用,我们学习 STM32 的时候 STM32 的GPIO 也是可以复用的。

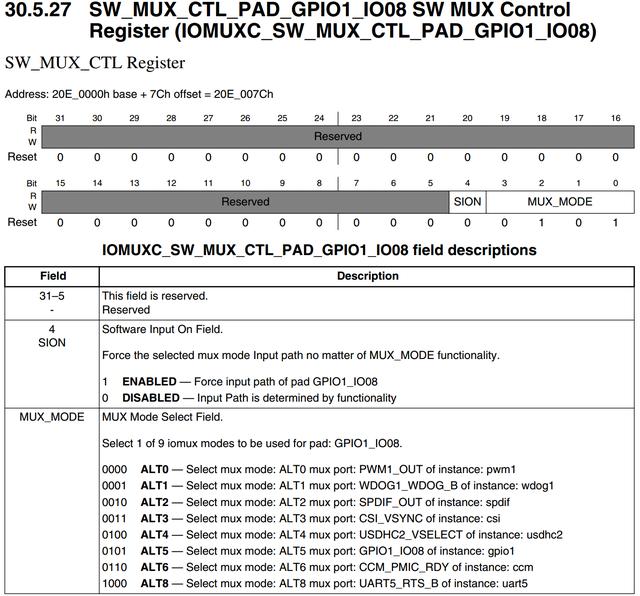

在来看一个“IOMUXC_SW_MUX_CTL_PAD_UART1_TX_DATA”这个 IO,这个 IO 对应的复用如图所示:

UART1_TX_DATA IO 复用

同样的,从图中可以看出,UART1_TX_DATA 可以复用为 7 种不同功能的 IO,分为ALT0~ALT5 和ALT8,其中 ALT5 表示 UART1_TX_DATA 可以复用为GPIO1_IO16。

由此可见,I.MX6U 的GPIO 不止 GPIO1_IO00~GPIO1_IO09 这 10 个,其它的 IO 都可以复用为GPIO 来使用。I.MX6U 的 GPIO 一共有 5 组:GPIO1、GPIO2、GPIO3、GPIO4 和 GPIO5,其中 GPIO1 有 32 个 IO,GPIO2 有 22 个 IO,GPIO3 有 29 个 IO、GPIO4 有 29 个 IO,GPIO5最少,只有 12 个 IO,这样一共有 124 个 GPIO。如果只想看每个 IO 能复用什么外设的话可以直接查阅《IMX6UL 参考手册》的第 4 章“Chapter 4 External Signals and Pin Multiplexing”。如果我们要编写代码,设置某个 IO 的复用功能的话就需要查阅第 30 章“Chapter 30: IOMUX Controller(IOMUXC)”,第 30 章详细的列出了所有 IO 对应的复用配置寄存器。

至此我们就解决了之前的第 3 个疑问,那就是 I.MX6U 的 IO 是有复用功能的,和 STM32一样,如果某个 IO 要作为某个外设引脚使用的话,是需要配置复用寄存器的。

三、I.MX6U处理器GPIO的IO配置

细心的读者应该会发现在《 I.MX6UL 参考手册》第 30 章“ Chapter 30: IOMUX Controller(IOMUXC)”的书签中,每一个 IO 会出现两次,它们的名字差别很小,不仔细看就看不出来,比如GPIO1_IO00 有如下两个书签:

IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO00

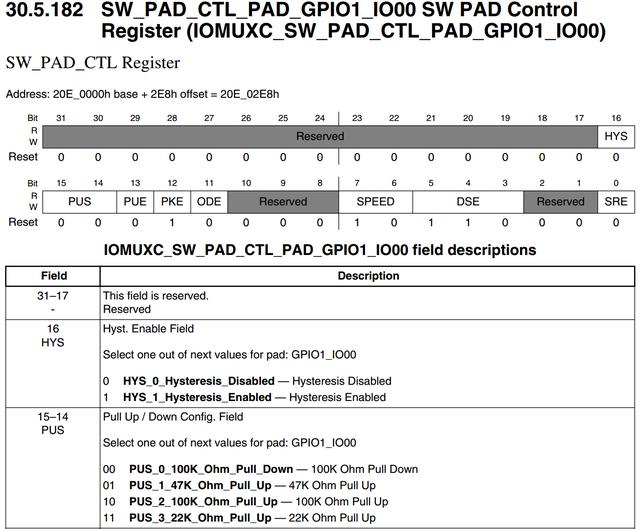

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00上面两个都是跟 GPIO_IO00 有关的寄存器,名字上的区别就是红 {MOD}部分,一个是“MUX”,一个是“PAD”。IOMUX_SW_MUX_CTL_PAD_GPIO1_IO00 我们前面已经说了,是用来配置GPIO1_IO00 复用功能的,那么 IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00 是做什么的呢?找到这个书签对应的 1582 页,如图所示:

IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00 寄存器

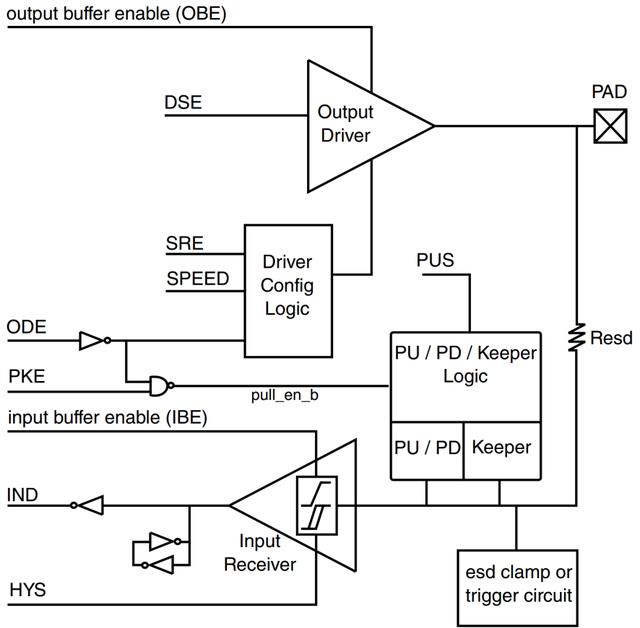

从图中可以看出,IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00 也是个寄存器,寄存器地址为 0X020E02E8。这也是个 32 位寄存器,但是只用到了其中的低 17 位,在看这写位的具体含义之前,先来看一下图中所示的 GPIO 功能图:

GPIO 功能图

我们对照着图中来详细看一下寄存器 IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO00 的各个位的含义:

HYS(bit16):对应图中 HYS,用来使能迟滞比较器,当 IO 作为输入功能的时候有效,用于设置输入接收器的施密特触发器是否使能。如果需要对输入波形进行整形的话可以使能此位。此位为 0 的时候禁止迟滞比较器,为 1 的时候使能迟滞比较器。

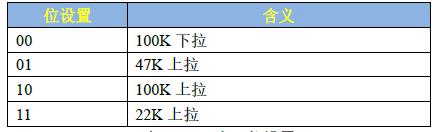

PUS(bit15:14):对应图中的 PUS,用来设置上下拉电阻的,一共有四种选项可以选择,如表所示:

上下拉设置

PUE(bit13):GPIO功能图中没有给出来,当 IO 作为输入的时候,这个位用来设置 IO 使用上下拉还是状态保持器。当为 0 的时候使用状态保持器,当为 1 的时候使用上下拉。状态保持器在IO 作为输入的时候才有用,故名思意,就是当外部电路断电以后此 IO 口可以保持住以前的状态。

PKE(bit12):对应GPIO功能图中的PKE,此为用来使能或者禁止上下拉/状态保持器功能,为0 时禁止上下拉/状态保持器,为 1 时使能上下拉和状态保持器。

ODE(bit11):对应GPIO功能图中的 ODE,当 IO 作为输出的时候,此位用来禁止或者使能开路输出,此位为 0 的时候禁止开路输出,当此位为 1 的时候就使能开路输出功能。

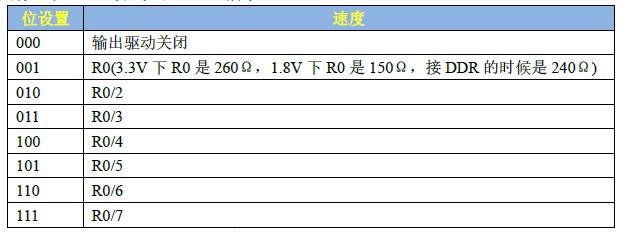

SPEED(bit7:6):对应GPIO功能图中的 SPEED,当 IO 用作输出的时候,此位用来设置 IO 速度,设置如表中 所示:

速度配置

DSE(bit5:3):对应图 8.1.4.2 中的 DSE,当 IO 用作输出的时候用来设置 IO 的驱动能力,总共有 8 个可选选项,如表所示:

驱动能力设置

SRE(bit0):对应GPIO功能图中的 SRE,设置压摆率,当此位为 0 的时候是低压摆率,当为 1的时候是高压摆率。这里的压摆率就是 IO 电平跳变所需要的时间,比如从 0 到 1 需要多少时间,时间越小波形就越陡,说明压摆率越高;反之,时间越多波形就越缓,压摆率就越低。如果你的产品要过 EMC 的话那就可以使用小的压摆率,因为波形缓和,如果你当前所使用的IO做高速通信的话就可以使用高压摆率。