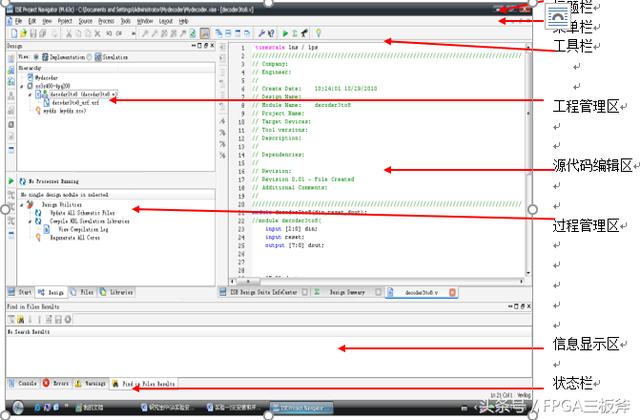

在计算机桌面上双击ISE图标,便可以启动ISE软件的运行。整个界面采用标准Windows格式,共分8个部分:标题栏、菜单栏、工具栏、工程管理栏、源代码文件编辑区、过程管理区、信息显示区和状态栏。

图1 ISE 工具界面

具体菜单栏中的各项的具体功能可以阅读相关资料。下面具体介绍利用ISE软件开发FPGA的整个过程。

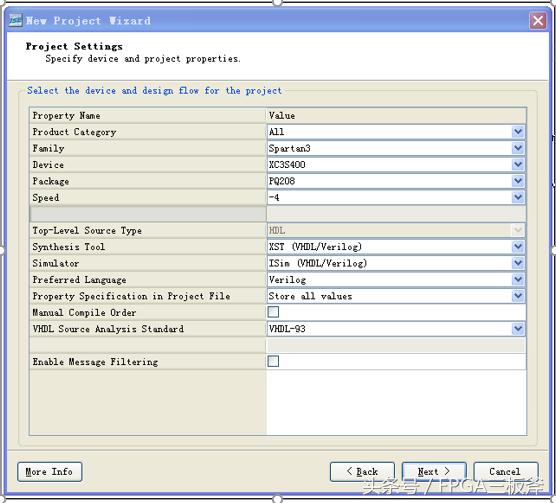

1、新工程建立

选择“File|New Projiect”选项,弹出新建工程的对话框,输入工程名,选择所存路径,至于顶层源文件类型默认为HDL,点击NEXT进入工程属性,选择器件类型、封装、速度、综合工具、仿真工具以及喜欢的硬件描述语言,详见下图设置。择好后点击OK进入下一页,可以选择新建源代码文件,也可直接跳过,进入下一页。如已有源代码文件,则可以添加到工程中;如没有,则单击“NEXT”进入最户一页,单击“OK”就建立一个完整的工程文件。

图2 新建工程

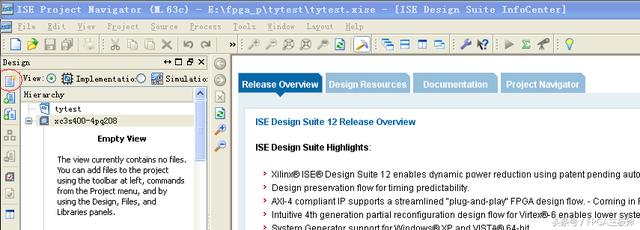

2、代码输入

1)在工程管理区点击鼠标右键,弹出菜单选择New Source,或者在Project栏目菜单中选择New Source,弹出界面;

图3 添加代码文件

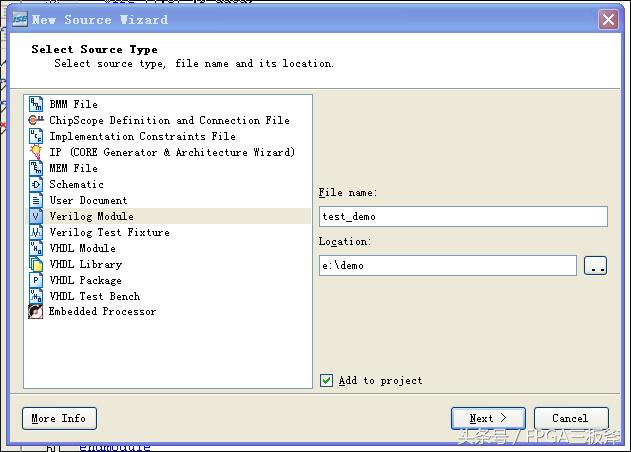

2)输入文件名,选择源码类型,这里选择Verilog Module,单击NEXT进入端口定义对话框;

图4 创建代码文件

3)输入端口名,选择端口的方向属性、总线以及MSB、LSB等,也可以在代码中进行声明。单击NEXT进入下一个界面;

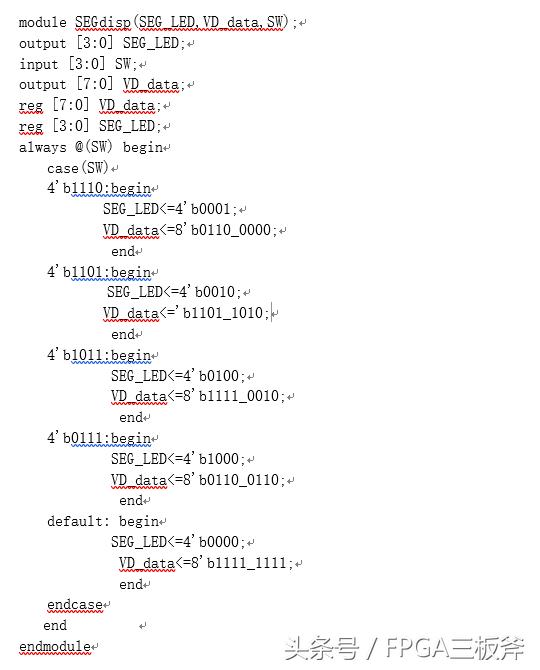

4)示例程序的verilog HDL程序:

图5 verilog 代码

5)单击“FINISH”,完成新源代码文件的建立。

当代码编辑完成后要存盘时,ISE12.2要检查代码的语法,如有错误,则存盘时在信息状态栏当中会给出出错信息。根据出错信息修改代码,直到没有语法错误为止。

3、进行仿真

ISE仿真有两种方法:一种是利用HDL Bencher的图形化波形编辑功能编写测试文件;另一种是利用HDL语言编写测试文件,这里介绍利用HDL语言来构建测试平台。

1)测试平台建立

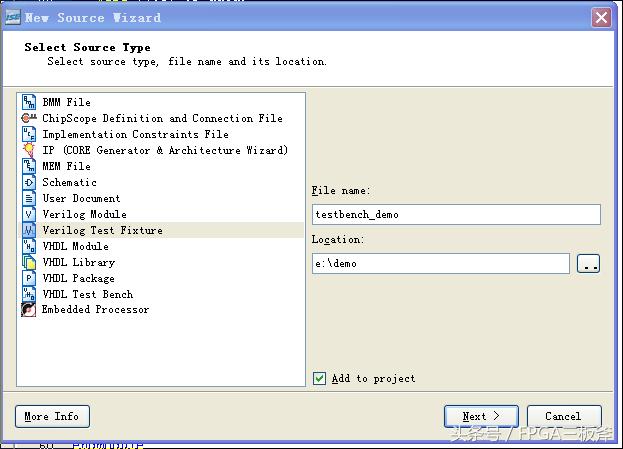

a)在工程管理区点击鼠标右键,弹出菜单选择New Source,弹出界面;

b)输入文件名,选择Verilog Test Fixture,打钩add to project,单击NEXT;

图6 创建仿真文件

c)选择要仿真的文件,点击NEXT;

d)点击“FINISH”,就生成一个Verilog测试模块。

ISE能自动生成测试平台的完整构架,包括所需信号、端口声明以及模块调用的实现。所需要完成的工作就是initial….end模块中的“//Add stimulus here”后面添加测试向量生成代码。

这里给出示例测试代码,将其添加于//Add stimulus here处

#100;

SW = 7;

#100;

SW = 11;

#100;

SW = 13;

#100;

SW = 14;

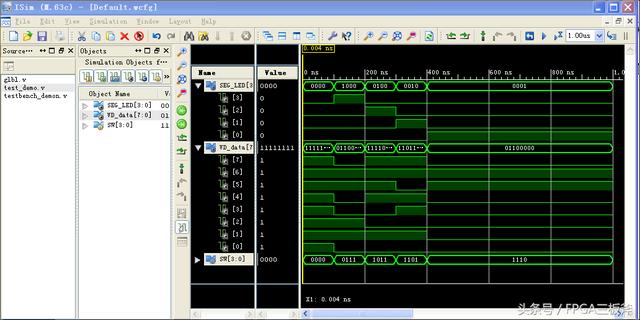

2)测试平台建立后,在工程管理区将状态设置为“Simulation”;选择要仿真的文件名,过程管理区就会显示“Isim simlator”;

3)下拉“Isim simlator”,选择“Simulate Behavioral Model”,单击鼠标右键,现在“Process Properties”可修改仿真远行时间等。

4)修改后,直接双击“Isim simlator”中的“Simulate Behavioral Model”进行仿真。检查仿真结果是否达到预期设计目标。

图7 工程仿真时序

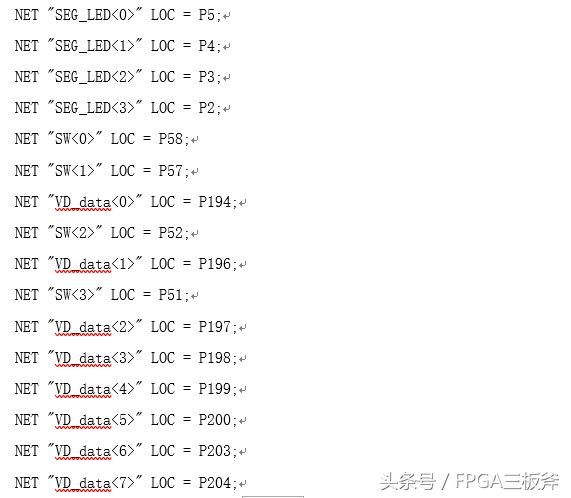

4、约束文件的编写

约束是FPGA开发中不可缺少的一部分。FPGA设计中有3类约束文件:用户设计文件(.UCF)、网表约束文件(.NCF)和物理约束文件(.PCF)。这里对我们开发FPGA过程常用的FPGA管脚约束文件进行描述。可以用文本编辑器和Xilinx约束文件编辑器进行编辑。

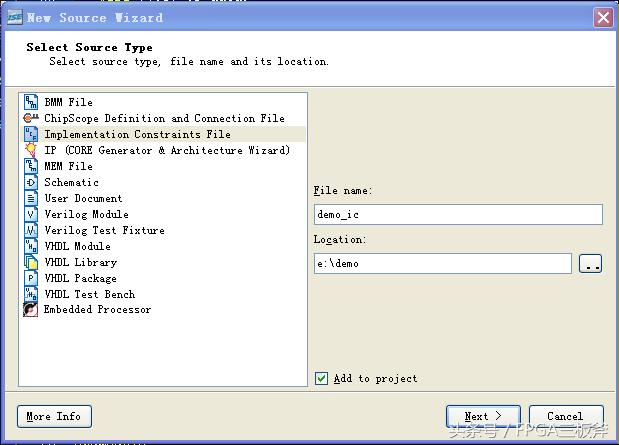

1)约束文件建立

a)在工程管理区点击鼠标右键,弹出菜单选择New Source,或者在Project栏目菜单中选择New Source,弹出界面;

图8 创建约束文件

b)输入文件名,选择Implemention Constraints File,点击NEXT;

c)如有多个文件,则选择相应文件,点击NEXT;

d)点击“FINISH”,完成约束文件的创建。

2)编辑约束文件

管脚约束文件的语法为:

NET “Signal_Port_Name” LOC=“Chip_Port”;

可用“#”或“/*……..*/”添加注释。需要注意的是UCF文件对字母的大小写敏感,信号名必须和设计中保持大小写一致。另外要搞清楚FPGA芯片管脚的编号方式,因不同类型的FPGA管脚编号可能是不同的,一旦选定了FPGA,知道其编号方式,就可在管脚约束文件引用。否则会出错的。

图9 管脚分配

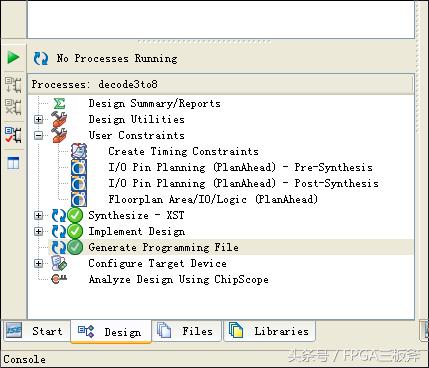

5、综合

完成了输入、仿真以及管脚分配后,就可以进行综合和实现。

选择要综合的文件,在过程管理区中双击“Synthesis-XST”可以完成综合操作,综合可能有3种结果:

图10 生成bit流文件

a)综合后完全正确,则在“Synthesis-XST”前面有一个打钩的绿 {MOD}小圆圈,且在信息显示区里显示process “Synthesis-XST”completed sucessfully。用鼠标右键点击“Synthesis-XST”选择“view Text Report”查看综合报告,了解FPGA资源使用情况等。

b)如有告警,则出现一个带感叹号的黄 {MOD}小圆圈,在信息显示区的“warning”中可以看到相关信息;

c)如有出错,则出现一个带叉的红 {MOD}小圆圈,在在信息显示区的“error”中可以看到相关的出错信息;

综合正确完成后,可以通过双击“View RTL Schematic”来查看RTL级构图,检查是否按照设计意图来实现电路。

另外需注意的,一般可使用XST属性的默认值来综合,但XST也提供丰富、灵活的属性配置,可鼠标用右键点击“Synthesis-XST”,选择“process properties”从三个方面来配置:synthesis option、HDL option 以及specific option,具体可参阅相关资料。

6、实现