本文主要讲述FPGA开发过程。

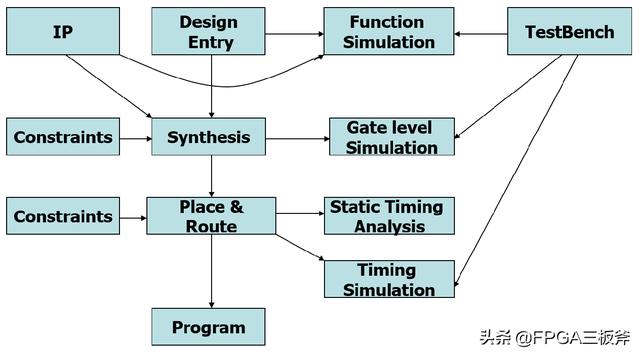

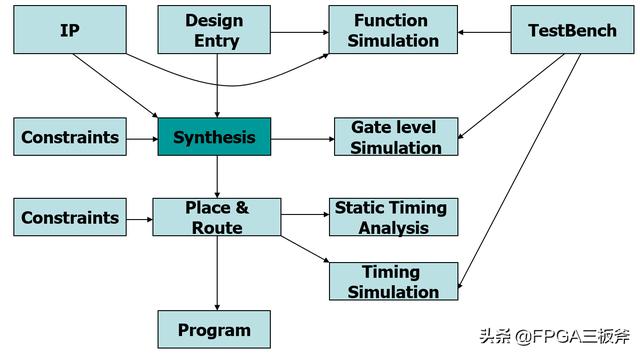

标准设计流程

一、Design

在系统设计之前,首先要进行的是方案论证、系统设计和 FPGA 芯片选择等准备工作。 系统工程师根据任务要求,如系统的指标和复杂度,对工作速度和芯片本 身的各种资源、 成本等方面进行权衡,选择合理的设计方案和合适的器件类型。一般都采用自顶向下的设 计方法,把系统分成若干个基本单元,然后再把每个基本单 元划分为下一层次的基本单 元,一直这样做下去,直到可以直接使用 EDA 元件库为止。

二、Design Entry

• 原理图输入

原理图输入

• CODE输入方式

代码的方式输入

• 网表输入方式

三、IP核

• 厂商工具产生的模块(Inter MagaWizard和Xilinx Core Generator)

• 公司购买的IP Core

• 公司自行开发的通用模块

• IP的形式可能是源代码,也可能是EDIF网表

xilinx IP

四、Function Simulation

• 功能仿真验证设计的正确性

• 功能仿真没有延时

• 使用专门的仿真工具,推荐modelsim

• Testbench用VHDL/Verolog HDL编写

• 功能仿真速度快,应在功能仿真阶段发现尽可能多的问题

• 功能仿真做得好,可以大大减少调试时间

五、TestBench

• TestBench用VHDL和Verilog HDL编写

• 利用HDL的语言机制,可以产生非常丰富的测试激励,对设计进行尽可能全面的验证

testbech

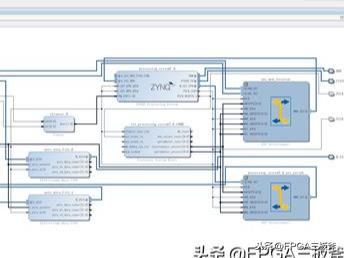

六、系统级仿真

• 把Testbench描述成虚拟PCB

• 在虚拟PCB上放置虚拟元件,包括我们的设计和外围元件

• 从器件商获得器件的功能仿真模型(VHDL / Verilog HDL)

• 如果没有模型可用,就需要作行为建模,可以是功能很简单的模型

• 系统级仿真就是用虚拟逻辑分析仪观察虚拟PCB上的波形

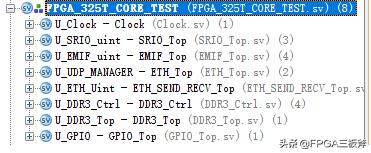

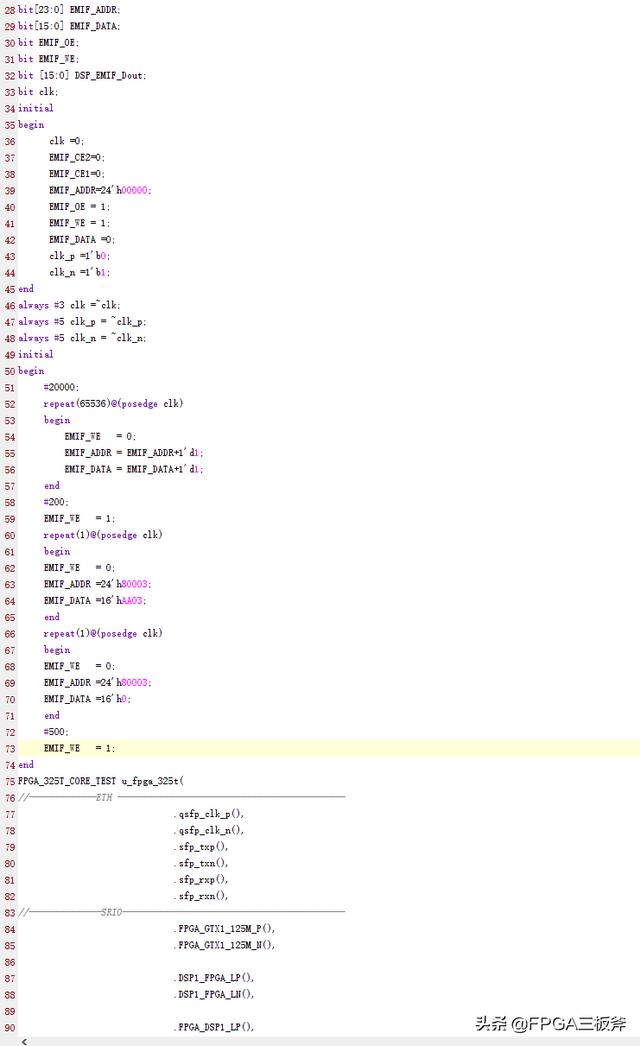

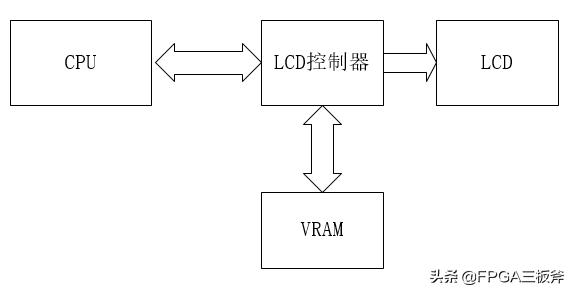

七、系统级仿真的例子

•从供应商获得VRAM的模型

•对EMIF的总线接口进行行为建模

•编写Testbench,描述虚拟PCB

•只需要给出CPU的访问序列,不需要关心VRAM的响应时序

•可以进行大数据量仿真

八、仿真工具

• FPGA厂商提供的开发工具仿真功能很弱,只提供波形输入,属于入门级

• PC平台上的仿真工具:

1)、Active HDL (Aldec)

2)、ModelSim (Mentor Graphics)推荐

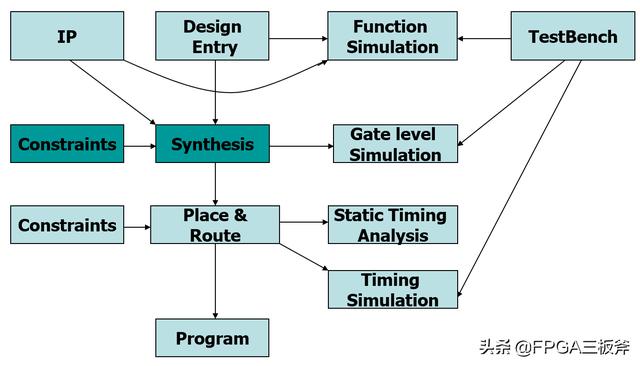

九、Synthesis

综合

• 综合将行为级描述转化成门级描述

• FPGA厂商提供的开发工具综合效果都不太好,属于入门级

• 综合应在第三方工具上完成

• PC平台上常用的综合工具:Leonardo Spectrum(Mentor Graphics)、Syplify Pro(Syplicity)推荐

十、Constraints(Synthesis)

• 综合阶段的约束通常只有时间约束

• 综合阶段的约束条件并不是必须满足,在布局布线阶段会对设计进一步优化

• 综合阶段的约束将传递到布局布线阶段

十一、综合的输出

• EDIF网表,供布局布线用

• VHDL/Verilog网表,供门级仿真用

• 约束文件,传递给布局布线工具

十二、Gate level Simulation

• 门级仿真验证综合结果与设计的一致性

• 门级仿真没有延时,即使源文件中加入了延时

• 门级仿真使用功能仿真相同的TestBench

• 门级仿真的结果必须与功能仿真一致

十三、门级仿真的必要性

• 门级仿真并不是必要的

• 综合将忽略敏感表,当敏感表中的信号没有包括进程中用到的所有右值时,门级仿真将给出与功能仿真不同的结果

• 使用第三方综合工具后对生成的门级网表

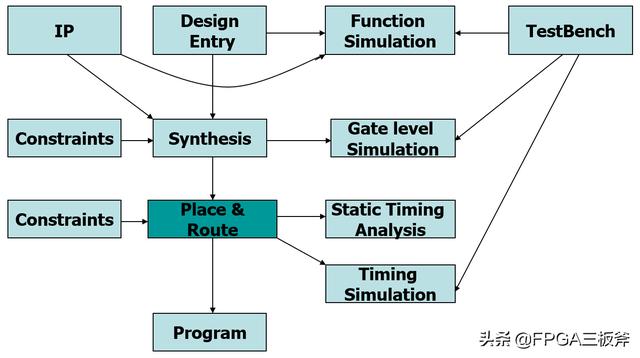

十四、Place & Route

布局布线

• P&R的输入是综合产生的EDIF网表

• P&R将门级网表转化成FPGA配置代码

• P&R在厂商开发工具中进行

十五、Constraints(P&R)

• P&R阶段的约束包括时间约束和位置约束

• 时间约束有这样几种:

1)、tpd: pin-to-pin delay,只用于组合逻辑

2)、tsu:setup time,用于输入

3)、tco:clock-to-out delay,用于输出

4)、fmax:内部最高工作频率

5)、Cut timing path:用于低速路径

• 位置约束包括:

1)、引脚位置

2)、内部逻辑单元位置

十六、Static Timing Analysis