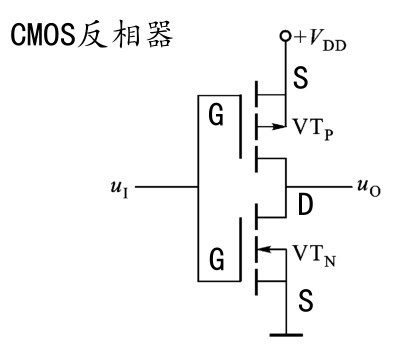

VTp PMOS导通条件:Vgs(th)P<0

VTn NMOS导通条件:Vgs(th)N>0

当UI=0, Ugs(N)=0,N管截止,Ugs(P)<0,P管导通,所以Uo=VDD,输出高电平

VTp PMOS导通条件:Vgs(th)P<0

VTn NMOS导通条件:Vgs(th)N>0

当UI=0, Ugs(N)=0,N管截止,Ugs(P)<0,P管导通,所以Uo=VDD,输出高电平当UI=VDD,Ugs(N)>0,N管导通,Ugs(P)=0,P管截止,所以Uo=0,输出低电平 即UI=/UO,反相器逻辑符号如下:

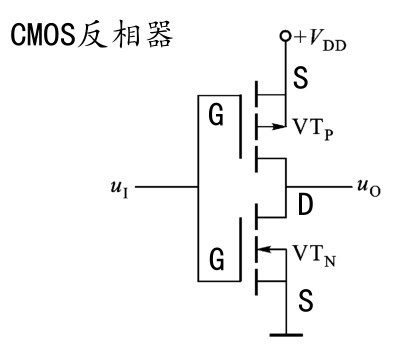

VTp PMOS导通条件:Vgs(th)P<0

VTn NMOS导通条件:Vgs(th)N>0

当UI=0, Ugs(N)=0,N管截止,Ugs(P)<0,P管导通,所以Uo=VDD,输出高电平

VTp PMOS导通条件:Vgs(th)P<0

VTn NMOS导通条件:Vgs(th)N>0

当UI=0, Ugs(N)=0,N管截止,Ugs(P)<0,P管导通,所以Uo=VDD,输出高电平