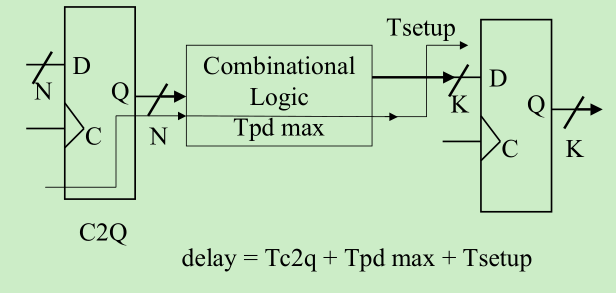

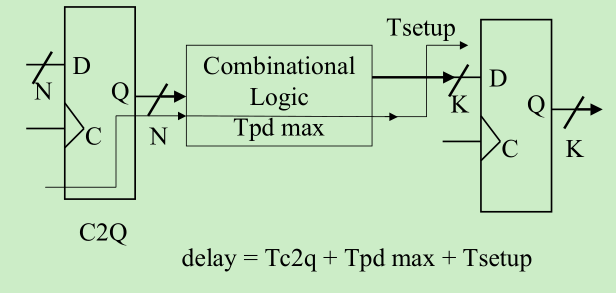

这篇文章接上篇文章继续讲一下时序系统中时序分析,如下图为一个时序系统的典型结构:

那么该系统的最大运行频率是多少呢?计算公式如下: Fre_max=1/longest delay path 因此要计算系统的最大运行频率,就需要找出系统总的最长路径。而最长路径处于下面这三条路径当中: 1.Clock to Output delay: Tc2q + Tcomb_Q2Omax,其中Tcomb_Q2O指的是Q输出到任何输出的最长路径。 2.Register to Register delay:Tc2q + Tcomb_Q2D max + Tsetup,其中 Tcomb_Q2D max 指的是DFF的Q输出到DFF的D输入的最长路径。 3.Pin to Pin combination delay:Tcomb_I2O max,指的就是输入到输出的最长的路径,中间没有任何DFF的干扰。 一般情况下,时序系统的输入输出都会打进寄存器中,即如下图所示的结构:

这种情况Thold 需要满足下面的式子: Tc2q + Tpd min >=Thold,一般情况下在时序电路中是很容易满足这个等式的。 下面可以看一个简单的例子:切换频率的计算,如下图所示:

上面说到的都是对于内部DFF的分析,下面说一下对于外部输入如何计算setup时间和hold时间,这个是有区别与内部DFF的setup时间和hold时间的。 外部输入会通过一个pad驱动器缓冲,经过组合逻辑然后到达同步的输入端D,如下图所示:

这种情况下对于输入DIN来说最坏的情况就是CLK 先与DIN到达同步输入端,因此其setup时间为: Din setup =Tsu + TpdDin max - Tpdclk min,这里的Tpd如下图中的虚线框图所示:

而这种情况下对于hold 时间来讲,最坏的情况就是数据Din先到同步输入端,而时钟clk后到达同步输入端,因此hold时间的计算方法如下: Din hold= Thd + Tpdclk max - TpdDin min. 以上就是时序系统相关时间的计算方法,大家可以找一些题目巩固一下理解。

那么该系统的最大运行频率是多少呢?计算公式如下: Fre_max=1/longest delay path 因此要计算系统的最大运行频率,就需要找出系统总的最长路径。而最长路径处于下面这三条路径当中: 1.Clock to Output delay: Tc2q + Tcomb_Q2Omax,其中Tcomb_Q2O指的是Q输出到任何输出的最长路径。 2.Register to Register delay:Tc2q + Tcomb_Q2D max + Tsetup,其中 Tcomb_Q2D max 指的是DFF的Q输出到DFF的D输入的最长路径。 3.Pin to Pin combination delay:Tcomb_I2O max,指的就是输入到输出的最长的路径,中间没有任何DFF的干扰。 一般情况下,时序系统的输入输出都会打进寄存器中,即如下图所示的结构:

这种情况Thold 需要满足下面的式子: Tc2q + Tpd min >=Thold,一般情况下在时序电路中是很容易满足这个等式的。 下面可以看一个简单的例子:切换频率的计算,如下图所示:

上面说到的都是对于内部DFF的分析,下面说一下对于外部输入如何计算setup时间和hold时间,这个是有区别与内部DFF的setup时间和hold时间的。 外部输入会通过一个pad驱动器缓冲,经过组合逻辑然后到达同步的输入端D,如下图所示:

这种情况下对于输入DIN来说最坏的情况就是CLK 先与DIN到达同步输入端,因此其setup时间为: Din setup =Tsu + TpdDin max - Tpdclk min,这里的Tpd如下图中的虚线框图所示:

而这种情况下对于hold 时间来讲,最坏的情况就是数据Din先到同步输入端,而时钟clk后到达同步输入端,因此hold时间的计算方法如下: Din hold= Thd + Tpdclk max - TpdDin min. 以上就是时序系统相关时间的计算方法,大家可以找一些题目巩固一下理解。