门电路

常见的门电路有:与门,或门,非门,异或门,与非门,或非门。今天,我们就来说说这些门电路是如何实现的,并用它来实现一个加法器。

非门(NOT)

- 逻辑符号 & 布尔表达式 & 真值表

请务必记住其逻辑框图符合,再后面做加法器时我们要用其来表示!!! - 实现

我们先用继电器实现一下

`

`

输入端输入1时,电磁铁会把金属弹簧片吸下来,从而灯泡电路断开,灯泡不发光,即输出0 输入端输入0时,电磁铁会把金属弹簧片维持原来的位置,从而灯泡电路连接,灯泡发光即输出1

这就实现了一个非门:输入1,输出0;输入0,输出1.

我们再用晶体管实现一下

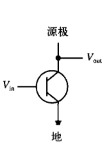

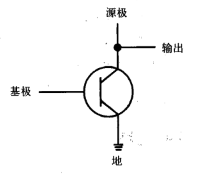

在分析这个电路之前,我们先看看这个晶体管的线路:

在计算机电路中,源极是一个高电压,发射极接地,基极通常做输入端,它决定了是否将源极接地:

当基极为高电压(1)时:晶体管闭合->源极接地->输出端为低电压(0)

当基极为低电压(0)时:晶体管打开->源极不接地->输出端为高电压(1)

经过上面的分析,你应该已经知道晶体管非门电路实现的原理了吧,那么对上面那幅图就不做再多的阐述了。

与门(NOT)

- 逻辑符号 & 布尔表达式 & 真值表

- 实现

我们先用继电器实现一下

可以看出,只有当两个开关都闭合时,灯泡才亮,很明显,这是一个与门电路。

两个继电器串联可以组成一个与门 我们再用晶体管实现一下

相信这个电路大家都看得懂,不再做过多的阐述或门(OR)

- 逻辑符号 & 布尔表达式 & 真值表

- 实现

我们先用继电器实现一下

可以看出,只有任意一个开关闭合,灯泡就亮,很明显,这是一个或门电路。

两个继电器并联可以组成一个或门 我们再用晶体管实现一下

这里就不画了,等到后面介绍或非门时,你可以在或非门输出端加上一个非门,从而组成或门。

与非门(NAND)

- 逻辑符号 & 布尔表达式 & 真值表

- 实现

我们先用继电器实现一下

我们可以看到:只要有一个开端断开,则灯泡就亮,这符合与非门:有0则1

我们再用晶体管实现一下

V1,V2只要有一个为低电平,那么源极将不会接地,则输出端为高电平

或非门(XOR)

- 逻辑符号 & 布尔表达式 & 真值表

- 实现

我们先用继电器实现一下

我们可以看到:只要有一个开端闭合,则灯泡将不亮,这符合与或门:有1则0

我们再用晶体管实现一下

V1,V2有一个微高电平时,源极将接地,输出端为低电平。

异或门(XOR)

- 逻辑符号 & 布尔表达式 & 真值表

注意到:异或门的真值表,刚好符合我们二进制的加法运算,1+1 = 01,0是本位输出位,1则是进位,后面我们将用异或门来做加法器 - 实现

由于异或门的实现需要用到或门和与非门和与门,要想用继电器来描述则有点难画,所以我们用逻辑框图符合来描述异或门:

我们来看看每一步的真值表:

显然,输入和输出完全符合我们之前的定义的异或门。下面,我们要用其来做加法器。经过上面的分析,我们已经掌握了6种逻辑门:

非门:将唯一的输入值求逆

与门:属于都为1时,输出才为1

或门:属于有一个为1时,就为1

与非门:结果与非门的相反

或非门:结果与或门的相反

异或门:两个输入皆相同时,就输出0

以上几种门电路的特征务必记住,下面我们就要开始真正地做加法器了,让我们看看计算机内部是如何进行加法运算的

加法器

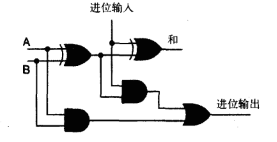

半加器

所谓半加器,就是计算两个位数的和并产生进位的电路,不考虑进位。我们来分析分析,

- 在本位加输出中,若两个输入数相同则是0,不同则是1,所以我们可以用异或门

来实现 - 在进位输出中,若输入的两个数都是1,才输出1,所以我们可以用与门来实现。

那么我们的半加器就做出来了:

为了简单,我们也可以采用以下表示:

全加器

在实际中,因为涉及到多位数的运算,所以不得不考虑进位,那么半加器就不能满足我们的需求了,所以我们要做一个全加器所谓全加器,就是对二进制执行加法运算的电路,考虑进位

我们来分析分析,

我们再组合一下,把表达变得更简单:

八位加法器

要实现八位加法器,当然就要八个全加器,只不过第一个全加器的进位输入值我们设为0就好啦。

这就是八位加法器,进位输入我们设置为0,然后A,B就是我要进行加法运算的8bits的二进制数啦。

按照这种思路,我们也可以设计出16位,32位的加法器。

circuits

下面我们用circuits在线电路设计和仿真工具实现各种电路。请点击这里进入circuits.io任务一:非门实现

在circuits中,并没有提供“NOT GATE”,我们可以用三极管来实现。

任务二:验证电路等价

在此实验中,我们将设计两个电路:A(B+C),AB+AC,并验证他们等价这是A(B+C)

这是AB+AC

我们枚举所有可能,结果如下

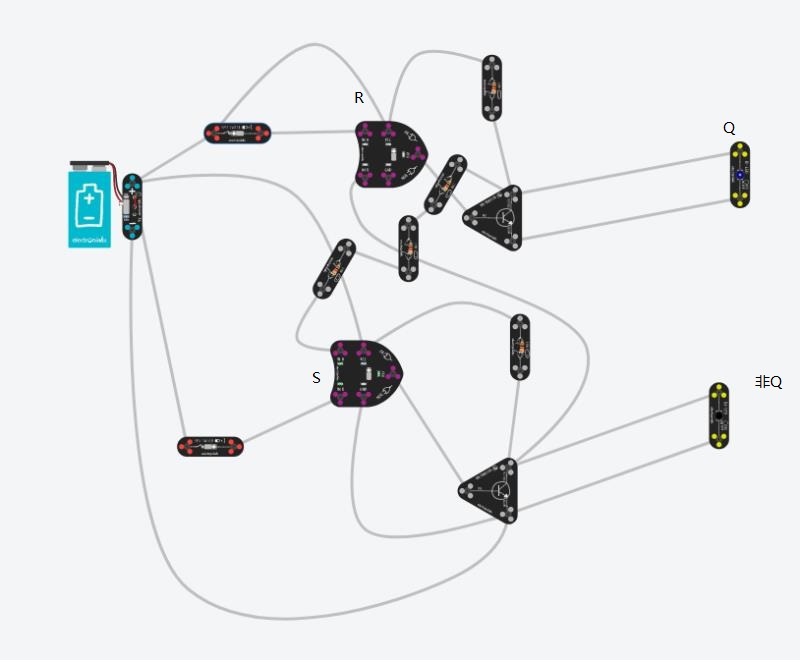

任务三:理解存储电路

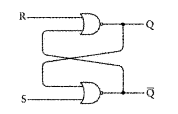

在本实验中,我们将搭建一个S-R锁存器,在进行实验之前,我们先来了解一下S-R锁存器的知识。S-R锁存器是触发器中的一种。它的功能就是保存数据,结构如下:

它的真值表如下:

我们做出一些说明,方便理解该触发器:

- 我们规定:S和R端不能同时置为1,这是我们禁止的,所以在使用S-R锁存器时,千万别放这种低级错误;

- Q端的输出即我们想要保留的东西,就是说你想保存1,那Q端就该输出1,想保存0,Q端就该输出0;

- S端我们用来置位和复位,置为你可以理解为把Q端输出置为1,复位你可以理解为把Q端输出置为0;

- Q和非Q端的输出肯定是相反的,这也是我们为什么把一端称为Q端,而另一端称为非Q端的原因;

- 我们对真值表第三行做一些说明,它的意思是:当S,R端皆为0时,它的输出将保持不变。也就是说:

- 如果上次为SR端分别为:10,Q非Q端输出分别为10,那么将S重新置为0时,R端维持0不变,那么Q非Q端输出仍然为10;

- 如果上次为SR端分别为:01,Q非Q端输出分别为01,那么将R重新置为0时,S端维持0不变,那么Q非Q端输出仍然为01;

下面我们就开始做实验啦!!!

任务四:设计加法电路

这网页有毒,巨耗内存。。。。全加器我实在画不下去了,每次画到一半必定卡死。。。所以我建议老师在找不到替代网站,还是手画此题吧。。。一位全加器,我画了一半,剩下一半用笔补了一下。。原理上面已经分析了。。。相信大家能够理解。。。

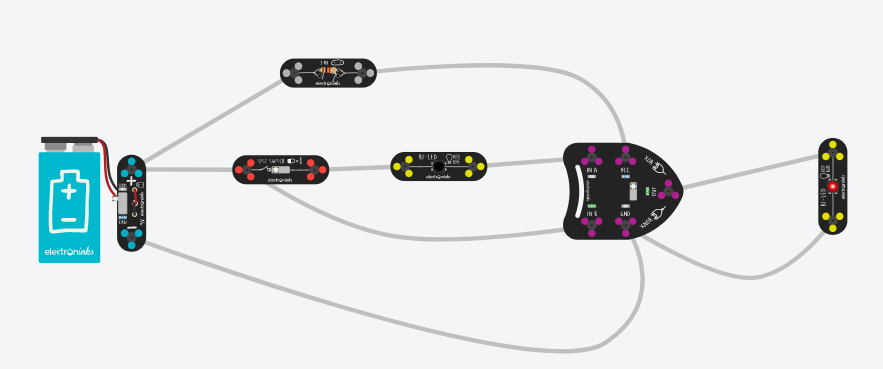

至于2位全加器,在我的垃圾电脑上是无法画出来的。。所以我截了别人的图。上面都分析了八位加法器的实现,相信这个二位就不用说了。请看偷来的图。。。

至于2位全加器,在我的垃圾电脑上是无法画出来的。。所以我截了别人的图。上面都分析了八位加法器的实现,相信这个二位就不用说了。请看偷来的图。。。

在此声明一点:以上图片中你可以看到很多地方用了电阻。之所以这样子,因为这个网站电路连线不能交叉,所以只能用电阻把它隔开。