1.点击file-new project wizard新建工程,工程名字为“lab3”,然后next-next,选择cyclone旗下的EP1C2Q24C8芯片,点击next,在simulation一栏,工具名选用“ModelSim-Altera”,类型选择“Verilog-HDL”,再点击finish完成工程的创建。

2.点击file-new新建verilog HDL file,输入程序代码,已“eighteencout”的名字保存,如图所示:

然后右键“eighteen.v”,选择“create symbol files for current file”为工程创建符号。

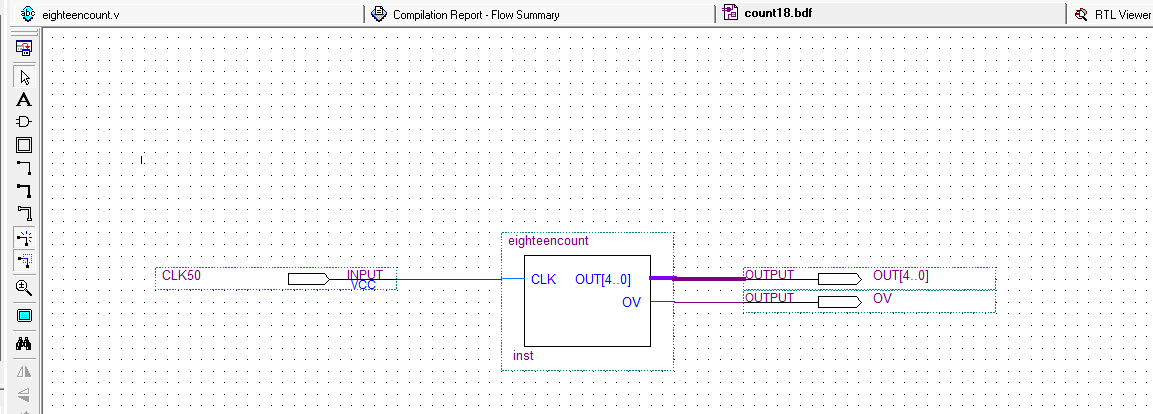

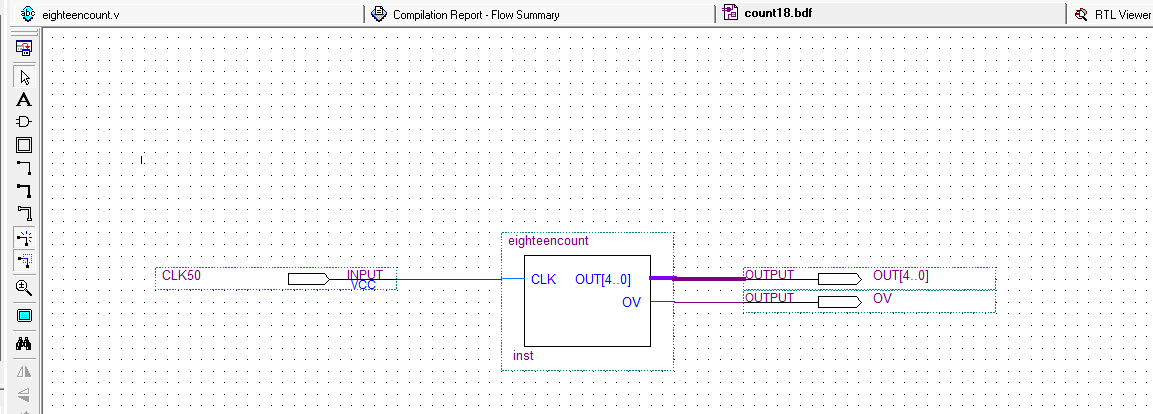

3.点击file-new新建bdf文件,选择器件连接,并以“count18.bdf”的名字保存,如图:

4.将已准备好的文本文档(pin引脚文件)通过assignments-import assignments导入到工程中,并点击assignments-pins查看引脚分布,如图所示:

此时可以查看RTL如图:

5.然后点击project-set as top.level entity将其设置为顶层文件,再点击processing-start进行编译,编译结果如图示:

6.点击file-new新建vector waveform file,点击view-utility windows-node finder进行关键引脚的仿真输入设计,在filter选项中选择singertap ii:pre-synthesis,并点击右侧的list,再将所需节点拖至仿真区域。点击edit-end time设置仿真时间,点击每一个输入信号的Bar进行输入信号的周期设置,并将文件保存。如图:

8. 打开assignments->settings->simulator settings

看里面的有个文本框 simulation input 里面是否为空,为空的话就要找到你所建立的Vector Waveform File 文件,是以*.VMF结尾的,如果没找到,你又以为你建立了Vector Waveform File ,很可能粗心的你还没保存Vector Waveform File ,保存了才会在project里面找到。

然后就可以点击processing-start simulation进行仿真了,如图所示:

2.点击file-new新建verilog HDL file,输入程序代码,已“eighteencout”的名字保存,如图所示:

然后右键“eighteen.v”,选择“create symbol files for current file”为工程创建符号。

3.点击file-new新建bdf文件,选择器件连接,并以“count18.bdf”的名字保存,如图:

4.将已准备好的文本文档(pin引脚文件)通过assignments-import assignments导入到工程中,并点击assignments-pins查看引脚分布,如图所示:

此时可以查看RTL如图:

5.然后点击project-set as top.level entity将其设置为顶层文件,再点击processing-start进行编译,编译结果如图示:

6.点击file-new新建vector waveform file,点击view-utility windows-node finder进行关键引脚的仿真输入设计,在filter选项中选择singertap ii:pre-synthesis,并点击右侧的list,再将所需节点拖至仿真区域。点击edit-end time设置仿真时间,点击每一个输入信号的Bar进行输入信号的周期设置,并将文件保存。如图:

8. 打开assignments->settings->simulator settings

看里面的有个文本框 simulation input 里面是否为空,为空的话就要找到你所建立的Vector Waveform File 文件,是以*.VMF结尾的,如果没找到,你又以为你建立了Vector Waveform File ,很可能粗心的你还没保存Vector Waveform File ,保存了才会在project里面找到。

然后就可以点击processing-start simulation进行仿真了,如图所示: