目录

前言

原理

Verilog HDL程序设计

测试代码

仿真波形图

ISE综合后

RTL Schematic

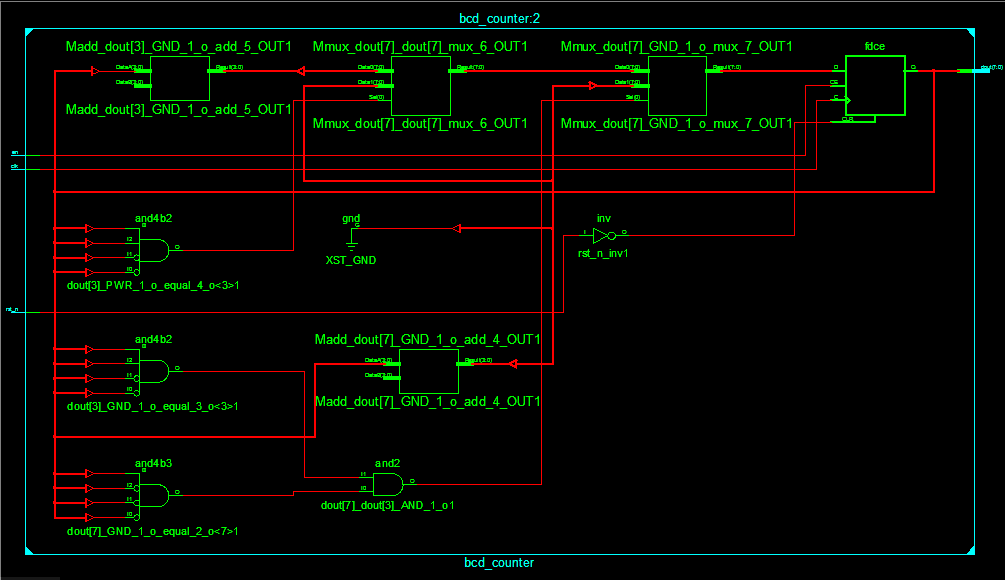

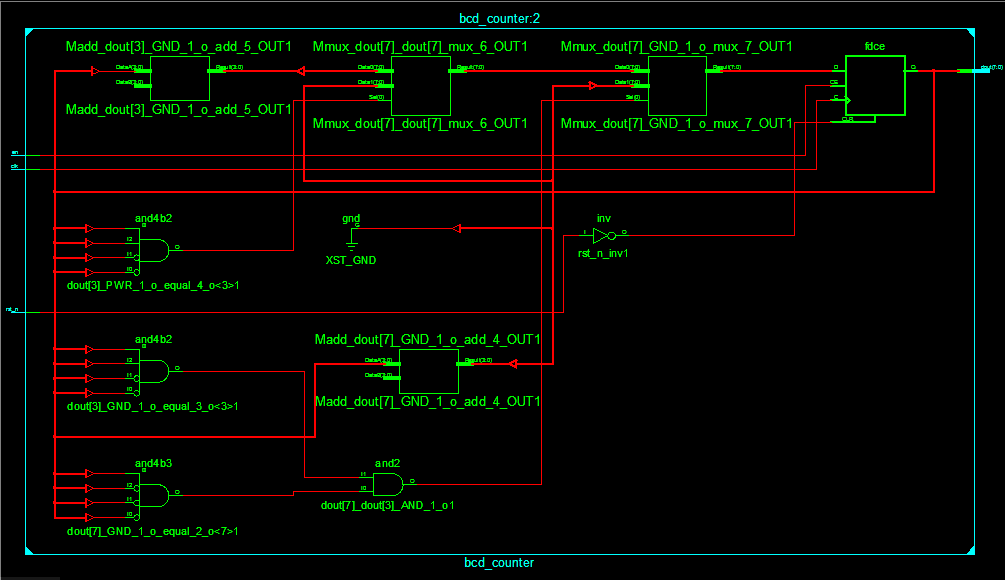

Technology Schematic

可见,计数到23后计数器就自动清零了,满足设计要求。

可见,计数到23后计数器就自动清零了,满足设计要求。

展开后

展开后

没办法,再放大就看不全了,需要看仔细的,自己用ISE综合一下就好了。

没办法,再放大就看不全了,需要看仔细的,自己用ISE综合一下就好了。

用了一些LUT资源和D触发器资源以及各种BUF资源。

最后附上同一系列的博文:

模6计数器以及模10计数器(Verilog HDL语言设计)(Modelsim仿真与ISE综合)

级联模60计数器

用了一些LUT资源和D触发器资源以及各种BUF资源。

最后附上同一系列的博文:

模6计数器以及模10计数器(Verilog HDL语言设计)(Modelsim仿真与ISE综合)

级联模60计数器

前言

本博文用Verilog HDL语言描述模24的8421BCD码计数器,之后用Modelsim进行功能仿真,然后用ISE进行综合,看看综合出来的RTL级电路以及Technology Schematic是什么样子的,对于RTL Schematic 以及 Technology Schematic可能比较复杂,暂时可能看不懂,但混个眼熟吧。重点是设计思路以及波形图是否正确,后面例如设计一个时钟计数器,这个模24的计数器就可以当成一个模块来直接使用。本博文的目的实际上也是为了时钟计数器做准备,后面的博文会用到这个模块。原理

计数原理很简单,rst_n为异步复位信号,当时钟上升沿或复位下降沿到来时,如果rst_n有效,则计数器清零(0000 0000)。计数器的计数过程为,当输出信号的低4位从0(0000)计数到9(1001)后,高4位计数加1,当计数到23(0010 0011)时,计数器重新清零,然后重新开始计数。Verilog HDL程序设计

//8421BCD码计数器,模24

module bcd_counter(clk, rst_n, en, dout);

input clk, rst_n, en;

output[7:0] dout;

reg[7:0] dout;

always@(posedge clk or negedge rst_n) //异步复位

begin

if(!rst_n) //复位信号有效时,输出清零

dout <= 8'b00000000;

else if(en == 1'b0) //计数使能无效时,输出不变

dout <= dout;

else if( (dout[7:4] == 4'b0010)&&(dout[3:0] == 4'b0011) ) //计数达到23时,输出清零

dout <= 8'b00000000;

else if(dout[3:0] == 4'b1001) //低位达到9时,低位清零,高位加1

begin

dout[3:0] <= 4'b0000;

dout[7:4] <= dout[7:4] + 1'b1;

end

else //上述情况都没有发生,则高位不变,低位加1

begin

dout[7:4] <= dout[7:4];

dout[3:0] <= dout[3:0] + 1'b1;

end

end

endmodule

测试代码

//模24,8421BCD码计数器的测试文件

`timescale 1ns/1ps

module bcd_counter_tb;

reg clk, rst_n, en;

wire[7:0] dout;

//时钟信号,周期为20ns

always

begin

#10 clk = ~clk;

end

//初始化

initial

begin

clk = 1'b0;

rst_n = 1'b0;

en = 1'b0;

#30 rst_n = 1'b1; en = 1'b1;

end

bcd_counter u1(.clk(clk), .rst_n(rst_n), .en(en), .dout(dout));

endmodule

仿真波形图

可见,计数到23后计数器就自动清零了,满足设计要求。

可见,计数到23后计数器就自动清零了,满足设计要求。

ISE综合后

RTL Schematic

展开后

展开后

没办法,再放大就看不全了,需要看仔细的,自己用ISE综合一下就好了。

没办法,再放大就看不全了,需要看仔细的,自己用ISE综合一下就好了。

Technology Schematic

用了一些LUT资源和D触发器资源以及各种BUF资源。

最后附上同一系列的博文:

模6计数器以及模10计数器(Verilog HDL语言设计)(Modelsim仿真与ISE综合)

级联模60计数器

用了一些LUT资源和D触发器资源以及各种BUF资源。

最后附上同一系列的博文:

模6计数器以及模10计数器(Verilog HDL语言设计)(Modelsim仿真与ISE综合)

级联模60计数器