class="markdown_views prism-atom-one-light">

结合下图我们可以看出:

下图是74161芯片的内部结构图,从图中可以看到,161芯片内部主要包括一个4比特计数器和一个并行置数电路, 另外还有2个逻辑门用于工作使能和进位控制。

下图是74161芯片的内部结构图,从图中可以看到,161芯片内部主要包括一个4比特计数器和一个并行置数电路, 另外还有2个逻辑门用于工作使能和进位控制。

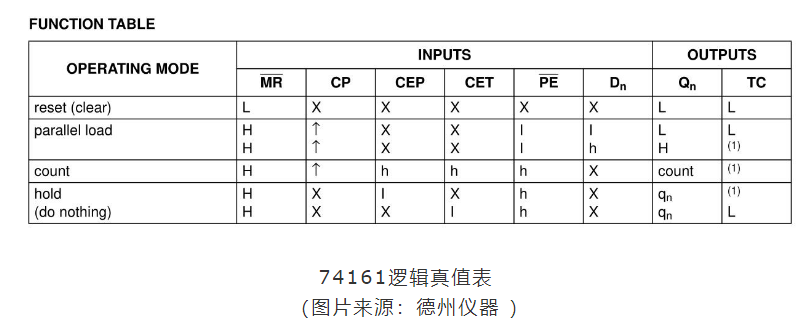

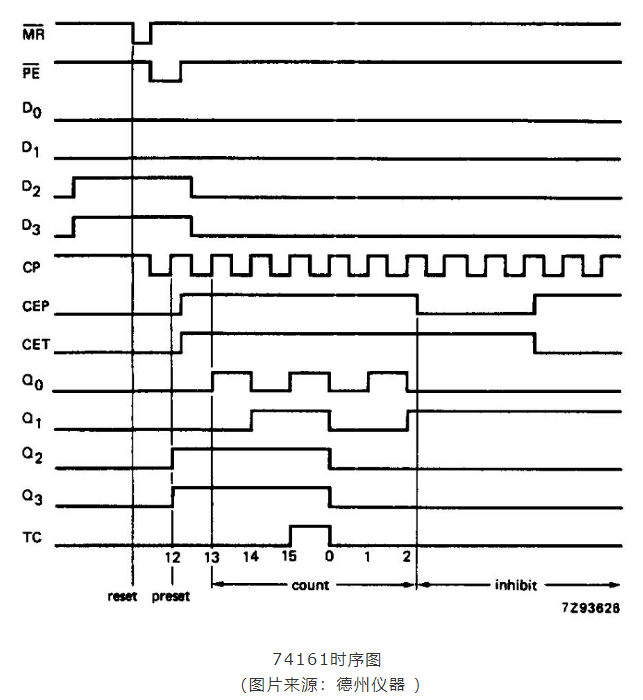

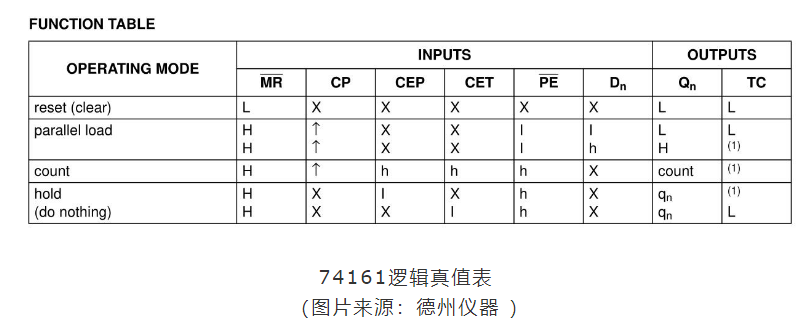

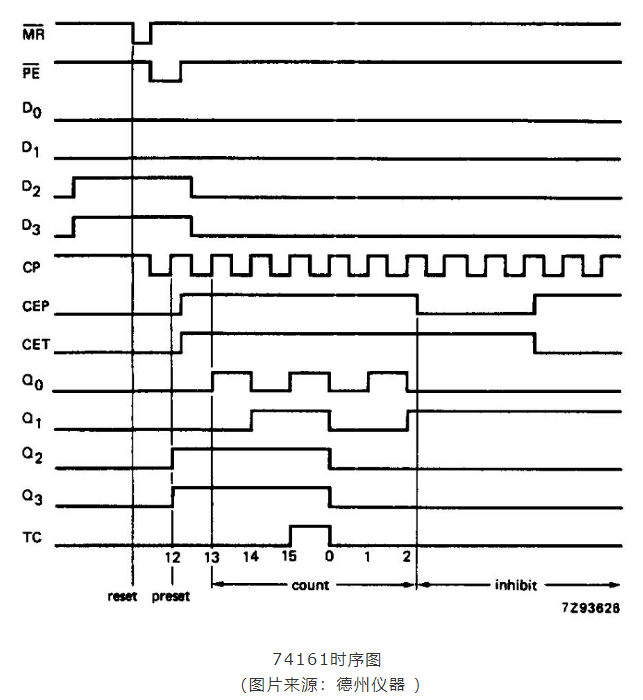

74LS161芯片的工作逻辑真值表和工作时序如下图所示

电路逻辑设计如下:

用QuartusⅡ进行功能性仿真后得:

用QuartusⅡ进行时序性仿真后得:

可见,时序仿真对信号的响应有一定的延迟。

设两个芯片的八个输出位分别为QH,QG,QF,QE,QD,QC,QB,QA(从高位到低位)计数周期为00000000到00010011(0到19),通过观察发现只有在一个周期结束的时候才会出现QA,QB,QE同时为1的情况,故可利用这一特性,让3个信号相与非(得0)接到两个161芯片的LND端,实现两个计数器的复位。

电路逻辑设计如下:

用QuartusⅡ进行功能性仿真后得:

用QuartusⅡ进行时序性仿真后得:

一.74LS161芯片基本功能介绍

74LS161就是一颗用来实现带置位功能的4比特16进制计数芯片。下图是74161芯片的相关信息。结合下图我们可以看出:

- TC为进位输出端,TC=Q0,Q1,Q2,Q3,CET相与,即只有在CET为1,且计数状态为1111时,TC才为高,并产生进位信号。

- CP为计数脉冲输入端,上升沿有效。

- MR为异步清0端,低电平有效,只要MR=0,就有Q0,Q1,Q2,Q3为0,与CP信号无关。

- PE为同步预置端,低电平有效,当MR=1,PE=0,在CP上升沿到来的时候,才能将数据输入端D1D2D3D4的数据置入并在输出端输出,即Q1Q2Q3Q4=D1D2D3D4

- CET,CEP为计数器允许控制端,高电平有效,只有当MR和PE为1,CET,CEP也为1时,计数器才开始工作。

- 当MR和PE为1,且CET,CEP中有一个为低电平时,计数器处于保持状态。

下图是74161芯片的内部结构图,从图中可以看到,161芯片内部主要包括一个4比特计数器和一个并行置数电路, 另外还有2个逻辑门用于工作使能和进位控制。

下图是74161芯片的内部结构图,从图中可以看到,161芯片内部主要包括一个4比特计数器和一个并行置数电路, 另外还有2个逻辑门用于工作使能和进位控制。

74LS161芯片的工作逻辑真值表和工作时序如下图所示

二.利用74LS161计数器芯片实现模12的计数器

设计要求:

- 用161计数器芯片,设计一个M=12的计数器

- 上电后,对CLK信号,从0顺序计数到11,然后回绕到0

- 当计数值为11的CLK周期,溢出信号OV输出一个高电平,其他周期OV信号输出0

- 用波形仿真观察电路结果

设计思路:

要实现模12的计数器,及从0到11,现在QD为高位,及从0000到1011,然后复位,再从0000开始循环计数。因为在一个计数周期中,QA,QB,QD都为1的时候只有在1011的时候才会出现,故利用这个特点,使QA,QB,QD相与非得到0,并把这个信号输入到LDN端,使计数器置位回到0000的初始状态,并且OV端会输出高电平,表示一个计时周期的结束。电路逻辑设计如下:

用QuartusⅡ进行功能性仿真后得:

用QuartusⅡ进行时序性仿真后得:

可见,时序仿真对信号的响应有一定的延迟。

三.利用74LS161计数器芯片实现模20的计数器

设计要求:

- 用161计数器芯片,设计一个M=20的计数器, 可以用多片

- 上电后,对CLK信号,从0顺序计数到19,然后回绕到0

- 当计数值为19的CLK周期,溢出信号OV输出一个高电平,其他周期OV信号输出0

- 用波形仿真观察电路结果

设计思路:

因为一片161最大只能实现模16的计数功能,故要用两片161芯片级联来实现这个功能,那么首先要解决的问题是如何使两个161芯片协同工作呢,即要使第一片计数从0到15,然后再激活第二个芯片开始工作,这里把低位片的溢出端RCO,接到高位片的LND端,而使ENT端常为1,这样当低位片一个周期计数结束之后,RCO产生高电平,会使高位片开始工作,即高位片输出0001,但是下一个脉冲到来的时候,RCO就会变为低电平,此时高位片进入保持状态,保持0001的状态,直到00010011,然后复位开始下一个周期的循环。那么如何复位呢?设两个芯片的八个输出位分别为QH,QG,QF,QE,QD,QC,QB,QA(从高位到低位)计数周期为00000000到00010011(0到19),通过观察发现只有在一个周期结束的时候才会出现QA,QB,QE同时为1的情况,故可利用这一特性,让3个信号相与非(得0)接到两个161芯片的LND端,实现两个计数器的复位。

电路逻辑设计如下:

用QuartusⅡ进行功能性仿真后得:

用QuartusⅡ进行时序性仿真后得: