用MATLAB/SIMULINK实现半加器、全加器的组合数字逻辑电路设计及仿真

一、实验目的:

1.学会用电子仿真软件 MATLAB7(SIMULINK) 设计半加器及全加器数字逻辑电路2.掌握半加器、全加器的工作原理。

3.学会用Scope(示波器)观察半加器,全加器的输入及输出波形

4.掌握simulink组合电路的分析和设计方法

5.验证半加器和全加器的逻辑功能(真值表)

二、实验准备

:根据分析所给的逻辑组合电路, 写出其输入与输出之间的逻辑关系(逻辑函数表达式或真值表),从而评定该电路的逻辑功能的方法。一般是首先对给定的逻辑电路,按逻辑门的连接方法,逐一写出相应的逻辑表达式,然后写出输出函数表达式,这样写出的逻辑函数表达式可能不是最简的,所以还应该利用逻辑代数的公式或者卡诺图进行简化。 再根据逻辑函数表达式写出它的真值表,最后根据真值表分析出函数的逻辑功能。三、实验实施

- 构建一个半加器

打开MATLAB 7,在matlab7的 command windows窗口中输入simulink启动Simulink,或按下工具栏中 图标,直接启动simulink。

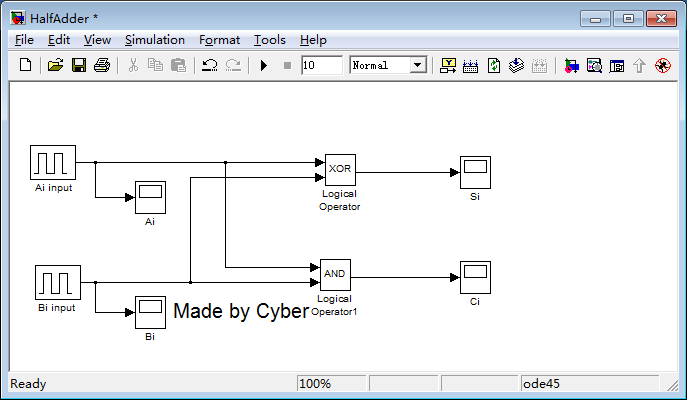

启动SIMULINK以后,打开Simulink library browser中文件(File)菜单中新建(New)一个模型文件(model),文件名为HalfAdder.mdl, 参考下图完成半加器电路。此文件需要使用导三个库中的模块:Logical and Bit Operations,sources和sinks。先从逻辑门开始。

在simulink library browser中,双击Logic and Bit Operations。将Logical Operator模块拖到工作窗口中,双击模块打开Block Parameters窗口,将Main标签中的Operator选项改为XOR。再拖入一个AND门。

接下来是输入信号。选用Pulse Generator以便检查是否得到了想要的输出。打开Sources面板,拖入两个Pulse Generator并放置再窗口的左侧。

这两个Pulse Generator作为加法器真值表的两个输入。双击第一个Pulse Generator并将它的周期(period)设定为8秒,相位延迟(phase delay)设定为4秒。将这个Pulse Generator重命名为Ai input,作为输入的最小标志位(least-significant bit)。双击第二个Pulse Generator,将周期设定为4秒,相位设定为2秒,重命名为Bi input。选择edit菜单,选择copy model to clipboard选项,将电路图复制粘贴如下图:

按照上图的方式将输入和两个逻辑门连接起来。

将两个Scope连接到Pulse Generator可以检查其输出波形是否是你想要的。打开Sinks面板,拖入两个Scope放到Pulse Generator的旁边,并将两者连接好。双击Scope就可以打开输出波形的窗口。选择Simulation菜单下Start来运行模型(或按下 按钮),可以看到x和y的信号波形。注意输入向量(Bi Ai)在最初的两秒内的数值是00,然后是01,10,11这是加法器真值表的四个数值。现在来检查输出是否是真值表的数值。将Scope与XOR门和AND连接起来,运行仿真(CTRL加T键),分别双击Bi ,Ai,Si,Ci图标,观察输出波形是否和预料一致。注意记得时常保存文件。将电路图及二个输入,二个输出信号输出图复制粘贴在下图(如下图所示):

1.通过分析波形图,完成下列半加器的真值表

Ai Bi S i Ci

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

半加器中Si的逻辑表达式为: Si=Ai⊕Bi (注:⊕为异或符号)

半加器中Ci的逻辑表达式为: Ci= AiBi - 构建一个全加器

打开MATLAB 7,在matlab7的 command windows窗口中输入simulink启动Simulink,或按下工具栏中 图标,直接启动。

启动SIMULINK以后,打开Simulink library browser 中文件(File)菜单中新建(New)一个模型文件(model),文件名为FullAdder.mdl,保存好此文件,以备以后的多位先行加法器(n位)设计要用到,用来创建子系统。 参考下图的加全器逻辑电路图。此文件需要使用导三个库中的模块:Logical and Bit Operations,sources和sinks。先从逻辑门开始。

参考下图,放置好全加器的各种逻辑门器件及连接好连接线,选输入信号。选用Pulse Generator。打开Sources面板,拖入三个Pulse Generator并放置在窗口的左侧。这三个Pulse Generator作为加法器真值表的三个输入。双击第一个Pulse Generator并将它的周期(period)设定为16秒,相位延迟(phase delay)设定为8秒。你可以将这个Pulse Generator重命名为Ai input,作为输入的最小标志位(least-significant bit)。双击第二个Pulse Generator,将周期设定为8秒,相位设定为4秒,重命名为Bi input, 双击第三个Pulse Generator,将周期设定为4秒,相位设定为2秒,重命名为Ci-1 input。选择simulation菜单 ,选择configurations parameters 菜单,将simulation time中 stop time改为20, 并将各线连接好。双击Scope就可以打开输出波形的窗口。选择Simulation菜单下Start来运行模型(或按下 按钮),可以看到x和y的信号波形。注意三个输入向量(Ai,Bi,Ci-1)在最初的2秒内的数值是000,然后是001,010,011,100,101,110,111。这是全加法器真值表的八个数值。现在来检查输出是否是真值表的数值。运行仿真(CTRL加T键),分别双击Ai,Bi,Ci-1,Si,Ci图标,观察输出波形是否和预料一致。注意记得时常保存文件(按下CTRL加S键)。选择edit菜单下copy model to clipboard选项,将电路图及三个输入,二个输出信号输出图复制粘贴在下图(如下图所示):

- 通过分析波形图,完成下列全加器的真值表

Ai Bi Ci-1 Si Ci

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

全加器中Ci的逻辑表达式为: Ci=AiBi+(Ai⊕Bi)Ci-1

四、实验目标检验

自查:对照所学理论知识,总结半加器及全加器中Si,Ci以及CLA的逻辑表达式,并与运行结果对比。参考书目

- 计算机组成原理教师用书 蒋本珊 清华大学出版社

- 计算机组成原理 (第三版)蒋本珊 清华大学出版社

- 计算机组成原理 (第二版)唐朔飞 高等教育出版社

- 电子计算机组成原理(第三版)蒋本珊 北京理工大学出版社

- 计算机组成原理 (第四版)白中英 北京邮电大学大学出版社.

- 数字电子技术基础(数字部分) 康华光 高等教育出版社