版权声明

作者:young cc

链接:https://www.zhihu.com/question/35128735/answer/61319380

来源:知乎

电路为什么要有触发器这种结构?为什么要用时钟同步起来呢?一个乘法器如果不设计成触发的会是什么状态?最近在想电路同步异步的时候想到这个问题,现在还是大二,感觉知识不够无法从宏观角度理解

题主,这是个很好的问题,因为触发器(flip flop)是数字电路很重要的基础,会了这个才能设计大规模电路,我来认真回答下,另补上了流水线的知识

------------------------------------------------------------------------------------------------------------------------

先简短回答问题:用触发器是因为触发器能保存数据,保存电路状态;触发器是在时钟边沿触发,用时钟同步是让整个电路能同步整齐划一的工作;乘法器的计算部分是组合逻辑,不需要触发器,计算后的结果可以用触发器保存起来。

接下来详细解释。

电路系统中是有两种电路,一种是组合逻辑(Combinational Logic),其输出只是当前输入的函数,与之前状态无关,无存储功能;另一种是时序逻辑(Sequential Logic ),能够存储数据供以后使用,如触发器,memory,寄存器(register,由多个触发器组成)。

举个例子,如果你要做累加,计算

<img src="https://pic4.zhimg.com/dee80e3a970579719fc4f1f83e48a59f_b.png" data-rawwidth="606" data-rawheight="426" class="origin_image zh-lightbox-thumb" width="606" data-original="https://pic4.zhimg.com/dee80e3a970579719fc4f1f83e48a59f_r.png">

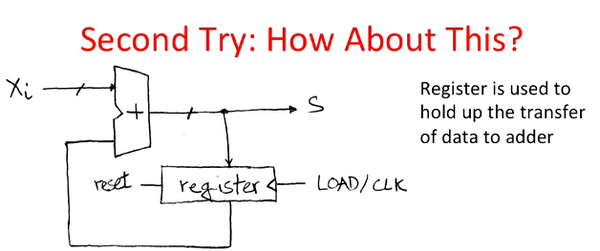

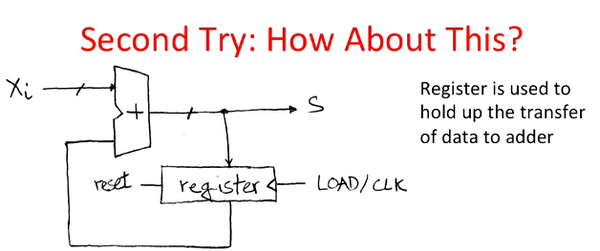

所以就需要触发器存储中间值,结构如下:

<img src="https://pic1.zhimg.com/f7e843401d439febb21d637eddd9b18c_b.png" data-rawwidth="628" data-rawheight="263" class="origin_image zh-lightbox-thumb" width="628" data-original="https://pic1.zhimg.com/f7e843401d439febb21d637eddd9b18c_r.png">

所以在实际的电路系统中,是由时序逻辑与组合逻辑共同组成。时序逻辑储存中间值,可分割组合逻辑,让每个组合逻辑变成一小块。流水线就是这样,能提高时钟频率,增加系统吞吐量,让每个模块的利用率达到最大。如下图所示:

<img src="https://pic2.zhimg.com/0fbb0d77d7501f95e9d7359500e3f7e5_b.png" data-rawwidth="611" data-rawheight="464" class="origin_image zh-lightbox-thumb" width="611" data-original="https://pic2.zhimg.com/0fbb0d77d7501f95e9d7359500e3f7e5_r.png">

设计触发器时,需要注意触发器的几个时间特性,满足这些特性触发器才能正常工作:

建立时间(T setup time):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。

保持时间(T hold):是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。

数据输出延时(Tco, Clock-to-Output Delay):当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

注意只有建立时间(T setup time)与 数据输出延时(Tco, Clock-to-Output Delay)是在critical path上,是电路delay,如下图:

<img src="https://pic1.zhimg.com/d9fcd81afb98b97ccbb75758903c8270_b.png" data-rawwidth="813" data-rawheight="588" class="origin_image zh-lightbox-thumb" width="813" data-original="https://pic1.zhimg.com/d9fcd81afb98b97ccbb75758903c8270_r.png">

最后说下,触发器的内容一定要认真理解,这个是整个数字电路的基础。

你说到了同步异步,那我说下异步电路吧。异步电路不需要时钟,低功耗,速度快,但需要用大量握手信号来同步电路,设计起来很复杂,目前还是非主流,至少十年内时序同步电路仍会是主流。

-----------------------------------------------流水线分割------------------------------------------------------

PS.有小伙伴说最好扩充下流水线(pipeline)知识,那我补充下吧

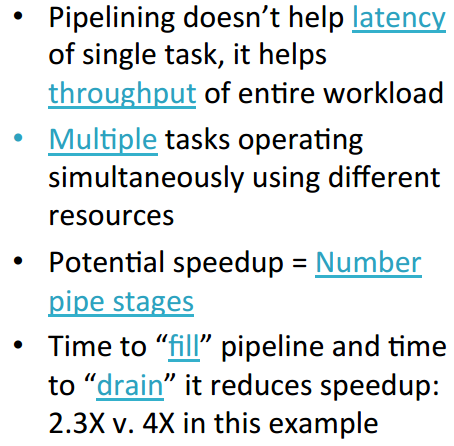

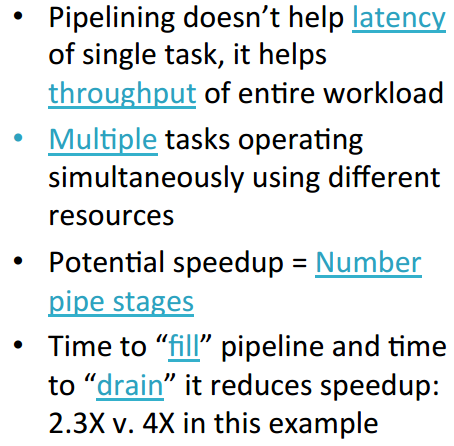

pipeline是将组合逻辑进行分割,能让任务以类似并行方式处理,提高系统频率,提高吞吐量(throughput).

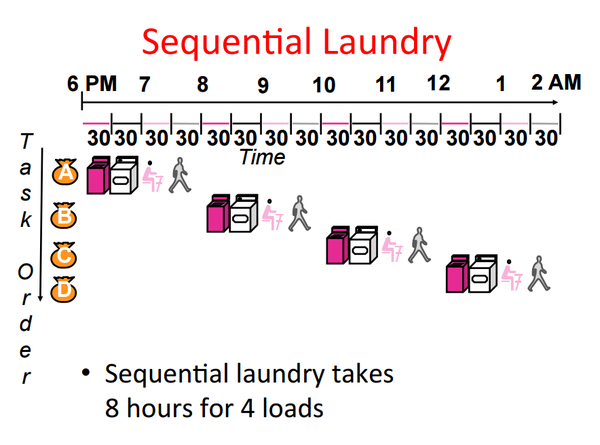

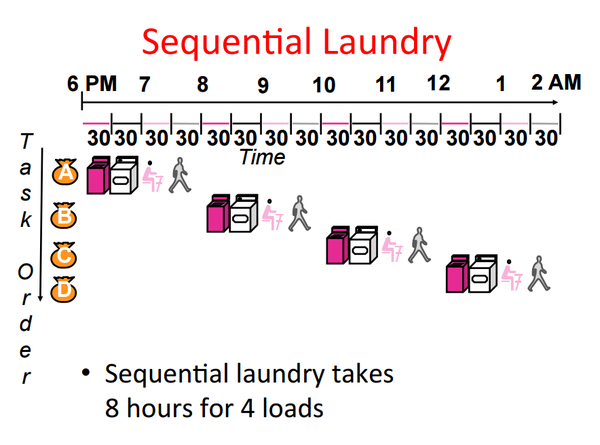

举个例子,假设洗衣分为四个步骤,分别在四个设备上进行,其中漂洗机器,烘干机器,在衣架上折叠衣服,把衣服放进柜子里各用30分钟,全过程需两小时。现有四个人去洗衣服,若sequential处理,一个人完成全步骤别人才开始,每人两小时,四个人共用八小时。如下图:

<img src="https://pic2.zhimg.com/390bc39fba2beed3db663a19673af545_b.png" data-rawwidth="884" data-rawheight="655" class="origin_image zh-lightbox-thumb" width="884" data-original="https://pic2.zhimg.com/390bc39fba2beed3db663a19673af545_r.png">但如果利用pipeline式的流水处理,当某人完成某步骤,其所用的设备就空闲了,后面的人就开始使用,四个人洗衣服只用3.5小时就能完成。如下图: 但如果利用pipeline式的流水处理,当某人完成某步骤,其所用的设备就空闲了,后面的人就开始使用,四个人洗衣服只用3.5小时就能完成。如下图:

但如果利用pipeline式的流水处理,当某人完成某步骤,其所用的设备就空闲了,后面的人就开始使用,四个人洗衣服只用3.5小时就能完成。如下图:

<img src="https://pic4.zhimg.com/55192854ed0b8c60f021eea8daa7a26b_b.png" data-rawwidth="899" data-rawheight="658" class="origin_image zh-lightbox-thumb" width="899" data-original="https://pic4.zhimg.com/55192854ed0b8c60f021eea8daa7a26b_r.png">

注意,pipeline只是提高系统的吞吐量,不能改善单个任务的latency。在实际电路中是在组合逻辑中插入register,分割组合逻辑,实现pipeline,而register读写也需要时间,所以单个任务的执行时间反而会增长。另外在分割组合逻辑时,使分割后的每段处理时间尽量相同,因为系统时钟是由最慢的那段决定的。如下图:

<img src="https://pic3.zhimg.com/125587503227702e20f6763df965a62e_b.png" data-rawwidth="454" data-rawheight="446" class="origin_image zh-lightbox-thumb" width="454" data-original="https://pic3.zhimg.com/125587503227702e20f6763df965a62e_r.png">

总结:

<img src="https://pic3.zhimg.com/44b1695d296c1b292a37923023d99762_b.png" data-rawwidth="847" data-rawheight="593" class="origin_image zh-lightbox-thumb" width="847" data-original="https://pic3.zhimg.com/44b1695d296c1b292a37923023d99762_r.png">

一个经典的五级流水线处理器如下图:

<img src="https://pic3.zhimg.com/1e3667161c3307d95cf5d863dbe435fe_b.png" data-rawwidth="915" data-rawheight="654" class="origin_image zh-lightbox-thumb" width="915" data-original="https://pic3.zhimg.com/1e3667161c3307d95cf5d863dbe435fe_r.png">

------------------------------------------------------------------------------------------------------------------------

PS. 得到大家这么多赞,那补上另一个关于流水线中会出现的hazards的成因与解决方法的回答是否有既用到 状态机 又用到 流水线 的module? - young cc 的回答

http://www-inst.eecs.berkeley.edu/~cs61c/sp15/lec/09/2015Sp-CS61C-L09-kavs-SDS-1up.pdf

http://www-inst.eecs.berkeley.edu/~cs61c/sp15/lec/13/2015Sp-CS61C-L13-kavs-Pipelining-1up.pdf

链接:https://www.zhihu.com/question/35128735/answer/61319380

来源:知乎

电路为什么要有触发器这种结构?为什么要用时钟同步起来呢?一个乘法器如果不设计成触发的会是什么状态?最近在想电路同步异步的时候想到这个问题,现在还是大二,感觉知识不够无法从宏观角度理解

题主,这是个很好的问题,因为触发器(flip flop)是数字电路很重要的基础,会了这个才能设计大规模电路,我来认真回答下,另补上了流水线的知识

------------------------------------------------------------------------------------------------------------------------

先简短回答问题:用触发器是因为触发器能保存数据,保存电路状态;触发器是在时钟边沿触发,用时钟同步是让整个电路能同步整齐划一的工作;乘法器的计算部分是组合逻辑,不需要触发器,计算后的结果可以用触发器保存起来。

接下来详细解释。

电路系统中是有两种电路,一种是组合逻辑(Combinational Logic),其输出只是当前输入的函数,与之前状态无关,无存储功能;另一种是时序逻辑(Sequential Logic ),能够存储数据供以后使用,如触发器,memory,寄存器(register,由多个触发器组成)。

举个例子,如果你要做累加,计算

s=0;

for (i=0;i<n;i++)

s = s+X{i} ;

如果不用触发器,只用组合逻辑,设计为下图。但可以看到这个设计有问题,无法实现结果,因为无法存储中间值,无法控制状态转换。<img src="https://pic4.zhimg.com/dee80e3a970579719fc4f1f83e48a59f_b.png" data-rawwidth="606" data-rawheight="426" class="origin_image zh-lightbox-thumb" width="606" data-original="https://pic4.zhimg.com/dee80e3a970579719fc4f1f83e48a59f_r.png">

所以就需要触发器存储中间值,结构如下:

<img src="https://pic1.zhimg.com/f7e843401d439febb21d637eddd9b18c_b.png" data-rawwidth="628" data-rawheight="263" class="origin_image zh-lightbox-thumb" width="628" data-original="https://pic1.zhimg.com/f7e843401d439febb21d637eddd9b18c_r.png">

所以在实际的电路系统中,是由时序逻辑与组合逻辑共同组成。时序逻辑储存中间值,可分割组合逻辑,让每个组合逻辑变成一小块。流水线就是这样,能提高时钟频率,增加系统吞吐量,让每个模块的利用率达到最大。如下图所示:

<img src="https://pic2.zhimg.com/0fbb0d77d7501f95e9d7359500e3f7e5_b.png" data-rawwidth="611" data-rawheight="464" class="origin_image zh-lightbox-thumb" width="611" data-original="https://pic2.zhimg.com/0fbb0d77d7501f95e9d7359500e3f7e5_r.png">

设计触发器时,需要注意触发器的几个时间特性,满足这些特性触发器才能正常工作:

建立时间(T setup time):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。

保持时间(T hold):是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。

数据输出延时(Tco, Clock-to-Output Delay):当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

注意只有建立时间(T setup time)与 数据输出延时(Tco, Clock-to-Output Delay)是在critical path上,是电路delay,如下图:

<img src="https://pic1.zhimg.com/d9fcd81afb98b97ccbb75758903c8270_b.png" data-rawwidth="813" data-rawheight="588" class="origin_image zh-lightbox-thumb" width="813" data-original="https://pic1.zhimg.com/d9fcd81afb98b97ccbb75758903c8270_r.png">

最后说下,触发器的内容一定要认真理解,这个是整个数字电路的基础。

你说到了同步异步,那我说下异步电路吧。异步电路不需要时钟,低功耗,速度快,但需要用大量握手信号来同步电路,设计起来很复杂,目前还是非主流,至少十年内时序同步电路仍会是主流。

-----------------------------------------------流水线分割------------------------------------------------------

PS.有小伙伴说最好扩充下流水线(pipeline)知识,那我补充下吧

pipeline是将组合逻辑进行分割,能让任务以类似并行方式处理,提高系统频率,提高吞吐量(throughput).

举个例子,假设洗衣分为四个步骤,分别在四个设备上进行,其中漂洗机器,烘干机器,在衣架上折叠衣服,把衣服放进柜子里各用30分钟,全过程需两小时。现有四个人去洗衣服,若sequential处理,一个人完成全步骤别人才开始,每人两小时,四个人共用八小时。如下图:

<img src="https://pic2.zhimg.com/390bc39fba2beed3db663a19673af545_b.png" data-rawwidth="884" data-rawheight="655" class="origin_image zh-lightbox-thumb" width="884" data-original="https://pic2.zhimg.com/390bc39fba2beed3db663a19673af545_r.png">但如果利用pipeline式的流水处理,当某人完成某步骤,其所用的设备就空闲了,后面的人就开始使用,四个人洗衣服只用3.5小时就能完成。如下图:

但如果利用pipeline式的流水处理,当某人完成某步骤,其所用的设备就空闲了,后面的人就开始使用,四个人洗衣服只用3.5小时就能完成。如下图:

但如果利用pipeline式的流水处理,当某人完成某步骤,其所用的设备就空闲了,后面的人就开始使用,四个人洗衣服只用3.5小时就能完成。如下图:<img src="https://pic4.zhimg.com/55192854ed0b8c60f021eea8daa7a26b_b.png" data-rawwidth="899" data-rawheight="658" class="origin_image zh-lightbox-thumb" width="899" data-original="https://pic4.zhimg.com/55192854ed0b8c60f021eea8daa7a26b_r.png">

注意,pipeline只是提高系统的吞吐量,不能改善单个任务的latency。在实际电路中是在组合逻辑中插入register,分割组合逻辑,实现pipeline,而register读写也需要时间,所以单个任务的执行时间反而会增长。另外在分割组合逻辑时,使分割后的每段处理时间尽量相同,因为系统时钟是由最慢的那段决定的。如下图:

<img src="https://pic3.zhimg.com/125587503227702e20f6763df965a62e_b.png" data-rawwidth="454" data-rawheight="446" class="origin_image zh-lightbox-thumb" width="454" data-original="https://pic3.zhimg.com/125587503227702e20f6763df965a62e_r.png">

总结:

<img src="https://pic3.zhimg.com/44b1695d296c1b292a37923023d99762_b.png" data-rawwidth="847" data-rawheight="593" class="origin_image zh-lightbox-thumb" width="847" data-original="https://pic3.zhimg.com/44b1695d296c1b292a37923023d99762_r.png">

一个经典的五级流水线处理器如下图:

<img src="https://pic3.zhimg.com/1e3667161c3307d95cf5d863dbe435fe_b.png" data-rawwidth="915" data-rawheight="654" class="origin_image zh-lightbox-thumb" width="915" data-original="https://pic3.zhimg.com/1e3667161c3307d95cf5d863dbe435fe_r.png">

------------------------------------------------------------------------------------------------------------------------

PS. 得到大家这么多赞,那补上另一个关于流水线中会出现的hazards的成因与解决方法的回答是否有既用到 状态机 又用到 流水线 的module? - young cc 的回答

http://www-inst.eecs.berkeley.edu/~cs61c/sp15/lec/09/2015Sp-CS61C-L09-kavs-SDS-1up.pdf

http://www-inst.eecs.berkeley.edu/~cs61c/sp15/lec/13/2015Sp-CS61C-L13-kavs-Pipelining-1up.pdf