概 述

数字电路:分组合逻辑电路和时序逻辑电路两大类。

组合逻辑电路的基本单元是门电路。

时序逻辑电路的基本单元是触发器。 一、触发器与门电路的区别

门电路某一时刻的输出信号完全取决于该时刻的输入信号,无记忆功能。

触发器具有记忆功能,能够在无信号的情况下,保持上一次的信号。 二、触发器的现态和次态

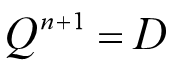

现态Qn——触发器接收输入信号之前的状态

次态Qn+1——触发器接收输入信号之后的状态 三、触发器的分类

从电路结构不同分:

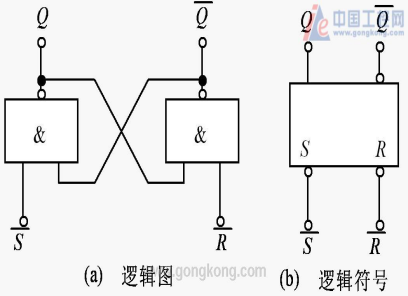

1、基本触发器

2、同步触发器

3、边沿触发器

从逻辑功能不同分:

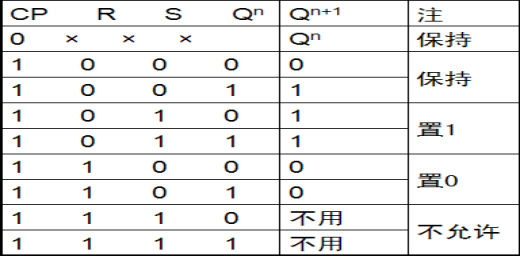

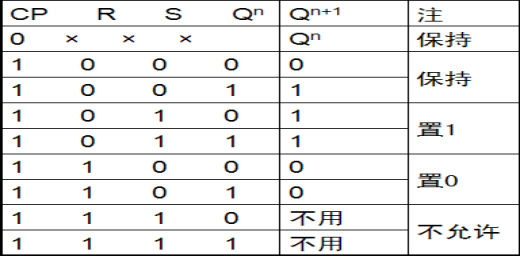

1、RS触发器

2、JK触发器

3、D触发器

4、T触发器

5、T’触发器

特性方程:

特性方程:

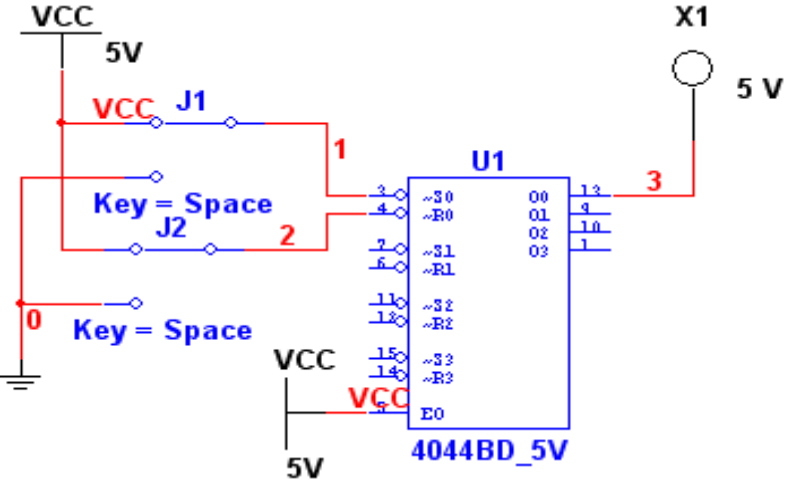

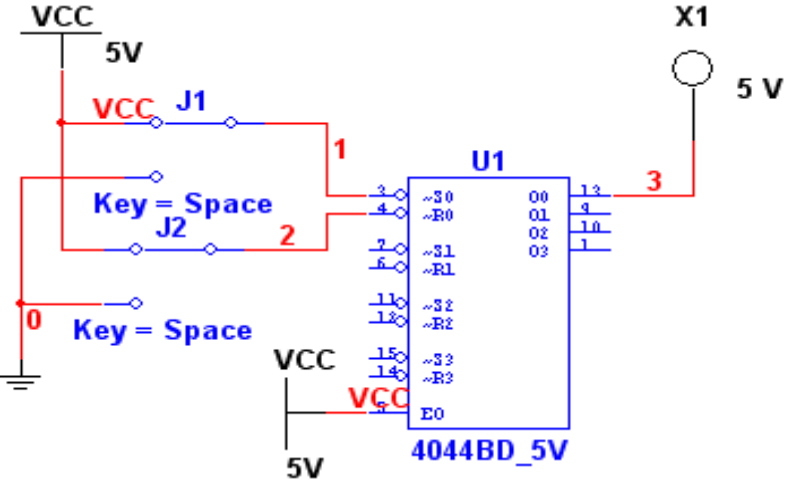

芯片型号:CC4044

芯片型号:CC4044

基本电路测试

基本电路测试

2、输出信号不仅和输入信号有关还和时钟信号相关

特性方程:

特性方程:

一、边沿触发器逻辑功能分类

一、边沿触发器逻辑功能分类

1、JK触发器

凡具有保持、置1、置0、翻转功能的电路都称为JK型时钟触发器,简称JK触发器。

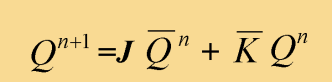

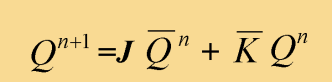

特性方程

特性方程

芯片型号:74LS112D

CP下降沿(或上升沿)有效

74LS112DJK触发器测试电路

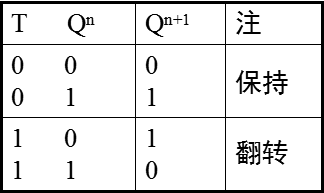

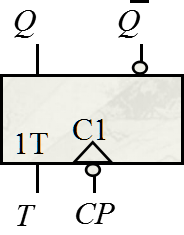

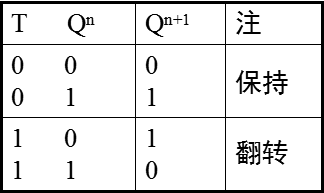

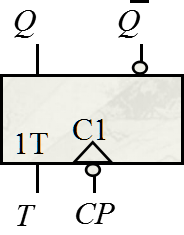

2、T型触发器

2、T型触发器

凡具有保持、翻转功能的电路,即当T=0是保持状态不变,T=1时翻转的电路,都称为T触发器。

⑴ 特性表

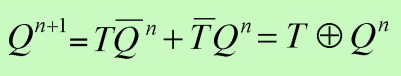

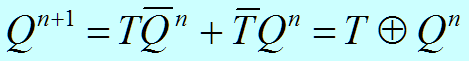

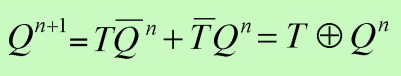

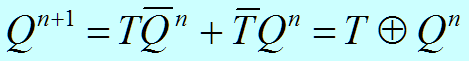

⑵ 特性方程

⑵ 特性方程

CP下降沿(或上升沿)有效 ⑶ 逻辑符号

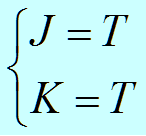

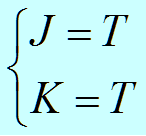

JK触发器→T触发器

T触发器特性方程:

JK触发器→T触发器

T触发器特性方程:

与JK触发器的特性方程比较,得:

与JK触发器的特性方程比较,得:

JK触发器变T触发器测试电路

JK触发器变T触发器测试电路

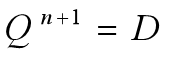

3、D型触发器

3、D型触发器

凡具有置1、置0功能的电路都称为D型时钟触发器,简称D型触发器或D触发器。 特性表

特性方程

特性方程

CP下降沿(或上升沿)时刻有效

芯片型号:74LS74D

CP下降沿(或上升沿)时刻有效

芯片型号:74LS74D

JK触发器→D触发器

D触发器的特性方程

JK触发器→D触发器

D触发器的特性方程

JK触发器的特性方程

JK触发器的特性方程

D触发器→T 触发器

逻辑功能:

D触发器→T 触发器

逻辑功能:

每来一次时钟脉冲,信号就翻转一次

D触发器到T’触发器

D触发器到T’触发器

数字电路:分组合逻辑电路和时序逻辑电路两大类。

组合逻辑电路的基本单元是门电路。

时序逻辑电路的基本单元是触发器。 一、触发器与门电路的区别

门电路某一时刻的输出信号完全取决于该时刻的输入信号,无记忆功能。

触发器具有记忆功能,能够在无信号的情况下,保持上一次的信号。 二、触发器的现态和次态

现态Qn——触发器接收输入信号之前的状态

次态Qn+1——触发器接收输入信号之后的状态 三、触发器的分类

从电路结构不同分:

1、基本触发器

2、同步触发器

3、边沿触发器

从逻辑功能不同分:

1、RS触发器

2、JK触发器

3、D触发器

4、T触发器

5、T’触发器

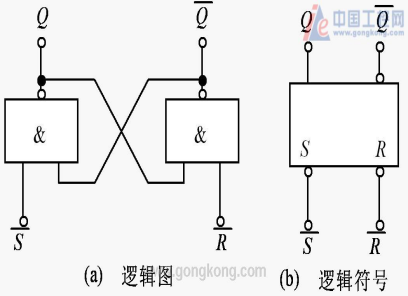

1、基本RS触发器

RS触发器特点:

特性方程:

特性方程: 芯片型号:CC4044

芯片型号:CC4044 基本电路测试

基本电路测试

2、时钟控制R-S触发器

特点:1、具有时钟输入引脚CP2、输出信号不仅和输入信号有关还和时钟信号相关

特性方程:

特性方程: 一、边沿触发器逻辑功能分类

一、边沿触发器逻辑功能分类1、JK触发器

凡具有保持、置1、置0、翻转功能的电路都称为JK型时钟触发器,简称JK触发器。

特性方程

特性方程

芯片型号:74LS112D

CP下降沿(或上升沿)有效

74LS112DJK触发器测试电路

2、T型触发器

2、T型触发器凡具有保持、翻转功能的电路,即当T=0是保持状态不变,T=1时翻转的电路,都称为T触发器。

⑴ 特性表

⑵ 特性方程

⑵ 特性方程

CP下降沿(或上升沿)有效 ⑶ 逻辑符号

JK触发器→T触发器

T触发器特性方程:

JK触发器→T触发器

T触发器特性方程: 与JK触发器的特性方程比较,得:

与JK触发器的特性方程比较,得:

JK触发器变T触发器测试电路

JK触发器变T触发器测试电路 3、D型触发器

3、D型触发器凡具有置1、置0功能的电路都称为D型时钟触发器,简称D型触发器或D触发器。 特性表

特性方程

特性方程 CP下降沿(或上升沿)时刻有效

芯片型号:74LS74D

CP下降沿(或上升沿)时刻有效

芯片型号:74LS74D JK触发器→D触发器

D触发器的特性方程

JK触发器→D触发器

D触发器的特性方程

JK触发器的特性方程

JK触发器的特性方程

D触发器→T 触发器

逻辑功能:

D触发器→T 触发器

逻辑功能:每来一次时钟脉冲,信号就翻转一次

D触发器到T’触发器

D触发器到T’触发器