PS:为了面试准备的,总结的比较粗糙。

1.实现D触发器逻辑

//基本D触发器

module D_EF(Q,D,CLK)

input D,CLK;

output Q;

reg Q; //在always语句中被赋值的信号要声明为reg类型 寄存器定义

always @ (posedge CLK)

begin Q <= D; end

endmodule

//带异步清0、异步置1的D触发器

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;//寄存器定义

always @ (posedge clk or negedge set or negedge reset)

begin

if(!reset) begin q<=0;qn<=1;end//异步清0,低有效

else if(!set) begin q<=1;qn<=1;end //异步置1,低有效

else begin q<=d;qn<=~d;end

end

endmodule

//带同步清0、同步置1的D触发器

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;

always @ (posedge clk)

begin

if(reset) begin q<=0;qn<=1;end//同步清0,高有效

else if(set) begin q<=1;qn<=1;end //同步置1,高有效

else begin q<=d;qn<=~d;end

end

endmodule

2.一个二选一mux 和一个inv实现异或

1^ 0 = 1

0 ^ 0 = 0

0 ^ 1 = 1

1 ^ 1 = 0

==》

b=0时输出 y=a;

b = 1时 y=~a

3.逻辑代数基本运算

3.逻辑代数基本运算

4.FPGA求三角函数,反三角函数

复杂运算——cordic算法

4.FPGA求三角函数,反三角函数

复杂运算——cordic算法

Cordic的方法核心就是伪旋转,将旋转角θ细化成若干个大小固定的角度θi,规定θi满足tanθi = 2^-i,通过一系列的迭代旋转,每次旋转θi,i为迭代次数,规定∑θi的范围即旋转角度θ的范围为[-99.7, 99.7]。如果θ的大于这个范围则可通过三角运算操作转化到该范围的角度。

xn = 1/∏cosθi (x0cosθ – y0sinθ)

yn = 1/∏cosθi (y0cosθ – x0sinθ)

伸缩因子,KN = 1 / ∏cosθi,已知迭代次数,我们可以预先计算KN的值。

我们预先计算出KN的值,然后令x0 = ∏cosθi,y0 = 0,则上述公式可化简为

xn = cosθ

yn = sinθ

即可实现正弦、余弦操作了。

5.FPGA实现FIFO控制器

https://download.csdn.net/download/u014485485/10681181

6.全加器

Cordic的方法核心就是伪旋转,将旋转角θ细化成若干个大小固定的角度θi,规定θi满足tanθi = 2^-i,通过一系列的迭代旋转,每次旋转θi,i为迭代次数,规定∑θi的范围即旋转角度θ的范围为[-99.7, 99.7]。如果θ的大于这个范围则可通过三角运算操作转化到该范围的角度。

xn = 1/∏cosθi (x0cosθ – y0sinθ)

yn = 1/∏cosθi (y0cosθ – x0sinθ)

伸缩因子,KN = 1 / ∏cosθi,已知迭代次数,我们可以预先计算KN的值。

我们预先计算出KN的值,然后令x0 = ∏cosθi,y0 = 0,则上述公式可化简为

xn = cosθ

yn = sinθ

即可实现正弦、余弦操作了。

5.FPGA实现FIFO控制器

https://download.csdn.net/download/u014485485/10681181

6.全加器

7.SRAM,SSRAM,DRAM,SDRAM

7.SRAM,SSRAM,DRAM,SDRAM

SRAM 利用寄存器来存储信息,所以一旦掉电,资料就会全部丢失,只要供电,它的资料就会一直存在,不需要动态刷新,所以叫静态随机存储器。

DRAM 利用MOS管的栅电容上的电荷来存储信息,一个DRAM的存储单元存储的是0还是1取决于电容是否有电荷,有电荷代表1,无电荷代表0。但时间一长,由于栅极漏电,代表1的电容会放电,代表0的电容会吸收电荷,这样会造成数据丢失,因此需要一个额外设电路进行内存刷新操作。刷新操作定期对电容进行检查,若电量大于满电量的1/2,则认为其代表1,并把电容充满电;若电量小于 1/2,则认为其代表0,并把电容放电,藉此来保持数据的连续性。这也是DRAM中的D(Dynamic动态)的意思。由于DRAM只使用一个MOS管来存信息,所以集成度可以很高,容量能够做的很大。SDRAM比它多了一个与CPU时钟同步。

SRAM(Static Dynamic Random Access Memory),它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。不像DRAM内存那样需要刷新电路,每隔一段时间,固定要对DRAM刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,所以在主板上SRAM存储器要占用一部分面积。

异步SRAM的访问独立于时钟,数据输入和输出都由地址的变化控制。

SSRAM(Synchronous SRAM)即同步静态随机存取存储器。同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

SDRAM(Synchronous Dynamic Random Access Memory)同步动态随机存取存储器,同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

DDR SDRAM(Double-Date-Rate SDRAM)也称作DDR RAM,这种改进型的RAM和SDRAM是基本一样的, 不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。这是目前电脑中用得最多的内存,在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。

https://blog.csdn.net/acs713/article/details/8139404

8.D触发器二分频电路

SRAM 利用寄存器来存储信息,所以一旦掉电,资料就会全部丢失,只要供电,它的资料就会一直存在,不需要动态刷新,所以叫静态随机存储器。

DRAM 利用MOS管的栅电容上的电荷来存储信息,一个DRAM的存储单元存储的是0还是1取决于电容是否有电荷,有电荷代表1,无电荷代表0。但时间一长,由于栅极漏电,代表1的电容会放电,代表0的电容会吸收电荷,这样会造成数据丢失,因此需要一个额外设电路进行内存刷新操作。刷新操作定期对电容进行检查,若电量大于满电量的1/2,则认为其代表1,并把电容充满电;若电量小于 1/2,则认为其代表0,并把电容放电,藉此来保持数据的连续性。这也是DRAM中的D(Dynamic动态)的意思。由于DRAM只使用一个MOS管来存信息,所以集成度可以很高,容量能够做的很大。SDRAM比它多了一个与CPU时钟同步。

SRAM(Static Dynamic Random Access Memory),它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。不像DRAM内存那样需要刷新电路,每隔一段时间,固定要对DRAM刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,所以在主板上SRAM存储器要占用一部分面积。

异步SRAM的访问独立于时钟,数据输入和输出都由地址的变化控制。

SSRAM(Synchronous SRAM)即同步静态随机存取存储器。同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

SDRAM(Synchronous Dynamic Random Access Memory)同步动态随机存取存储器,同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

DDR SDRAM(Double-Date-Rate SDRAM)也称作DDR RAM,这种改进型的RAM和SDRAM是基本一样的, 不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。这是目前电脑中用得最多的内存,在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。

https://blog.csdn.net/acs713/article/details/8139404

8.D触发器二分频电路

9.有源滤波器和无源滤波器

滤波器有无源和有源之分,无源滤波器是利用电感、电容和电阻的组合设计构成的滤波电路,可滤除某一次或多次谐波。有源滤波器是利用可关断电力电子器件,产生与负荷电流中谐波分量大小相等、相位相反电流来抵消谐波的滤波装置。

无源可以看成额外吸收谐波的负载,被动的吸收谐波;有源可以看成电源,主动的生成反向谐波。

对于这个的理解可以从英文来理解。 (Passive power filter,PPF),passive 可以理解为被动的消极的 专业翻译就是无源的。(Active power filter,APF) active 可以理解为主动的,积极的,专业翻译就是有源的。

10.傅里叶变换/拉普拉斯变换/Z变换

三种变换均是是将原先的时域信号变换到频域进行表示,在频域分析信号的特征。当信号变换到频域后,就会出现很多时域中无法直接观察到的现象。比如F域中的频谱响应;L域中的系统稳定性判断;Z域滤波器设计。

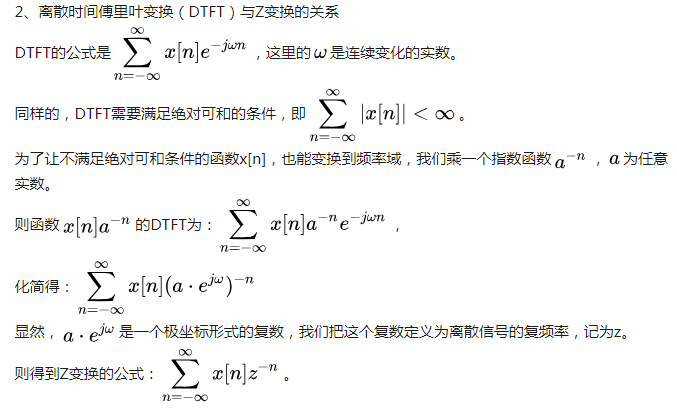

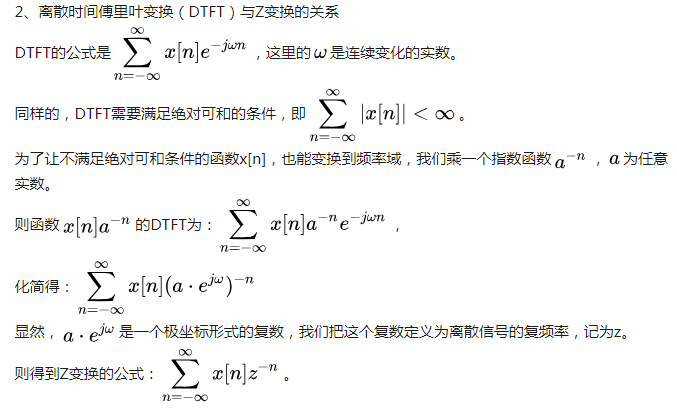

傅里叶变换粗略分来包括连续时间傅里叶变换(CTFT)、离散时间傅里叶变换(DTFT)。

CTFT是将连续时间信号变换到频域,将频率的含义扩充之后,就得到拉普拉斯变换。

DTFT是将离散时间信号变换到频域,将频率的含义扩充之后,就得到Z变换。

9.有源滤波器和无源滤波器

滤波器有无源和有源之分,无源滤波器是利用电感、电容和电阻的组合设计构成的滤波电路,可滤除某一次或多次谐波。有源滤波器是利用可关断电力电子器件,产生与负荷电流中谐波分量大小相等、相位相反电流来抵消谐波的滤波装置。

无源可以看成额外吸收谐波的负载,被动的吸收谐波;有源可以看成电源,主动的生成反向谐波。

对于这个的理解可以从英文来理解。 (Passive power filter,PPF),passive 可以理解为被动的消极的 专业翻译就是无源的。(Active power filter,APF) active 可以理解为主动的,积极的,专业翻译就是有源的。

10.傅里叶变换/拉普拉斯变换/Z变换

三种变换均是是将原先的时域信号变换到频域进行表示,在频域分析信号的特征。当信号变换到频域后,就会出现很多时域中无法直接观察到的现象。比如F域中的频谱响应;L域中的系统稳定性判断;Z域滤波器设计。

傅里叶变换粗略分来包括连续时间傅里叶变换(CTFT)、离散时间傅里叶变换(DTFT)。

CTFT是将连续时间信号变换到频域,将频率的含义扩充之后,就得到拉普拉斯变换。

DTFT是将离散时间信号变换到频域,将频率的含义扩充之后,就得到Z变换。

简而言之:

傅里叶变换只能对能量有限的信号进行变换(也就是可以收敛的信号),无法对能量无限的信号进行变换(无法收敛的信号)进行变换!

因此,拉氏变换由此诞生,他就是在傅里叶变换公式中乘以一个双肩因子,使得能量无限的信号也能进行时频变换!

Z变换就是离散化的拉氏变换!

简而言之:

傅里叶变换只能对能量有限的信号进行变换(也就是可以收敛的信号),无法对能量无限的信号进行变换(无法收敛的信号)进行变换!

因此,拉氏变换由此诞生,他就是在傅里叶变换公式中乘以一个双肩因子,使得能量无限的信号也能进行时频变换!

Z变换就是离散化的拉氏变换!

3.逻辑代数基本运算

3.逻辑代数基本运算

4.FPGA求三角函数,反三角函数

复杂运算——cordic算法

4.FPGA求三角函数,反三角函数

复杂运算——cordic算法

Cordic的方法核心就是伪旋转,将旋转角θ细化成若干个大小固定的角度θi,规定θi满足tanθi = 2^-i,通过一系列的迭代旋转,每次旋转θi,i为迭代次数,规定∑θi的范围即旋转角度θ的范围为[-99.7, 99.7]。如果θ的大于这个范围则可通过三角运算操作转化到该范围的角度。

xn = 1/∏cosθi (x0cosθ – y0sinθ)

yn = 1/∏cosθi (y0cosθ – x0sinθ)

伸缩因子,KN = 1 / ∏cosθi,已知迭代次数,我们可以预先计算KN的值。

我们预先计算出KN的值,然后令x0 = ∏cosθi,y0 = 0,则上述公式可化简为

xn = cosθ

yn = sinθ

即可实现正弦、余弦操作了。

5.FPGA实现FIFO控制器

https://download.csdn.net/download/u014485485/10681181

6.全加器

Cordic的方法核心就是伪旋转,将旋转角θ细化成若干个大小固定的角度θi,规定θi满足tanθi = 2^-i,通过一系列的迭代旋转,每次旋转θi,i为迭代次数,规定∑θi的范围即旋转角度θ的范围为[-99.7, 99.7]。如果θ的大于这个范围则可通过三角运算操作转化到该范围的角度。

xn = 1/∏cosθi (x0cosθ – y0sinθ)

yn = 1/∏cosθi (y0cosθ – x0sinθ)

伸缩因子,KN = 1 / ∏cosθi,已知迭代次数,我们可以预先计算KN的值。

我们预先计算出KN的值,然后令x0 = ∏cosθi,y0 = 0,则上述公式可化简为

xn = cosθ

yn = sinθ

即可实现正弦、余弦操作了。

5.FPGA实现FIFO控制器

https://download.csdn.net/download/u014485485/10681181

6.全加器

7.SRAM,SSRAM,DRAM,SDRAM

7.SRAM,SSRAM,DRAM,SDRAM

SRAM 利用寄存器来存储信息,所以一旦掉电,资料就会全部丢失,只要供电,它的资料就会一直存在,不需要动态刷新,所以叫静态随机存储器。

DRAM 利用MOS管的栅电容上的电荷来存储信息,一个DRAM的存储单元存储的是0还是1取决于电容是否有电荷,有电荷代表1,无电荷代表0。但时间一长,由于栅极漏电,代表1的电容会放电,代表0的电容会吸收电荷,这样会造成数据丢失,因此需要一个额外设电路进行内存刷新操作。刷新操作定期对电容进行检查,若电量大于满电量的1/2,则认为其代表1,并把电容充满电;若电量小于 1/2,则认为其代表0,并把电容放电,藉此来保持数据的连续性。这也是DRAM中的D(Dynamic动态)的意思。由于DRAM只使用一个MOS管来存信息,所以集成度可以很高,容量能够做的很大。SDRAM比它多了一个与CPU时钟同步。

SRAM(Static Dynamic Random Access Memory),它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。不像DRAM内存那样需要刷新电路,每隔一段时间,固定要对DRAM刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,所以在主板上SRAM存储器要占用一部分面积。

异步SRAM的访问独立于时钟,数据输入和输出都由地址的变化控制。

SSRAM(Synchronous SRAM)即同步静态随机存取存储器。同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

SDRAM(Synchronous Dynamic Random Access Memory)同步动态随机存取存储器,同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

DDR SDRAM(Double-Date-Rate SDRAM)也称作DDR RAM,这种改进型的RAM和SDRAM是基本一样的, 不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。这是目前电脑中用得最多的内存,在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。

https://blog.csdn.net/acs713/article/details/8139404

8.D触发器二分频电路

SRAM 利用寄存器来存储信息,所以一旦掉电,资料就会全部丢失,只要供电,它的资料就会一直存在,不需要动态刷新,所以叫静态随机存储器。

DRAM 利用MOS管的栅电容上的电荷来存储信息,一个DRAM的存储单元存储的是0还是1取决于电容是否有电荷,有电荷代表1,无电荷代表0。但时间一长,由于栅极漏电,代表1的电容会放电,代表0的电容会吸收电荷,这样会造成数据丢失,因此需要一个额外设电路进行内存刷新操作。刷新操作定期对电容进行检查,若电量大于满电量的1/2,则认为其代表1,并把电容充满电;若电量小于 1/2,则认为其代表0,并把电容放电,藉此来保持数据的连续性。这也是DRAM中的D(Dynamic动态)的意思。由于DRAM只使用一个MOS管来存信息,所以集成度可以很高,容量能够做的很大。SDRAM比它多了一个与CPU时钟同步。

SRAM(Static Dynamic Random Access Memory),它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。不像DRAM内存那样需要刷新电路,每隔一段时间,固定要对DRAM刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,所以在主板上SRAM存储器要占用一部分面积。

异步SRAM的访问独立于时钟,数据输入和输出都由地址的变化控制。

SSRAM(Synchronous SRAM)即同步静态随机存取存储器。同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

SDRAM(Synchronous Dynamic Random Access Memory)同步动态随机存取存储器,同步是指Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。

DDR SDRAM(Double-Date-Rate SDRAM)也称作DDR RAM,这种改进型的RAM和SDRAM是基本一样的, 不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。这是目前电脑中用得最多的内存,在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。

https://blog.csdn.net/acs713/article/details/8139404

8.D触发器二分频电路

9.有源滤波器和无源滤波器

滤波器有无源和有源之分,无源滤波器是利用电感、电容和电阻的组合设计构成的滤波电路,可滤除某一次或多次谐波。有源滤波器是利用可关断电力电子器件,产生与负荷电流中谐波分量大小相等、相位相反电流来抵消谐波的滤波装置。

无源可以看成额外吸收谐波的负载,被动的吸收谐波;有源可以看成电源,主动的生成反向谐波。

对于这个的理解可以从英文来理解。 (Passive power filter,PPF),passive 可以理解为被动的消极的 专业翻译就是无源的。(Active power filter,APF) active 可以理解为主动的,积极的,专业翻译就是有源的。

10.傅里叶变换/拉普拉斯变换/Z变换

三种变换均是是将原先的时域信号变换到频域进行表示,在频域分析信号的特征。当信号变换到频域后,就会出现很多时域中无法直接观察到的现象。比如F域中的频谱响应;L域中的系统稳定性判断;Z域滤波器设计。

傅里叶变换粗略分来包括连续时间傅里叶变换(CTFT)、离散时间傅里叶变换(DTFT)。

CTFT是将连续时间信号变换到频域,将频率的含义扩充之后,就得到拉普拉斯变换。

DTFT是将离散时间信号变换到频域,将频率的含义扩充之后,就得到Z变换。

9.有源滤波器和无源滤波器

滤波器有无源和有源之分,无源滤波器是利用电感、电容和电阻的组合设计构成的滤波电路,可滤除某一次或多次谐波。有源滤波器是利用可关断电力电子器件,产生与负荷电流中谐波分量大小相等、相位相反电流来抵消谐波的滤波装置。

无源可以看成额外吸收谐波的负载,被动的吸收谐波;有源可以看成电源,主动的生成反向谐波。

对于这个的理解可以从英文来理解。 (Passive power filter,PPF),passive 可以理解为被动的消极的 专业翻译就是无源的。(Active power filter,APF) active 可以理解为主动的,积极的,专业翻译就是有源的。

10.傅里叶变换/拉普拉斯变换/Z变换

三种变换均是是将原先的时域信号变换到频域进行表示,在频域分析信号的特征。当信号变换到频域后,就会出现很多时域中无法直接观察到的现象。比如F域中的频谱响应;L域中的系统稳定性判断;Z域滤波器设计。

傅里叶变换粗略分来包括连续时间傅里叶变换(CTFT)、离散时间傅里叶变换(DTFT)。

CTFT是将连续时间信号变换到频域,将频率的含义扩充之后,就得到拉普拉斯变换。

DTFT是将离散时间信号变换到频域,将频率的含义扩充之后,就得到Z变换。

简而言之:

傅里叶变换只能对能量有限的信号进行变换(也就是可以收敛的信号),无法对能量无限的信号进行变换(无法收敛的信号)进行变换!

因此,拉氏变换由此诞生,他就是在傅里叶变换公式中乘以一个双肩因子,使得能量无限的信号也能进行时频变换!

Z变换就是离散化的拉氏变换!

简而言之:

傅里叶变换只能对能量有限的信号进行变换(也就是可以收敛的信号),无法对能量无限的信号进行变换(无法收敛的信号)进行变换!

因此,拉氏变换由此诞生,他就是在傅里叶变换公式中乘以一个双肩因子,使得能量无限的信号也能进行时频变换!

Z变换就是离散化的拉氏变换!