一:部分主体操作步骤:(省略顶层BDF文件及virlog文件过程及生成元件)1.观察计数器内部原理:

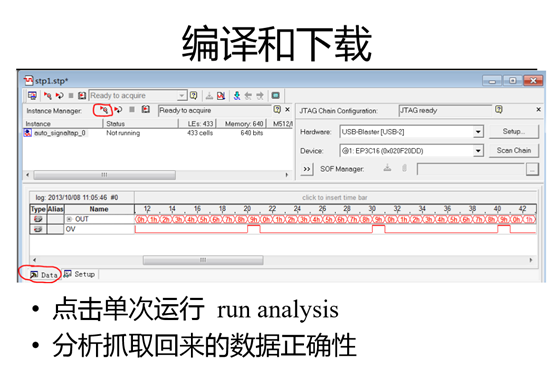

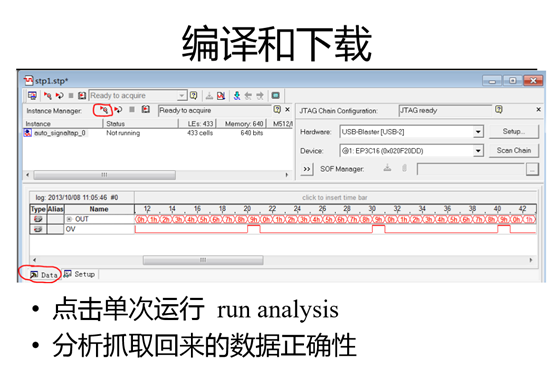

2.创建vwf文件,添加node finder并仿真,观察波形和毛刺。3.使用signal tap 文件进行验证。

二.0—9计数器中重点问题理解:(1)在①②,③④之间出现毛刺,因为OUT是几个子状态out[0][1][2][3]分别情况的组合,在输入端存在竞争,在输出端出现毛刺,即“冒险”。

二.0—9计数器中重点问题理解:(1)在①②,③④之间出现毛刺,因为OUT是几个子状态out[0][1][2][3]分别情况的组合,在输入端存在竞争,在输出端出现毛刺,即“冒险”。 (2)因为实际情况下时钟信号的延迟,使out[1]的信号略落后于其他路信号(这是竞争的一种正常情况),所以暂时出现了0,0,0,0的情况,因而出现毛刺(打开后是OUT为0的状态。)

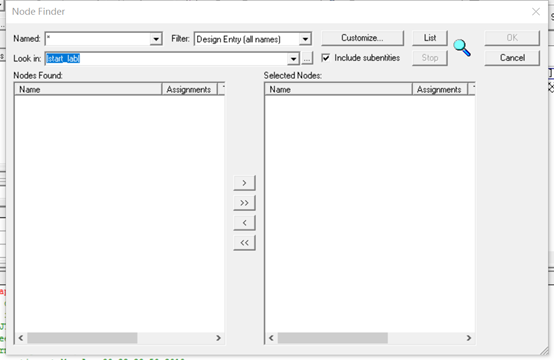

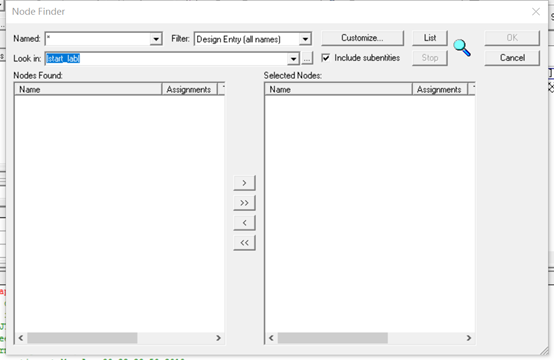

(2)因为实际情况下时钟信号的延迟,使out[1]的信号略落后于其他路信号(这是竞争的一种正常情况),所以暂时出现了0,0,0,0的情况,因而出现毛刺(打开后是OUT为0的状态。) 3.signal tapⅡ文件出现的问题:(1)在左下角进行node finder添加,而不是原文件。

3.signal tapⅡ文件出现的问题:(1)在左下角进行node finder添加,而不是原文件。 (2)一定要将原文件中的filter选项改成design empty(all names),然后重新编译并下载!

(2)一定要将原文件中的filter选项改成design empty(all names),然后重新编译并下载! 不然会出现问题:Signal TapⅡ file is not compatible with the file programmed in the device.!!!解决方法:将BDF文件下载到开发板!!!! 三.关于17进制计数器:注意以下问题:1. module代码如下:

不然会出现问题:Signal TapⅡ file is not compatible with the file programmed in the device.!!!解决方法:将BDF文件下载到开发板!!!! 三.关于17进制计数器:注意以下问题:1. module代码如下: 共18种状态,宽度定义为5。仿真波形如下:

共18种状态,宽度定义为5。仿真波形如下: 注意在仿真过程中可能出现:no simulation input file assignment specify,解决方法是:Assignments/simulator settings 其中有一个文本框simulationinput看是否为空,为空添加建立的VMF文件即可。

注意在仿真过程中可能出现:no simulation input file assignment specify,解决方法是:Assignments/simulator settings 其中有一个文本框simulationinput看是否为空,为空添加建立的VMF文件即可。 Signal tap验证完毕。(图如上)四:1——8输出0,9——17输出1:代码如下:

Signal tap验证完毕。(图如上)四:1——8输出0,9——17输出1:代码如下: 无可避免的出现毛刺… …

无可避免的出现毛刺… … Emmmmmm… …关于消除毛刺… …新手博主查阅资料中,如果有好方法… …希望大家能在评论区告诉博主… …提前感谢… …五.关于把OV信号接到LED灯上… …本来应该是隔0.02*17微秒闪烁一次,但由于时间太短,只能看见一直亮着的LED灯。

Emmmmmm… …关于消除毛刺… …新手博主查阅资料中,如果有好方法… …希望大家能在评论区告诉博主… …提前感谢… …五.关于把OV信号接到LED灯上… …本来应该是隔0.02*17微秒闪烁一次,但由于时间太短,只能看见一直亮着的LED灯。

2.创建vwf文件,添加node finder并仿真,观察波形和毛刺。3.使用signal tap 文件进行验证。

二.0—9计数器中重点问题理解:(1)在①②,③④之间出现毛刺,因为OUT是几个子状态out[0][1][2][3]分别情况的组合,在输入端存在竞争,在输出端出现毛刺,即“冒险”。

二.0—9计数器中重点问题理解:(1)在①②,③④之间出现毛刺,因为OUT是几个子状态out[0][1][2][3]分别情况的组合,在输入端存在竞争,在输出端出现毛刺,即“冒险”。 (2)因为实际情况下时钟信号的延迟,使out[1]的信号略落后于其他路信号(这是竞争的一种正常情况),所以暂时出现了0,0,0,0的情况,因而出现毛刺(打开后是OUT为0的状态。)

(2)因为实际情况下时钟信号的延迟,使out[1]的信号略落后于其他路信号(这是竞争的一种正常情况),所以暂时出现了0,0,0,0的情况,因而出现毛刺(打开后是OUT为0的状态。) 3.signal tapⅡ文件出现的问题:(1)在左下角进行node finder添加,而不是原文件。

3.signal tapⅡ文件出现的问题:(1)在左下角进行node finder添加,而不是原文件。 (2)一定要将原文件中的filter选项改成design empty(all names),然后重新编译并下载!

(2)一定要将原文件中的filter选项改成design empty(all names),然后重新编译并下载! 不然会出现问题:Signal TapⅡ file is not compatible with the file programmed in the device.!!!解决方法:将BDF文件下载到开发板!!!! 三.关于17进制计数器:注意以下问题:1. module代码如下:

不然会出现问题:Signal TapⅡ file is not compatible with the file programmed in the device.!!!解决方法:将BDF文件下载到开发板!!!! 三.关于17进制计数器:注意以下问题:1. module代码如下: 共18种状态,宽度定义为5。仿真波形如下:

共18种状态,宽度定义为5。仿真波形如下: 注意在仿真过程中可能出现:no simulation input file assignment specify,解决方法是:Assignments/simulator settings 其中有一个文本框simulationinput看是否为空,为空添加建立的VMF文件即可。

注意在仿真过程中可能出现:no simulation input file assignment specify,解决方法是:Assignments/simulator settings 其中有一个文本框simulationinput看是否为空,为空添加建立的VMF文件即可。 Signal tap验证完毕。(图如上)四:1——8输出0,9——17输出1:代码如下:

Signal tap验证完毕。(图如上)四:1——8输出0,9——17输出1:代码如下: 无可避免的出现毛刺… …

无可避免的出现毛刺… … Emmmmmm… …关于消除毛刺… …新手博主查阅资料中,如果有好方法… …希望大家能在评论区告诉博主… …提前感谢… …五.关于把OV信号接到LED灯上… …本来应该是隔0.02*17微秒闪烁一次,但由于时间太短,只能看见一直亮着的LED灯。

Emmmmmm… …关于消除毛刺… …新手博主查阅资料中,如果有好方法… …希望大家能在评论区告诉博主… …提前感谢… …五.关于把OV信号接到LED灯上… …本来应该是隔0.02*17微秒闪烁一次,但由于时间太短,只能看见一直亮着的LED灯。