最近在设计中遇到了亚稳态情况的处理,因此又回头去看了一下数字电路中的时序分析,本篇文章主要讲的就是数字电路中的时序分析。

延时可以分成两大类:一类是门延时;另一类的是D触发器的延时。这两类延时在时序电路分析中都要涉及到。首先我们来看一下门延时。

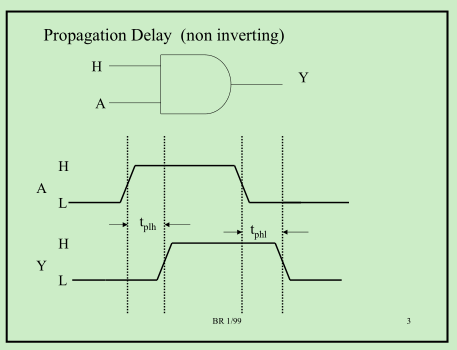

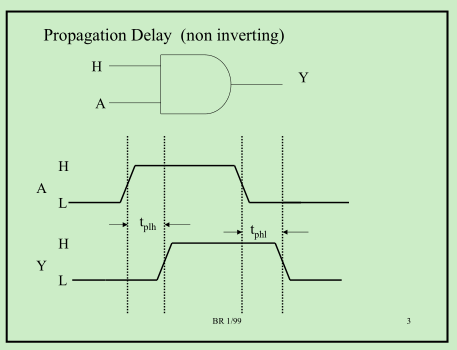

门延时指的是构成门的晶体管在有限的时间内完成转换,也就是当门的输入变化时,输出在有限的时间里完成改变,这个改变所用的有限时间就是门延时,也就是传播延时(propagation delay,后面缩写为pd)。通常晶体管的尺寸越小,转换就越快。

传播延时分为两类,Tphl,指的是输入改变时输出由高到低;Tplh指的是输入改变时,输出由低到高。这两个时间均是在输入的50%和输出的50%处测量,如下图所示:

下面讲一下D触发器的延时,对于一个D触发器,需要关注的时序有三个方面: 1.C2Q:指的是时钟C改变是,Q改变所需要的延时,属于传播延时propagation delay. 2.setup 时间:时钟上升沿之前,输入稳定所需要的时间。 这里可以给出英文的定义,更恰切一些:the amount of time the synchronous input(D) must be stable before the active edge of clock 3.hold 时间:时钟上升沿来临之后,输入要保持稳定的时间。 同样给出英文定义:the amount of time the synchronous input(D) must be stable after the active edge of clock,如图所示:

下面讲一下D触发器的延时,对于一个D触发器,需要关注的时序有三个方面: 1.C2Q:指的是时钟C改变是,Q改变所需要的延时,属于传播延时propagation delay. 2.setup 时间:时钟上升沿之前,输入稳定所需要的时间。 这里可以给出英文的定义,更恰切一些:the amount of time the synchronous input(D) must be stable before the active edge of clock 3.hold 时间:时钟上升沿来临之后,输入要保持稳定的时间。 同样给出英文定义:the amount of time the synchronous input(D) must be stable after the active edge of clock,如图所示: