实验内容

作业要求第一种方法:异步高电平复位

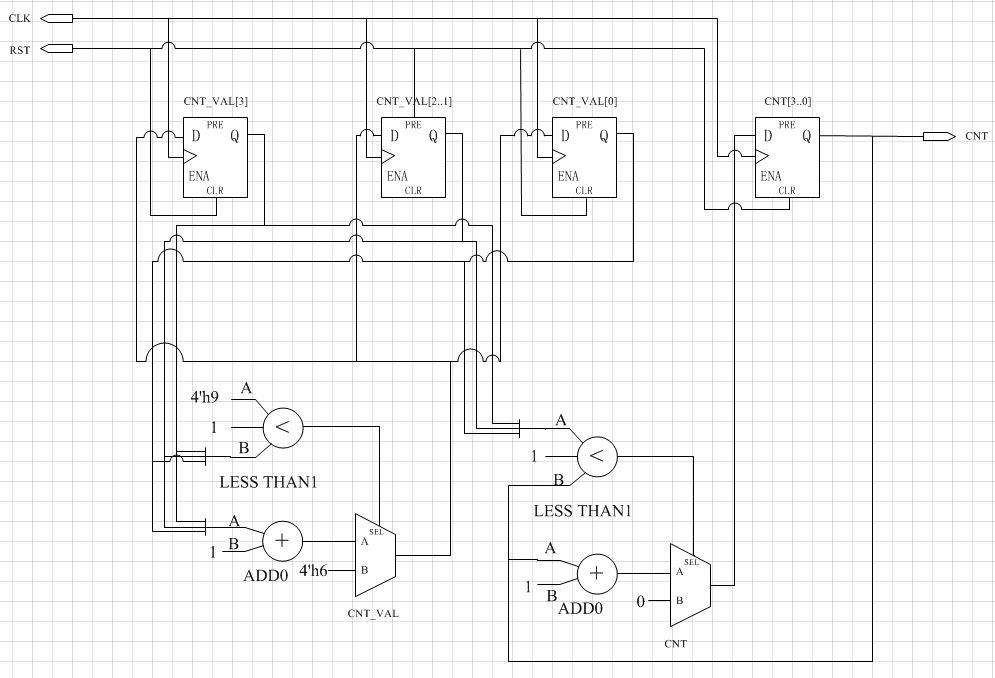

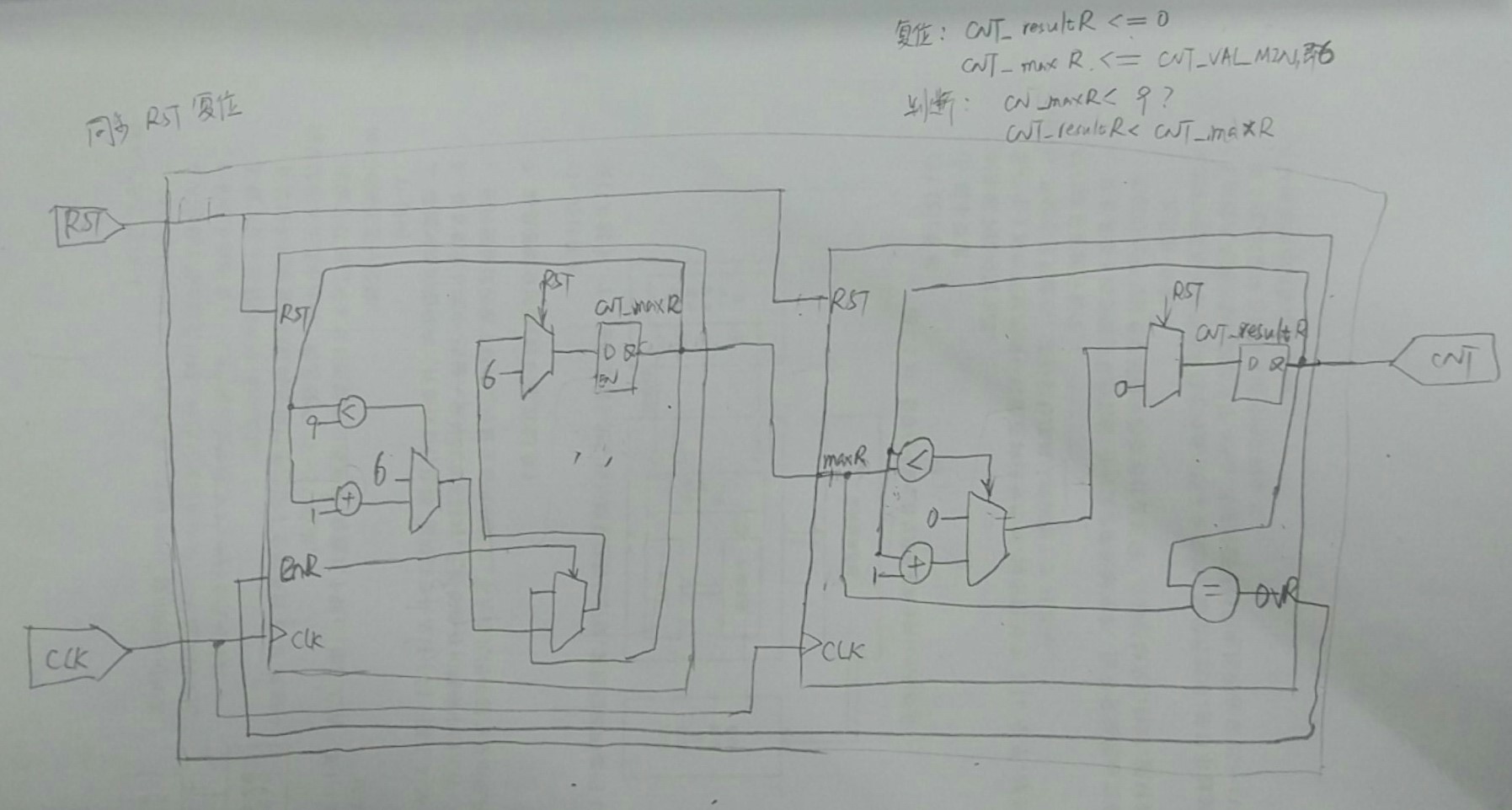

手工绘制的电路结构RTL设计图

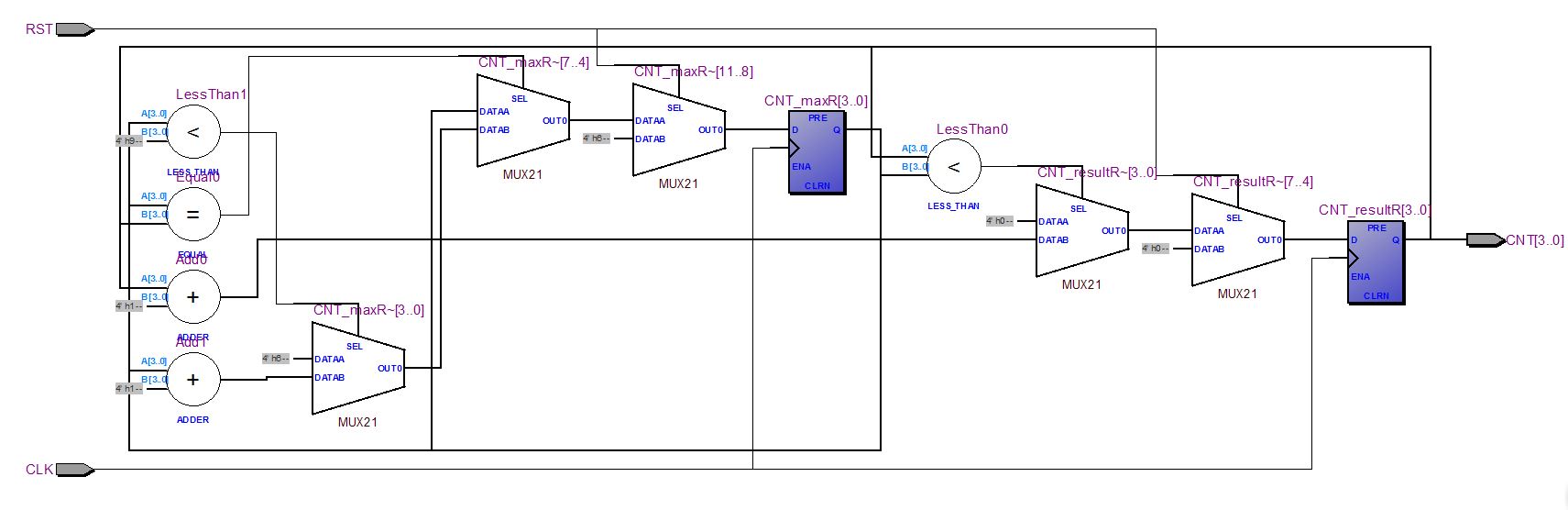

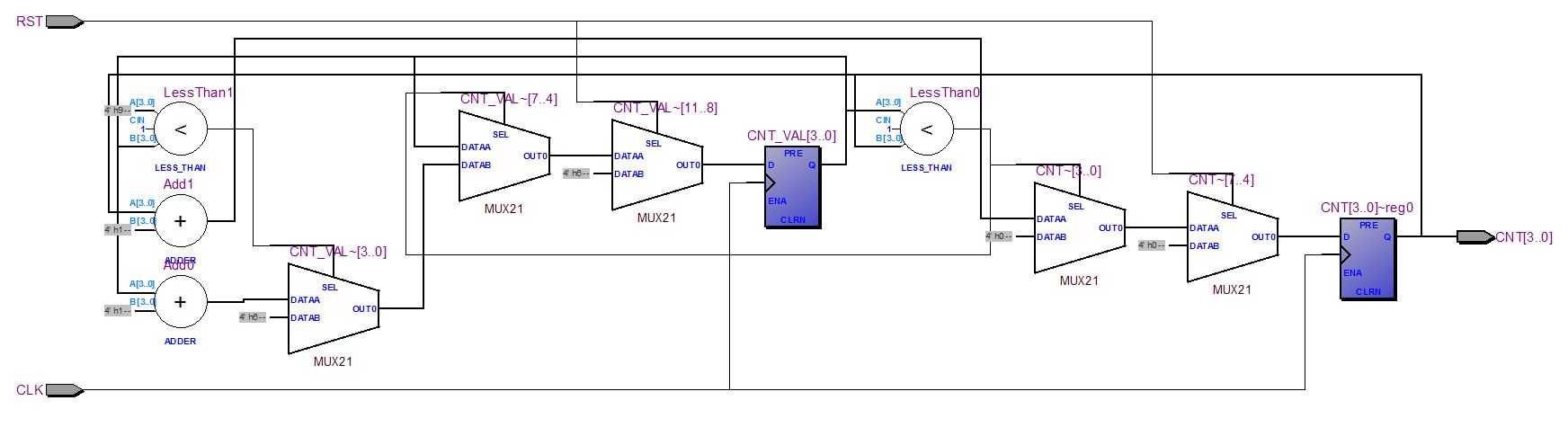

- 思路:本题计数器需要用到的RTL符号有2个4位寄存器、2个双路选择器、2个加法器、2个比较器

- 异步高电平复位:复位信号只要变高电平就立即执行复位操作。CNT(计数值)预置初值为零;CNT_VAL_MAX(计数最大值)预置初值4’b0110(即CNT_VAL_min)。

- 判断CNT与CNT_VAL大小,若CNT>=CNT_VAL,则双路选择器选通输出4’h0给CNT寄存器的输入端;否则CNT计数+1再将其通过双路选择器选通输出送入CNT寄存器的输入端。如下图框内①

- 此外,当CNT>=CNT_VAL时,CNT_VAL计数+1并与9(即CNT_VAL_MAX)比较:若CNT_VAL>=9,则双路选择器选通输出4’h6给CNT_VAL寄存器的输入端;否则再将CNT_VAL原值送回CNT_VAL寄存器的输入端。如下图框内②

- 手工绘制RTL图:

Quartus扫描生成的电路RTL图

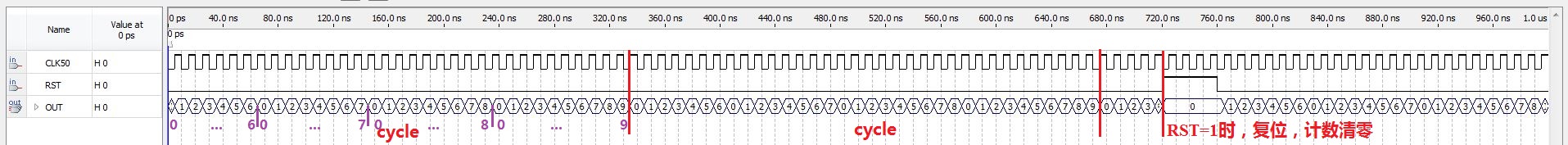

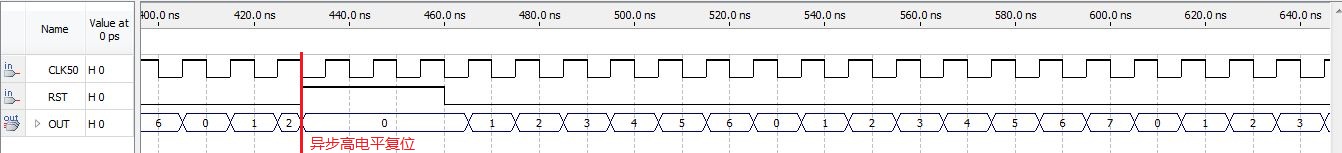

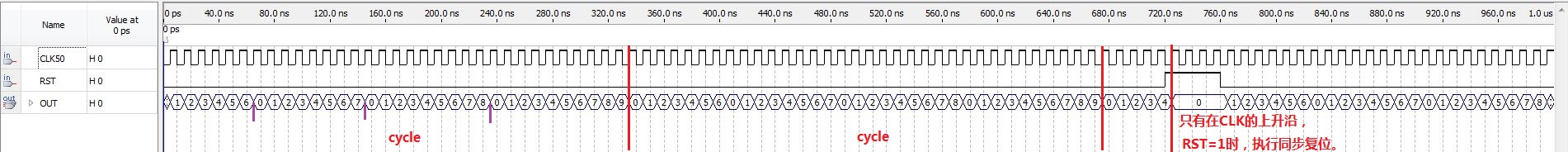

计数器的波形仿真截图

- 计数器在电路复位后会循环的从0值递增计数到最大值,计数最大值是一个循环变化的过程,计数器复位之后,第一次计数最大值是6,然后是7、8、9,然后计数最大值又变成6,如此往复循环,计数过程如下图所示。

- 异步高电平复位:复位信号只要变成高电平就执行复位操作,如下图所示。

计数器代码

module cnt_circle_0to9(

CLK , // clock

RST , //reset

CNT); // output

input CLK;//clock

input RST;//reset,

output [4-1:0] CNT;//output counter value

parameter CNT_VAL_MIN=6;//counter cycle min value

parameter CNT_VAL_MAX=9;//counter cycle max value

reg [4-1:0] CNT;

reg [4-1:0] CNT_VAL=CNT_VAL_MIN;

//异步高电平复位就是复位信号只要变高电平就执行复位操作,如果是同步的话就要看复位信号是否在时钟有效沿为高电平。

//异步高电平复位

always @ (posedge CLK or posedge RST)begin

if(RST)begin

CNT <= 0;

CNT_VAL <= CNT_VAL_MIN;

end

else begin

if(CNT >= CNT_VAL)begin //Less Than0

CNT <= 0;

CNT_VAL <= CNT_VAL + 1'b1; //ADD0,非阻塞赋值,同时完成

if(CNT_VAL >= CNT_VAL_MAX) //Less Than1

CNT_VAL <= CNT_VAL_MIN;

end

else CNT <= CNT + 1'b1; //ADD1

end

end

////同步高电平复位

//always @ (posedge CLK) begin

// if(RST)begin

// CNT <= 0;

// CNT_VAL <= CNT_VAL_MIN;

// end

// else begin

// if(CNT >= CNT_VAL)begin //Less Than0

// CNT <= 0;

// CNT_VAL <= CNT_VAL + 1'b1; //ADD1

// if(CNT_VAL >= CNT_VAL_MAX) //Less Than1

// CNT_VAL <= CNT_VAL_MIN;

// end

// else CNT <= CNT + 1'b1; //ADD0

// end

//end

endmodule // module cnt_circle_0to9

第二种方法:同步高电平复位

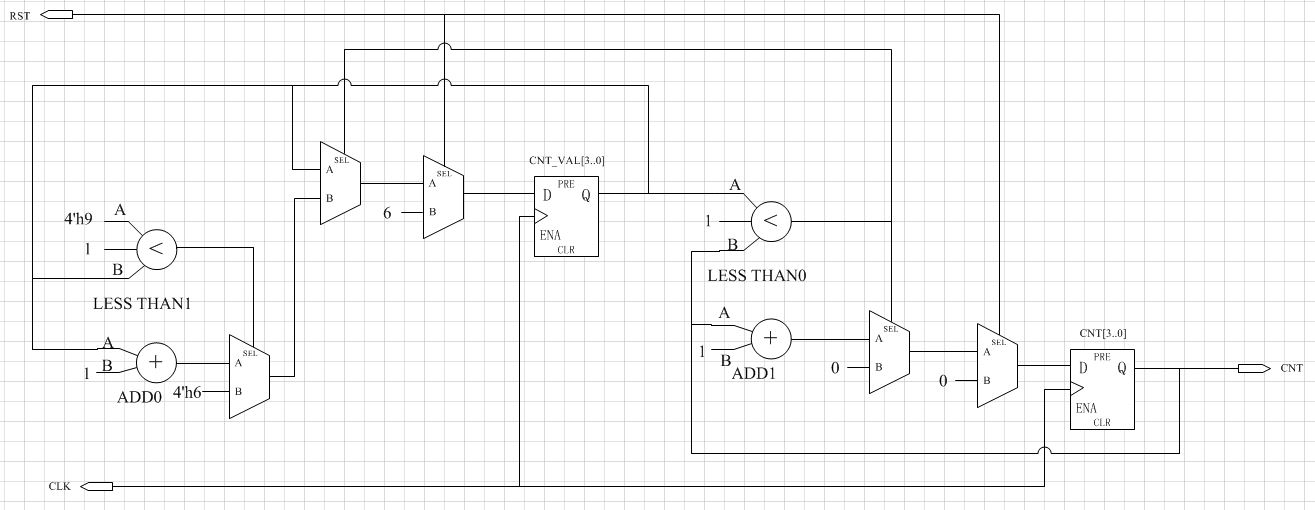

手工绘制的电路结构RTL设计图

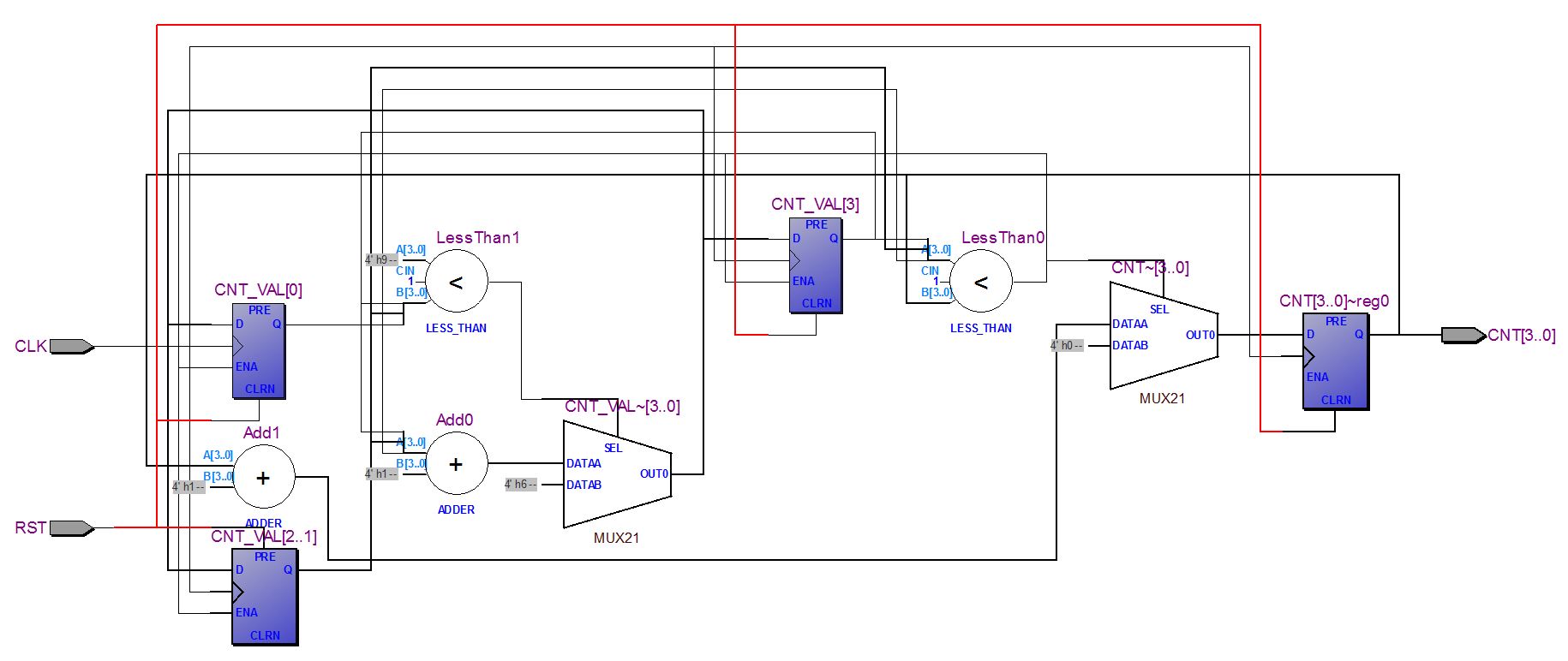

- 思路:本题计数器需要用到的RTL符号有2个4位寄存器、5个双路选择器、2个加法器、2个比较器

- 同步高电平复位:只有在时钟有效沿复位信号为高电平时,才进行复位操作。因此两个寄存器前分别需要一个双路选择器,由RST选择通路。接下来的思路与异步复位类似。

- 手工绘制RTL图:

Quartus扫描生成的电路RTL图

计数器的波形仿真截图

- 同步高电平复位:只有在CLK上升沿当复位信号为高电平才执行复位操作,如下图所示。

计数器代码

- 代码见上面代码被注释部分。

module cnt_circle_v2_0to9(

CLK , // clock

RST , //reset

CNT); // output

input CLK;//clock

input RST;//reset,

output [4-1:0] CNT;//output counter value

parameter MAX_min=6;//counter cycle min value

parameter MAX_max=9;//counter cycle max value

reg [4-1:0] CNT_maxR = MAX_min;//count for MAX

reg enR , ovR ;

reg [4-1:0] CNT_resultR;//count for result

//异步高电平复位就是复位信号只要变高电平就执行复位操作,如果是同步的话就要看复位信号是否在时钟有效沿为高电平。

//异步高电平复位

always @ (posedge CLK)begin

if(RST)begin

CNT_resultR <= 0;

CNT_maxR <= MAX_min;

end

else begin

if(CNT_resultR < CNT_maxR)begin

CNT_resultR <= CNT_resultR + 1'b1;

end

else begin

CNT_resultR <= 0;

end

if(enR)begin

if(CNT_maxR < MAX_max)begin

CNT_maxR <= CNT_maxR + 1'b1;

end

else

CNT_maxR <= MAX_min;

end

else

CNT_maxR <= CNT_maxR ;

end

end

always @ (CNT_resultR)begin

enR = ovR;

if(CNT_resultR == CNT_maxR)

ovR = 1;

else

ovR = 0;

end

assign CNT = CNT_resultR;

endmodule // module cnt_circle_v2_0to9

两种方法比较

- 差异从两方面看:

- 波形仿真:异步复位,从RST=0时立即执行复位操作,计数清零;同步复位,只有在CLK上升沿RST=1才执行复位。

- RTL图:异步复位时,是通过RST给CNT和CNT_VAL寄存器分别预置初值;同步复位是RST通过双路选择器确定两个寄存器的初值。