- 设计直接数字频率合成(DDS)

要求:

–用计数器生成地址、读取ROM数据

–理解二进制补码和无符号数

–修改计数增量值,观察波形变化,思考输出频率

和计数器增量值的关系。

1、 例化的子模块代码

// 带计数增量输入的计数器 //

module cnt_incr(

CLK , // clock

INCR , // counter increase value

CNTVAL); // counter value

input CLK;

input [7-1:0] INCR;

output [7-1:0] CNTVAL;

reg [7-1:0] CNTVAL;

always @ (posedge CLK) begin

CNTVAL <= INCR + CNTVAL;

end

endmodule

//生成正弦波表的rom【代码太长,此处略去150行】 //

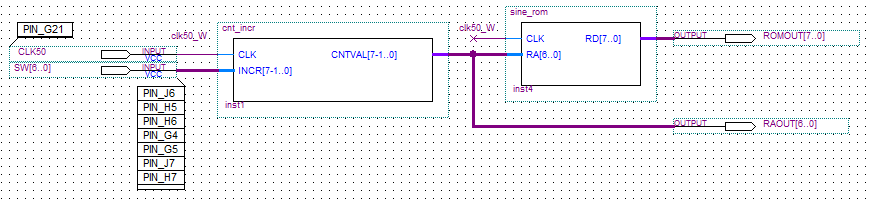

2、原理图  3、RTL图

3、RTL图  计数器模块内部电路结构:

计数器模块内部电路结构:  【思考】:如果加法器溢出了,输出结果会怎样?

【思考】:如果加法器溢出了,输出结果会怎样? 【答】:当相位累加器的溢出时,—个完整的阶梯正弦信号就从ROM查询表的输出端输出。因此,相位累加器的溢出率就是正弦波信号的输出频率。 ROM内部电路结构:

4、不同的计数增量值对应的波形

(1)计数增量为1时,正弦波频率约0.39 MHZ

4、不同的计数增量值对应的波形

(1)计数增量为1时,正弦波频率约0.39 MHZ  (2)计数增量为2时,正弦波频率约0.78 MHZ

(2)计数增量为2时,正弦波频率约0.78 MHZ  (3)计数增量为4时,正弦波频率1.5625 MHZ

(3)计数增量为4时,正弦波频率1.5625 MHZ  【问题一】拨动开关,观察不同频率的正弦波, 电路的工作时钟是50MHz

【问题一】拨动开关,观察不同频率的正弦波, 电路的工作时钟是50MHz (1) 请回答,你能得到的正弦波频率和计数器增量值的对应关系是什么?

(2)请回答,你能得到的最低频率的正弦波是多少?设该频率为f1

(3)请思考,能否有什么方法能够得到比f1频率还低的正弦波

【答】:

(1)正弦波频率和计数器增量值成 线性关系。

(2)正弦波的最低频率f1约0.39 MHZ。

(3)增加计数器增量或减小计数器数据位宽。 【问题二】输出信号频率 和 电路工作时钟频率,计数器增量值,以及计数器数据位宽之间的表达式关系?

【答】:

学生实验:

学生实验:

- 设计直接数字频率合成(DDS)

要求:

–把计数增量输入信号分配到10个拨码开关上

–把计数值信号的高7位分配为ROM的地址,低3位悬空不使用。

–编译、下载电路,拨动拨码开关,观察最低频率有什么变化。

// 带计数增量输入的计数器 //

module cnt_incr(

CLK , // clock

INCR , // counter increase value

CNTVAL); // counter value

input CLK;

input [10-1:0] INCR;

output [10-1:0] CNTVAL;

reg [10-1:0] CNTVAL;

always @ (posedge CLK) begin

CNTVAL <= INCR + CNTVAL;

end

endmodule

//生成正弦波表的rom【代码太长,此处略去150行】 //

2、原理图  3、不同的计数增量值对应的波形

(1)计数增量为1时,正弦波频率约0.0488 MHZ

3、不同的计数增量值对应的波形

(1)计数增量为1时,正弦波频率约0.0488 MHZ  (2)计数增量为2时,正弦波频率约0.0976 MHZ

(2)计数增量为2时,正弦波频率约0.0976 MHZ  (3)计数增量为4时,正弦波频率约0.1953 MHZ

(3)计数增量为4时,正弦波频率约0.1953 MHZ