STM32F407 144脚封装的第143脚PDR,一直没有关注过,板子上是直接对其悬空处理,悬空到底对系统有没有什么影响,查看了STM32F4系列的技术手册也没有发祥有相关说明。只是说明了PDR脚要接到VDD或者VSS(根据芯片不同而不同),没有说明悬空会怎么样?若有大牛知道望告知一二不胜感激!

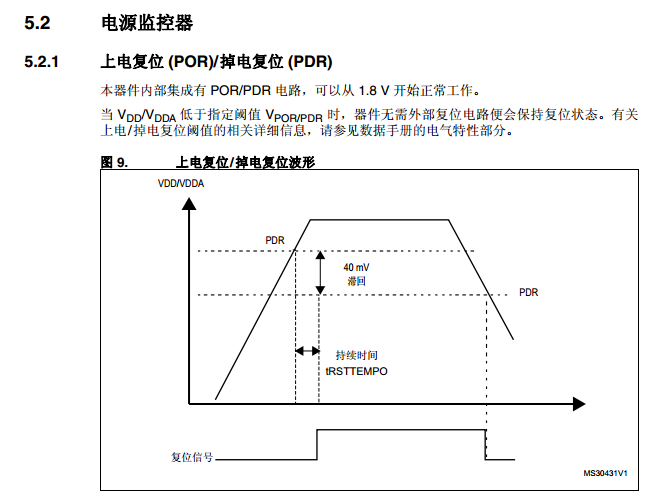

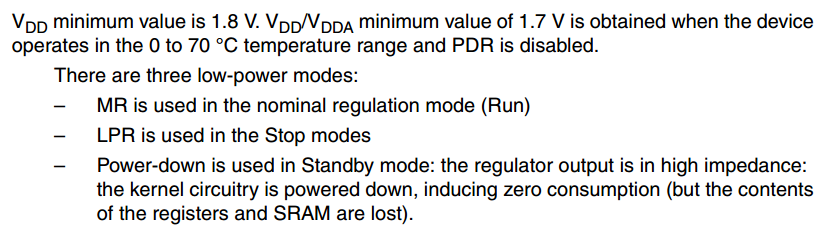

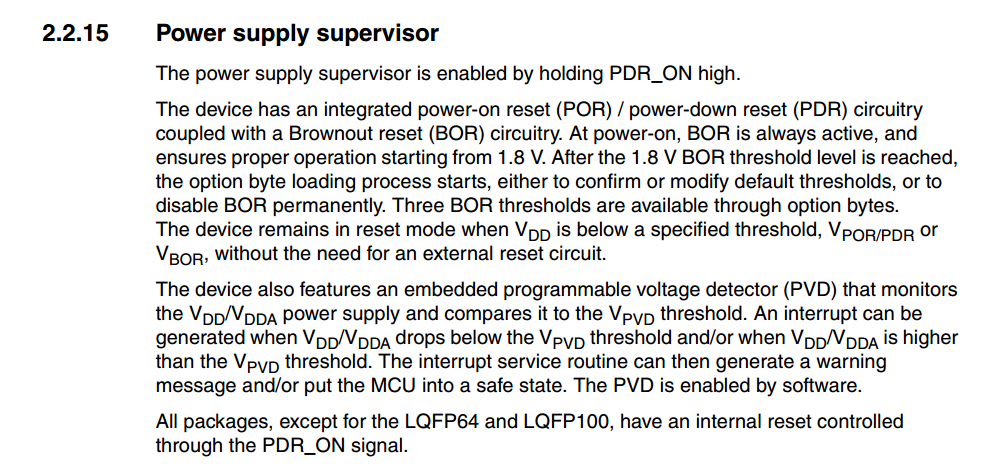

PDR全称为power down reset,也就是掉电复位,RM0090参考手册上是这样描述的:

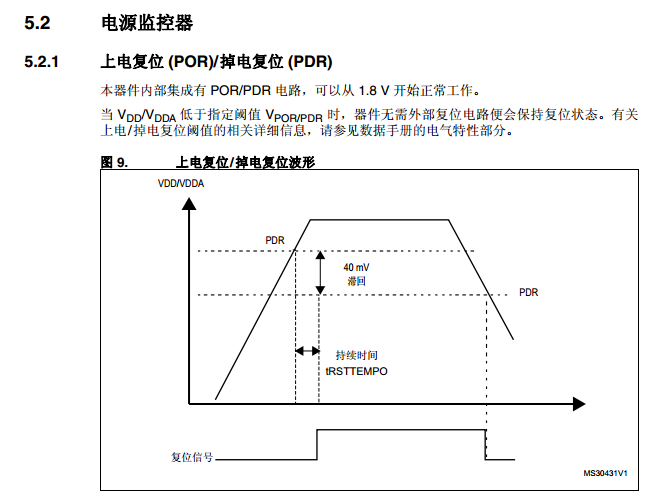

从图中可以看出,当PDR脚的电压低于1.8V时,芯片将会进入复位状态。

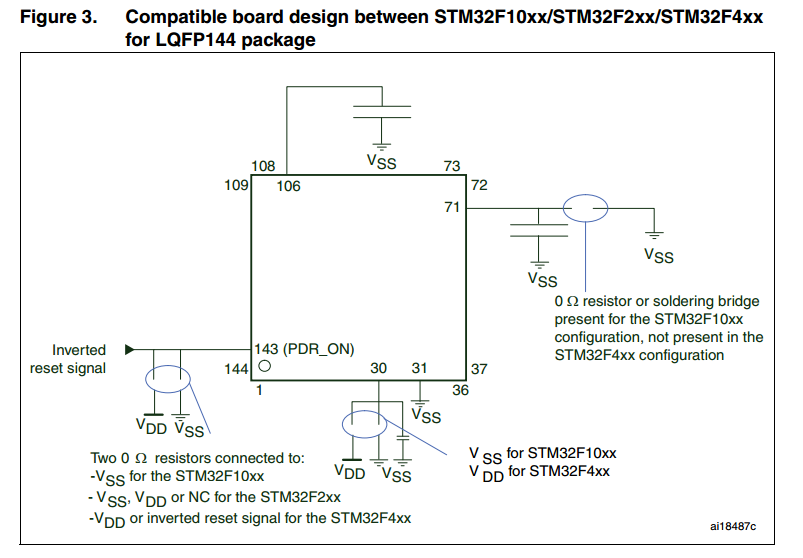

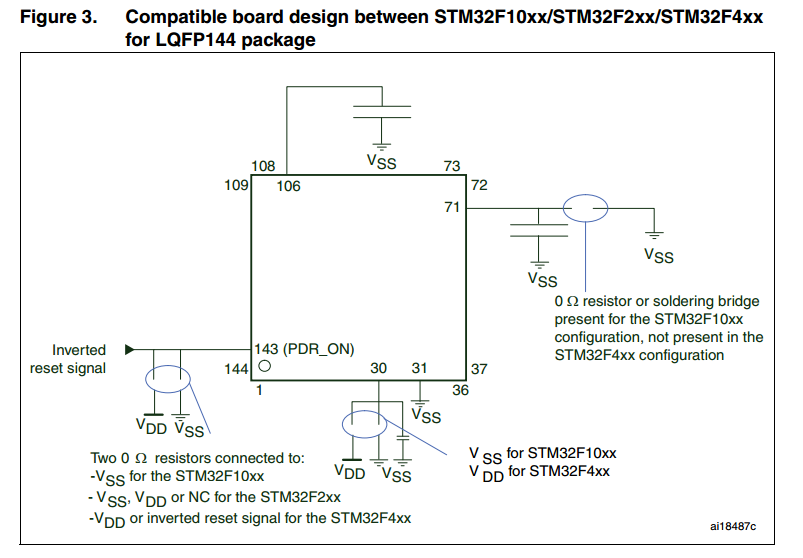

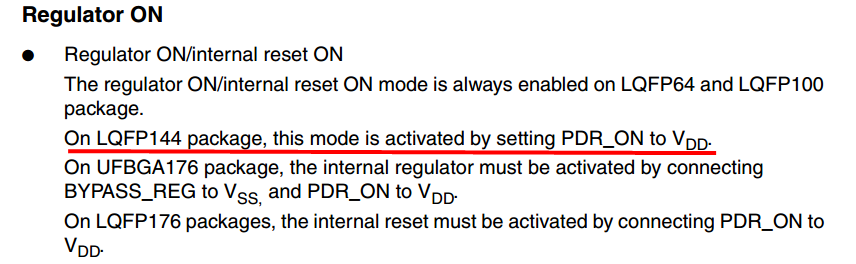

当PDR脚悬空时,在某种情况下是否会触发芯片复位? PDR脚具体怎么接还需要看另外一份文档,stm32f407_datasheet, Doc ID 022152 Rev2中相关的内容是这么描述的:

由上可见,stm32F4系列需要将PDR脚接到VDD来使能,掉电复位。

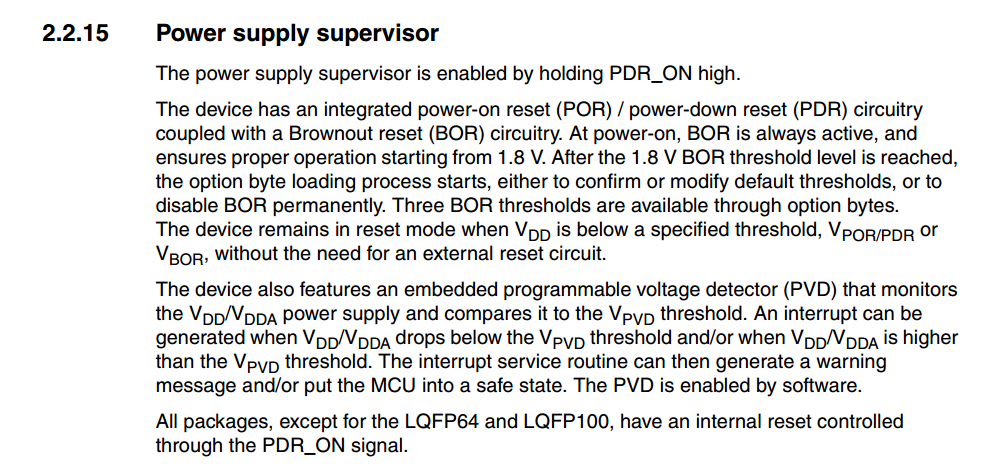

这上面的描述说明,要使能电压换监控器必须要保持PDR引脚为高,POR上电复位,PDR掉电复位和BOR欠压保护。

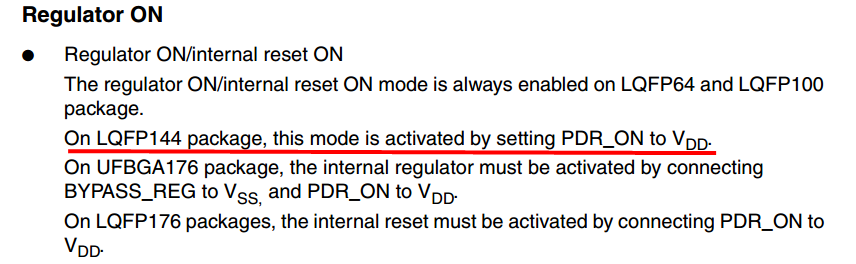

与PDR引脚关联的另一个功能是调压器,文档stm32f407_datasheet, Doc ID 022152 Rev2明确说明了LQFP114封装的芯片要使能电压调节器必须要将PDR拉高。

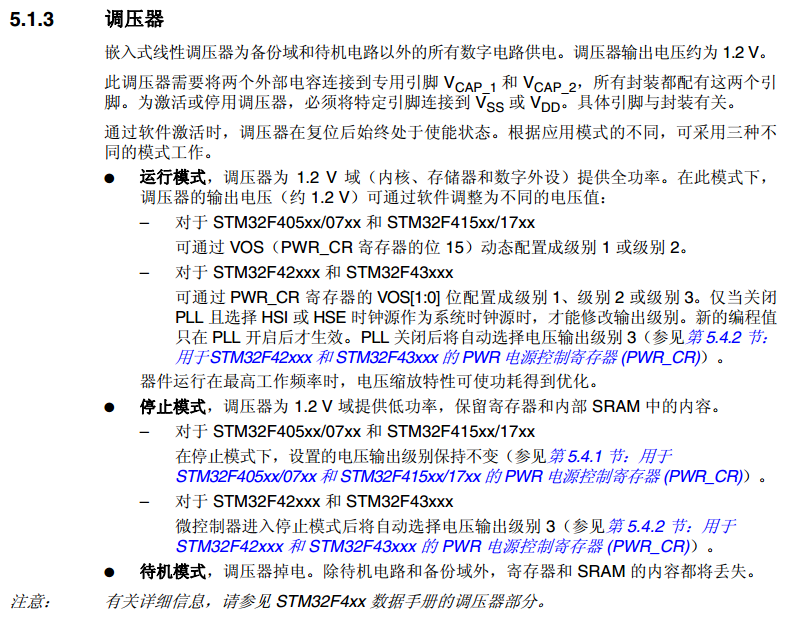

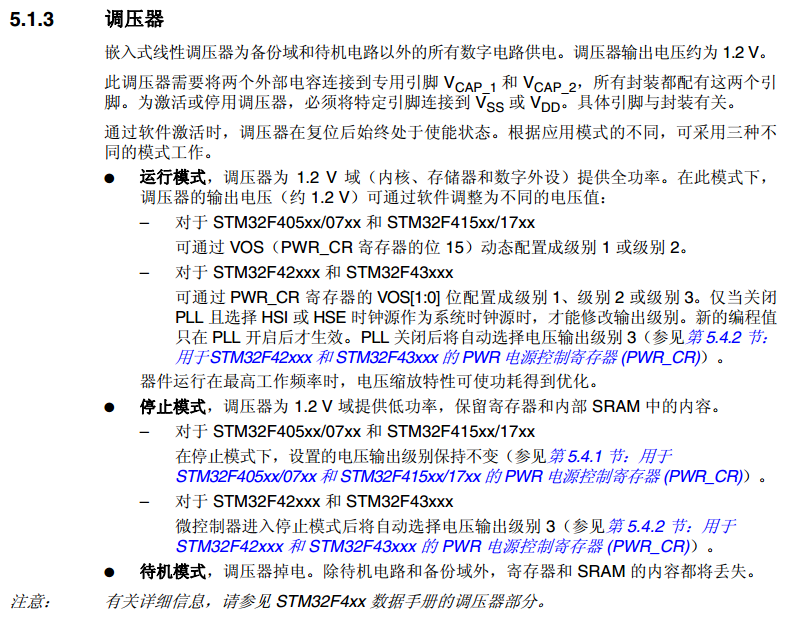

当关闭电压调节器会对PA0引脚造成影响,那么电压调节器有什么作用呢?M0090中是这么描述的:

以上就简单的根据手册对PDR进行了浅薄的探讨,等后面有了更深入的了解再更新!

以上就简单的根据手册对PDR进行了浅薄的探讨,等后面有了更深入的了解再更新!

PDR全称为power down reset,也就是掉电复位,RM0090参考手册上是这样描述的:

从图中可以看出,当PDR脚的电压低于1.8V时,芯片将会进入复位状态。

当PDR脚悬空时,在某种情况下是否会触发芯片复位? PDR脚具体怎么接还需要看另外一份文档,stm32f407_datasheet, Doc ID 022152 Rev2中相关的内容是这么描述的:

由上可见,stm32F4系列需要将PDR脚接到VDD来使能,掉电复位。

这上面的描述说明,要使能电压换监控器必须要保持PDR引脚为高,POR上电复位,PDR掉电复位和BOR欠压保护。

与PDR引脚关联的另一个功能是调压器,文档stm32f407_datasheet, Doc ID 022152 Rev2明确说明了LQFP114封装的芯片要使能电压调节器必须要将PDR拉高。

当关闭电压调节器会对PA0引脚造成影响,那么电压调节器有什么作用呢?M0090中是这么描述的:

以上就简单的根据手册对PDR进行了浅薄的探讨,等后面有了更深入的了解再更新!

以上就简单的根据手册对PDR进行了浅薄的探讨,等后面有了更深入的了解再更新!