在数字电路中,根据逻辑功能的不同而分为两大类,组合逻辑电路与时序逻辑电路。

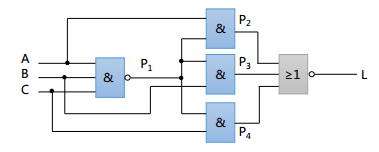

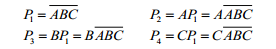

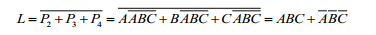

对于图中的电路,我们可以容易的转换成如下逻辑表达式: 经过计算,化简,最终便得出:

经过计算,化简,最终便得出:

然后画真值表。

然后画真值表。

最后,得出它的逻辑功能,只有当A、B、C这三个变量相同时,输出才是1。

以上电路转换成,Verilog代码来表示,则可能会是如下语句:

①针对wire型变量,

最后,得出它的逻辑功能,只有当A、B、C这三个变量相同时,输出才是1。

以上电路转换成,Verilog代码来表示,则可能会是如下语句:

①针对wire型变量,

而在FPGA的设计中,则是与之相反。我们要根据给定的逻辑功能,设计出一个能实现该功能的最简逻辑电路。

而在FPGA的设计中,则是与之相反。我们要根据给定的逻辑功能,设计出一个能实现该功能的最简逻辑电路。

我们将L=1的结果分别取出,并相或,即可得出函数表达式。

我们将L=1的结果分别取出,并相或,即可得出函数表达式。

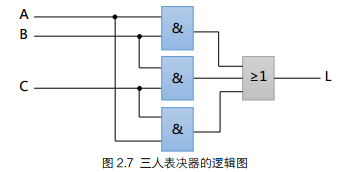

此时,如果我们化简此式,则可得到,

此时,如果我们化简此式,则可得到,

最后的逻辑图也就是,

最后的逻辑图也就是,

到了这里,你也许会发现,之前给出的Verilog代码而生成的RTL图和上面生成的逻辑图不一样,但是其实现的功能是一样的。

其实答案很简单,Verilog代码是行为级描述,而逻辑图是门级描述。

而我们需要弄清楚的是:

1、verilog建模方式分为:行为级和结构级,由行为级→结构级

2、行为级建模包括系统级、算法级和RTL级(程序员编写)

3、结构级也称为“门级和开关级”,包含模块实例和基本元件实例(软件完成)

这不禁引起我们的考虑,为什么要化简,同样功能的逻辑表达式,Verilog代码用到了加法器和比较器,而逻辑图只用到了简单的与、或门,因此,一个简洁的数字电路可以节省元器件、降低成本,减少元器件的故障率,提高电路的可靠性。

作为我们程序员虽然不能凡事都使用门级描述,因为这严重影响开发进度。而在使用行为级描述时,也需要尽量的简洁语言,这样会给我们自己带来更多便利。

到了这里,你也许会发现,之前给出的Verilog代码而生成的RTL图和上面生成的逻辑图不一样,但是其实现的功能是一样的。

其实答案很简单,Verilog代码是行为级描述,而逻辑图是门级描述。

而我们需要弄清楚的是:

1、verilog建模方式分为:行为级和结构级,由行为级→结构级

2、行为级建模包括系统级、算法级和RTL级(程序员编写)

3、结构级也称为“门级和开关级”,包含模块实例和基本元件实例(软件完成)

这不禁引起我们的考虑,为什么要化简,同样功能的逻辑表达式,Verilog代码用到了加法器和比较器,而逻辑图只用到了简单的与、或门,因此,一个简洁的数字电路可以节省元器件、降低成本,减少元器件的故障率,提高电路的可靠性。

作为我们程序员虽然不能凡事都使用门级描述,因为这严重影响开发进度。而在使用行为级描述时,也需要尽量的简洁语言,这样会给我们自己带来更多便利。

其波形图,

其波形图,

由上可以看出,当A经过一个非门时,会产生一小段时间的延时,而终于在L上出现一个窄脉冲信号,也就是毛刺。由于A与`A到达L输出端有先后,出现了竞争,而产生了毛刺,即出现了冒险。

到此,我们可以看到使用组合逻辑电路是有风险的,竞争与冒险,这个问题一直困扰着我们。

当然解决的办法也很简单,加一个时钟信号给它就行了,把它变成一个时序电路,让它随时钟信号有序的运行,只在某一个时刻有输入输出,这样就可以大大降低避免毛刺产生的几率。

由上可以看出,当A经过一个非门时,会产生一小段时间的延时,而终于在L上出现一个窄脉冲信号,也就是毛刺。由于A与`A到达L输出端有先后,出现了竞争,而产生了毛刺,即出现了冒险。

到此,我们可以看到使用组合逻辑电路是有风险的,竞争与冒险,这个问题一直困扰着我们。

当然解决的办法也很简单,加一个时钟信号给它就行了,把它变成一个时序电路,让它随时钟信号有序的运行,只在某一个时刻有输入输出,这样就可以大大降低避免毛刺产生的几率。

1、何为组合逻辑电路

我们只需铭记一点就是,这种电路的输出Y只与当时的输入X有关,而与之前的输入X’无关。所以这是一个可以随输入X的变化而瞬变输出Y的电路,如果用我们的Verilog代码来表示,则可能会出现在如下语句中: ①针对wire型变量,assign Y = X1 && X2;

②针对reg型变量,

always@(*)

begin

Y = X1 && X2;

end

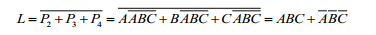

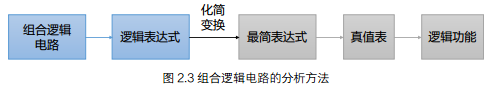

2、组合逻辑电路的分析方法

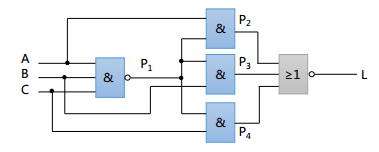

对于图中的电路,我们可以容易的转换成如下逻辑表达式:

经过计算,化简,最终便得出:

经过计算,化简,最终便得出:

然后画真值表。

然后画真值表。

最后,得出它的逻辑功能,只有当A、B、C这三个变量相同时,输出才是1。

以上电路转换成,Verilog代码来表示,则可能会是如下语句:

①针对wire型变量,

最后,得出它的逻辑功能,只有当A、B、C这三个变量相同时,输出才是1。

以上电路转换成,Verilog代码来表示,则可能会是如下语句:

①针对wire型变量,

assign L = ((A == B) && (A == C) && (B == C)) ? 1’b1 : 1’b0 ;

②针对reg型变量,

always@(*)

begin

if((A == B) && (A == C) && (B == C))

L = 1’b1;

else

L = 1’b0;

end

按照往常分析逻辑电路的顺序,如下:

而在FPGA的设计中,则是与之相反。我们要根据给定的逻辑功能,设计出一个能实现该功能的最简逻辑电路。

而在FPGA的设计中,则是与之相反。我们要根据给定的逻辑功能,设计出一个能实现该功能的最简逻辑电路。

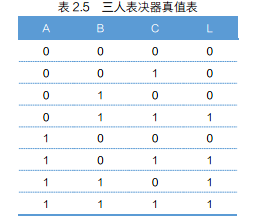

3、组合逻辑电路的设计方法

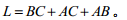

根据给定的逻辑功能,设计出一个三人表决器,即,至少两人赞同才为1。 Verilog代码来表示,则可能会是如下语句: ①针对wire型变量,assign L = ( A + B + C >= 3’d2) ? 1’b1 : 1’b0 ;

②针对reg型变量,

always@(*)

begin

if(A + B + C >= 3’d2)

L = 1’b1;

else

L = 1’b0;

end

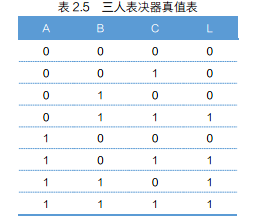

给出三人表决器的真值表:

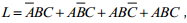

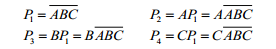

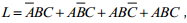

我们将L=1的结果分别取出,并相或,即可得出函数表达式。

我们将L=1的结果分别取出,并相或,即可得出函数表达式。

此时,如果我们化简此式,则可得到,

此时,如果我们化简此式,则可得到,

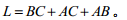

最后的逻辑图也就是,

最后的逻辑图也就是,

到了这里,你也许会发现,之前给出的Verilog代码而生成的RTL图和上面生成的逻辑图不一样,但是其实现的功能是一样的。

其实答案很简单,Verilog代码是行为级描述,而逻辑图是门级描述。

而我们需要弄清楚的是:

1、verilog建模方式分为:行为级和结构级,由行为级→结构级

2、行为级建模包括系统级、算法级和RTL级(程序员编写)

3、结构级也称为“门级和开关级”,包含模块实例和基本元件实例(软件完成)

这不禁引起我们的考虑,为什么要化简,同样功能的逻辑表达式,Verilog代码用到了加法器和比较器,而逻辑图只用到了简单的与、或门,因此,一个简洁的数字电路可以节省元器件、降低成本,减少元器件的故障率,提高电路的可靠性。

作为我们程序员虽然不能凡事都使用门级描述,因为这严重影响开发进度。而在使用行为级描述时,也需要尽量的简洁语言,这样会给我们自己带来更多便利。

到了这里,你也许会发现,之前给出的Verilog代码而生成的RTL图和上面生成的逻辑图不一样,但是其实现的功能是一样的。

其实答案很简单,Verilog代码是行为级描述,而逻辑图是门级描述。

而我们需要弄清楚的是:

1、verilog建模方式分为:行为级和结构级,由行为级→结构级

2、行为级建模包括系统级、算法级和RTL级(程序员编写)

3、结构级也称为“门级和开关级”,包含模块实例和基本元件实例(软件完成)

这不禁引起我们的考虑,为什么要化简,同样功能的逻辑表达式,Verilog代码用到了加法器和比较器,而逻辑图只用到了简单的与、或门,因此,一个简洁的数字电路可以节省元器件、降低成本,减少元器件的故障率,提高电路的可靠性。

作为我们程序员虽然不能凡事都使用门级描述,因为这严重影响开发进度。而在使用行为级描述时,也需要尽量的简洁语言,这样会给我们自己带来更多便利。

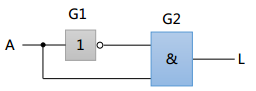

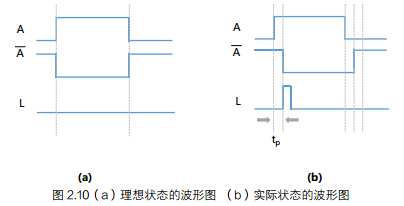

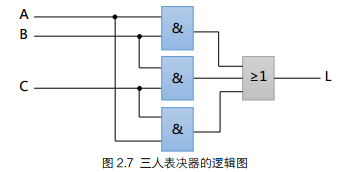

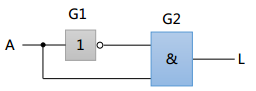

4、竞争与冒险

首先引入一个概念,在实际电路中,输入信号通过一个门电路然后输出,它总是要有传输时间的,那么就是,门电路的传输时间,即延迟时间。 在一个组合电路中,当某一个变量经过两条以上的路径到达输出端时,由于每条路径上的延迟时间的不同,到达终点的时间就会有先后,这一现象就是竞争。 其波形图,

其波形图,

由上可以看出,当A经过一个非门时,会产生一小段时间的延时,而终于在L上出现一个窄脉冲信号,也就是毛刺。由于A与`A到达L输出端有先后,出现了竞争,而产生了毛刺,即出现了冒险。

到此,我们可以看到使用组合逻辑电路是有风险的,竞争与冒险,这个问题一直困扰着我们。

当然解决的办法也很简单,加一个时钟信号给它就行了,把它变成一个时序电路,让它随时钟信号有序的运行,只在某一个时刻有输入输出,这样就可以大大降低避免毛刺产生的几率。

由上可以看出,当A经过一个非门时,会产生一小段时间的延时,而终于在L上出现一个窄脉冲信号,也就是毛刺。由于A与`A到达L输出端有先后,出现了竞争,而产生了毛刺,即出现了冒险。

到此,我们可以看到使用组合逻辑电路是有风险的,竞争与冒险,这个问题一直困扰着我们。

当然解决的办法也很简单,加一个时钟信号给它就行了,把它变成一个时序电路,让它随时钟信号有序的运行,只在某一个时刻有输入输出,这样就可以大大降低避免毛刺产生的几率。