偶然间在网上看到网友请教关于十进制进位的问题,具体问题见:

帮忙解释一个VHDL语言描述10进制cnt10的问题

其中讲述了,里面陈述了SIGNAL定义的中间变量Q在累加到8时就开始进位,而不是累加到9时进位,为此我设计了两个相似的语言程序对此进行理解:

程序一:

这是一个十进制计数器的VHDL设计,其实里面看不出SIGNAL和VARIABLE定义的变量有什么区别!

再来看下面的程序二:

这是一个十进制计数器的VHDL设计,其实里面看不出SIGNAL和VARIABLE定义的变量有什么区别!

再来看下面的程序二:

对比这两个程序,可以发现,程序一中就判断IF Q=9放在整个进程的开头,而在程序二中,时钟判断语句后面是Q<=Q+1;

显然在程序一中,SIGNAL的作用等于VARIABLE,而在两者不等价,因为,至始至终,OE都为地点平,如果两者等价的话,在Q=8的时候OE应该被拉高!

因此,可以发现,在程序二中,当时Q=8且时钟上升沿到来时,执行Q<=1+Q后,Q=9,但是程序并没有执行Q=9,那是因为此时Q依旧等于8,有点类似与C++中的Q++,当程序执行到END PROCESS后,上升沿结束,数据开始带入,但是在带入的过程中又执行了IF Q=9,但是没有执行OE<'1'.

这里讲的可能有点啰嗦,没有条理,这有一篇分析比较好的文章可以看看:

https://blog.csdn.net/qijitao/article/details/50629305

我一开始的想法是,在数据带入的过程中也不会执行IF Q=9,然而经过仿真发现,还是当Q=8时,就变回了0,且OE始终为低电平,具体为什么是这样无从考证,但是至少说明的SIGNAL是在END PROCESS后才会带入数据,以及需要注意其中的IF!

因此,如果你执着地想要把Q<=Q+1写在前面,则可以借鉴如下程序:

对比这两个程序,可以发现,程序一中就判断IF Q=9放在整个进程的开头,而在程序二中,时钟判断语句后面是Q<=Q+1;

显然在程序一中,SIGNAL的作用等于VARIABLE,而在两者不等价,因为,至始至终,OE都为地点平,如果两者等价的话,在Q=8的时候OE应该被拉高!

因此,可以发现,在程序二中,当时Q=8且时钟上升沿到来时,执行Q<=1+Q后,Q=9,但是程序并没有执行Q=9,那是因为此时Q依旧等于8,有点类似与C++中的Q++,当程序执行到END PROCESS后,上升沿结束,数据开始带入,但是在带入的过程中又执行了IF Q=9,但是没有执行OE<'1'.

这里讲的可能有点啰嗦,没有条理,这有一篇分析比较好的文章可以看看:

https://blog.csdn.net/qijitao/article/details/50629305

我一开始的想法是,在数据带入的过程中也不会执行IF Q=9,然而经过仿真发现,还是当Q=8时,就变回了0,且OE始终为低电平,具体为什么是这样无从考证,但是至少说明的SIGNAL是在END PROCESS后才会带入数据,以及需要注意其中的IF!

因此,如果你执着地想要把Q<=Q+1写在前面,则可以借鉴如下程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY cnt10a IS

PORT(

CLK:IN BIT;

OE:OUT BIT;

Y:OUT INTEGER RANGE 0 TO 10);

END CNT10a;

architecture RT of cnt10a is

signal Q:INTEGER RANGE 0 TO 10;

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK='1')THEN

IF Q=9 THEN

OE<='1';

Q<=0;

ELSE

Q<=Q+1;

OE<='0';

END IF;

END IF;

Y<=Q;

END PROCESS;

END RT;

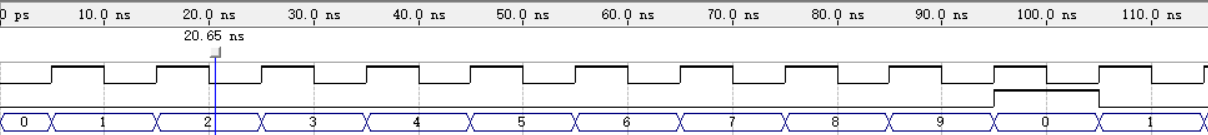

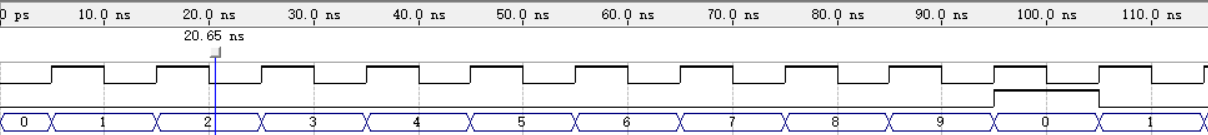

以下是仿真后的结果:

这是一个十进制计数器的VHDL设计,其实里面看不出SIGNAL和VARIABLE定义的变量有什么区别!

再来看下面的程序二:

这是一个十进制计数器的VHDL设计,其实里面看不出SIGNAL和VARIABLE定义的变量有什么区别!

再来看下面的程序二:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY cnt10 IS

PORT(

CLK:IN BIT;

OE:OUT BIT;

Y:OUT INTEGER RANGE 0 TO 9);

END CNT10;

architecture RT of cnt10 is

signal Q:INTEGER RANGE 0 TO 9;

BEGIN

PROCESS(CLK,Q)

BEGIN

IF(CLK'EVENT AND CLK='1')THEN

Q<=Q+1;

END IF;

IF Q=9 THEN

OE<='1';

Q<=0;

ELSE

OE<='0';

END IF;

END PROCESS;

Y<=Q;

END RT;

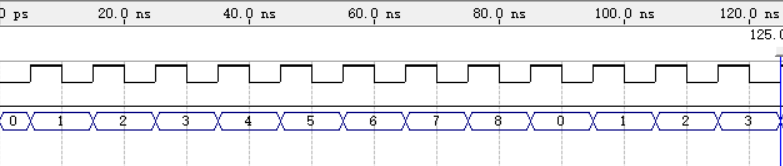

以下是执行仿真后的结果:

对比这两个程序,可以发现,程序一中就判断IF Q=9放在整个进程的开头,而在程序二中,时钟判断语句后面是Q<=Q+1;

显然在程序一中,SIGNAL的作用等于VARIABLE,而在两者不等价,因为,至始至终,OE都为地点平,如果两者等价的话,在Q=8的时候OE应该被拉高!

因此,可以发现,在程序二中,当时Q=8且时钟上升沿到来时,执行Q<=1+Q后,Q=9,但是程序并没有执行Q=9,那是因为此时Q依旧等于8,有点类似与C++中的Q++,当程序执行到END PROCESS后,上升沿结束,数据开始带入,但是在带入的过程中又执行了IF Q=9,但是没有执行OE<'1'.

这里讲的可能有点啰嗦,没有条理,这有一篇分析比较好的文章可以看看:

https://blog.csdn.net/qijitao/article/details/50629305

我一开始的想法是,在数据带入的过程中也不会执行IF Q=9,然而经过仿真发现,还是当Q=8时,就变回了0,且OE始终为低电平,具体为什么是这样无从考证,但是至少说明的SIGNAL是在END PROCESS后才会带入数据,以及需要注意其中的IF!

因此,如果你执着地想要把Q<=Q+1写在前面,则可以借鉴如下程序:

对比这两个程序,可以发现,程序一中就判断IF Q=9放在整个进程的开头,而在程序二中,时钟判断语句后面是Q<=Q+1;

显然在程序一中,SIGNAL的作用等于VARIABLE,而在两者不等价,因为,至始至终,OE都为地点平,如果两者等价的话,在Q=8的时候OE应该被拉高!

因此,可以发现,在程序二中,当时Q=8且时钟上升沿到来时,执行Q<=1+Q后,Q=9,但是程序并没有执行Q=9,那是因为此时Q依旧等于8,有点类似与C++中的Q++,当程序执行到END PROCESS后,上升沿结束,数据开始带入,但是在带入的过程中又执行了IF Q=9,但是没有执行OE<'1'.

这里讲的可能有点啰嗦,没有条理,这有一篇分析比较好的文章可以看看:

https://blog.csdn.net/qijitao/article/details/50629305

我一开始的想法是,在数据带入的过程中也不会执行IF Q=9,然而经过仿真发现,还是当Q=8时,就变回了0,且OE始终为低电平,具体为什么是这样无从考证,但是至少说明的SIGNAL是在END PROCESS后才会带入数据,以及需要注意其中的IF!

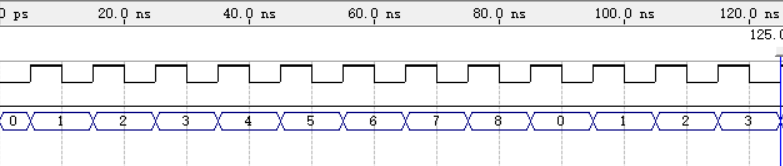

因此,如果你执着地想要把Q<=Q+1写在前面,则可以借鉴如下程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY cnt10 IS

PORT(

CLK:IN BIT;

OE:OUT BIT;

Y:OUT INTEGER RANGE 0 TO 9);

END CNT10;

architecture RT of cnt10 is

signal Q:INTEGER RANGE 0 TO 9;

BEGIN

PROCESS(CLK,Q)

BEGIN

IF(CLK'EVENT AND CLK='1')THEN

Q<=Q+1;

END IF;

IF Q=10 then

Q<=0;

END IF;

if (Q=0)THEN

OE<='1';

ELSE

OE<='0';

END IF;

Y<=Q;

END PROCESS;

END RT;

初学VHDL,不知道理解的对不对,如有错误,请予以指出,谢谢!