目录

前言

行为级描述

Verilog HDL设计代码为:

ISE综合

RTL Schematic

Technology Schematic

状态机描述状态转移图

Verilog HDL代码

测试文件

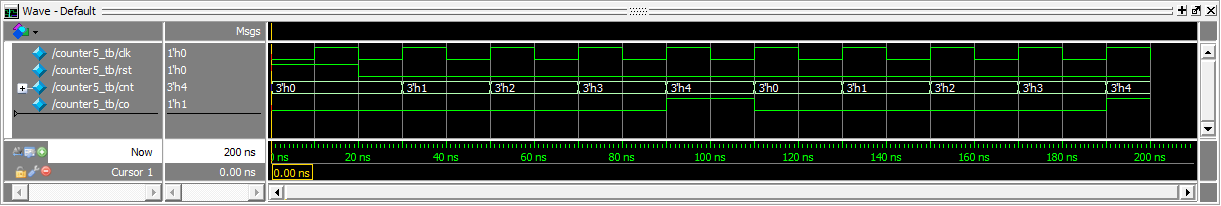

仿真波形

ISE综合

RTL Schematic

Technology Schematic

修正为同步复位

Verilog HDL语言描述

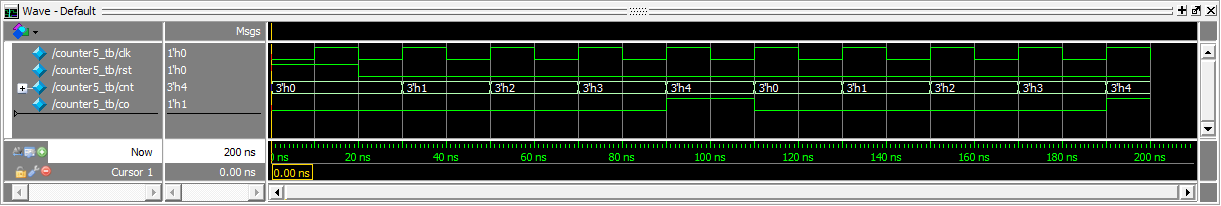

仿真波形图

ISE综合

RTL Schematic

Technology Schematic

结构性描述

简单的比较

展开后

展开后

展开后

展开后

注:用有限状态机这种描述方法中,出现了一系列的错误,这也是一个发现错误并解决的过程,解决问题的代价是很大的(时间的花费,心理的奔溃),但解决问题后的成就感是微妙的,问题见博文:Modelsim下进行功能仿真没问题,可是在ISE综合报错,如何解决?

注:用有限状态机这种描述方法中,出现了一系列的错误,这也是一个发现错误并解决的过程,解决问题的代价是很大的(时间的花费,心理的奔溃),但解决问题后的成就感是微妙的,问题见博文:Modelsim下进行功能仿真没问题,可是在ISE综合报错,如何解决?

有限状态机描述

有限状态机描述

直观上看的确如此,可是是不是感觉到很迷惑,这些RTL级元器件到底是什么?有什么功能?似乎看不懂综合出来的电路是什么意思,为了探讨这个问题,下篇博客再议。

写好了,我会附上链接。

直观上看的确如此,可是是不是感觉到很迷惑,这些RTL级元器件到底是什么?有什么功能?似乎看不懂综合出来的电路是什么意思,为了探讨这个问题,下篇博客再议。

写好了,我会附上链接。

前言

采用Verilog HDL对时序逻辑电路进行描述的方法有:状态转移图描述、结构性描述以及抽象性的行为描述。 下面以5进制同步加法计数器的Verilog HDL描述为例,对比不同的描述方式综合出来的RTL Schematic,看看有什么不同。行为级描述

首先采用电路的行为级描述方式。Verilog HDL设计代码为:

module counter5(clk, rst, cnt, co);

input clk;

input rst;

output co; //输出为进位

reg co;

output [2:0] cnt;

reg[2:0] cnt;

always@(posedge clk)

begin

if(rst)

begin

cnt <= 3'b000;

co <= 1'b0;

end

else if(cnt == 3'b100)

begin

cnt <= 3'b000;

co <= 1'b1;

end

else

begin

cnt <= cnt + 1'b1;

co <= 1'b0;

end

end

endmodule

ISE综合

RTL Schematic

展开后

展开后

Technology Schematic

状态机描述状态转移图

Verilog HDL代码

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 22:12:23 08/03/2018

// Design Name:

// Module Name: counter5

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module counter5(clk,rst, cnt, co);

input clk;

input rst;

output[2:0] cnt;

output co;

reg co;

reg[2:0] pre_state, next_state;

parameter s0 = 3'b000, s1 = 3'b001, s2 = 3'b010, s3 = 3'b011, s4 = 3'b100;

always@(posedge clk or posedge rst)

begin

if(rst)

begin

pre_state <= s0;

// co <= 1'b0;

end

else

begin

pre_state <= next_state;

end

end

always@(pre_state)

begin

case(pre_state)

s0:

begin

next_state = s1;

co = 1'b0;

end

s1:

begin

next_state = s2;

co = 1'b0;

end

s2:

begin

next_state = s3;

co = 1'b0;

end

s3:

begin

next_state = s4;

co = 1'b0;

end

s4:

begin

next_state = s0;

co = 1'b1;

end

default:

begin

next_state = s0;

co = 1'b0;

end

endcase

end

assign cnt = pre_state;

endmodule

测试文件

`timescale 1ns/1ps

module counter5_tb;

reg clk,rst;

wire[2:0] cnt;

wire co;

always

begin

#10 clk = ~clk;

end

initial

begin

clk = 1'b0;

rst = 1'b1;

#20 rst = 1'b0;

end

counter5 u1(.clk(clk), .rst(rst), .cnt(cnt), .co(co));

endmodule

仿真波形

ISE综合

RTL Schematic

展开后

展开后

Technology Schematic

修正为同步复位

Verilog HDL语言描述

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 22:12:23 08/03/2018

// Design Name:

// Module Name: counter5

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module counter5(clk,rst, cnt, co);

input clk;

input rst;

output[2:0] cnt;

output co;

reg co;

reg[2:0] pre_state, next_state;

parameter s0 = 3'b000, s1 = 3'b001, s2 = 3'b010, s3 = 3'b011, s4 = 3'b100;

always@(posedge clk )

begin

if(rst)

begin

pre_state <= s0;

// co <= 1'b0;

end

else

begin

pre_state <= next_state;

end

end

always@(pre_state)

begin

case(pre_state)

s0:

begin

next_state = s1;

co = 1'b0;

end

s1:

begin

next_state = s2;

co = 1'b0;

end

s2:

begin

next_state = s3;

co = 1'b0;

end

s3:

begin

next_state = s4;

co = 1'b0;

end

s4:

begin

next_state = s0;

co = 1'b1;

end

default:

begin

next_state = s0;

co = 1'b0;

end

endcase

end

assign cnt = pre_state;

endmodule

测试代码不变

省略

仿真波形图

ISE综合

RTL Schematic

Technology Schematic

注:用有限状态机这种描述方法中,出现了一系列的错误,这也是一个发现错误并解决的过程,解决问题的代价是很大的(时间的花费,心理的奔溃),但解决问题后的成就感是微妙的,问题见博文:Modelsim下进行功能仿真没问题,可是在ISE综合报错,如何解决?

注:用有限状态机这种描述方法中,出现了一系列的错误,这也是一个发现错误并解决的过程,解决问题的代价是很大的(时间的花费,心理的奔溃),但解决问题后的成就感是微妙的,问题见博文:Modelsim下进行功能仿真没问题,可是在ISE综合报错,如何解决?

结构性描述

其实还有一种描述方式,是结构性描述,但这种描述方式实在过于繁琐,例如本例如果采用结构性描述,就不得不画卡诺图,化简卡诺图,等等,真的很让人X疼,这不如让我用原理图来设计电路算了。 这里就不采用这种方式了,但这也不意味着结构性的描述方式一无是处,在有的场合还是需要的; 这三种描述方式有的时候可以混合使用,例如模60计数器的实现就可以采用模10计数器和模6计数器的级联来描述,见博客: 级联模60计数器(Verilog HDL语言描述)(仿真与综合) 这里的级联方式不就是一种结构性的描述吗? 而小的模块的描述则采用的是比价抽象的行为级描述方式。简单的比较

从RTL Schematic中可以看出,行为级描述方式和有限状态机描述方式综合出来的电路还是有很大不同的: 行为级描述的RTL Schematic 有限状态机描述

有限状态机描述

直观上看的确如此,可是是不是感觉到很迷惑,这些RTL级元器件到底是什么?有什么功能?似乎看不懂综合出来的电路是什么意思,为了探讨这个问题,下篇博客再议。

写好了,我会附上链接。

直观上看的确如此,可是是不是感觉到很迷惑,这些RTL级元器件到底是什么?有什么功能?似乎看不懂综合出来的电路是什么意思,为了探讨这个问题,下篇博客再议。

写好了,我会附上链接。