FPGA实验3:计数器、波形仿真、SignalTap

2019-04-14 08:22发布

生成海报

- 实验一:设计一个0-17的计数器,当计数值为17的时候,OV输出1,其他输出0,注意设定合理的信号位宽。

1、 例化的子模块代码

module cnt_0to17(

CLK ,

CNTVAL,

OV );

input CLK;

output [4:0] CNTVAL;

output OV;

reg [4:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(CNTVAL >= 17)

CNTVAL <= 0;

else

CNTVAL <= CNTVAL + 1'b1;

end

always @ (CNTVAL) begin

if(CNTVAL == 17)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule

2、原理图

3、RTL图

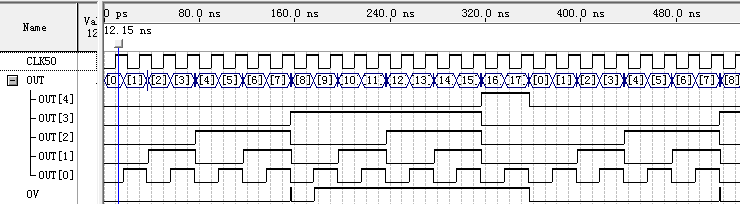

4、仿真波形

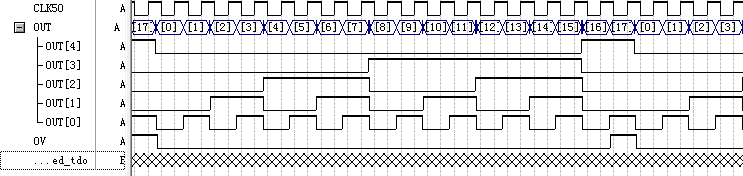

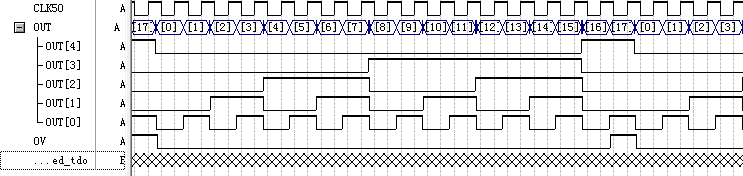

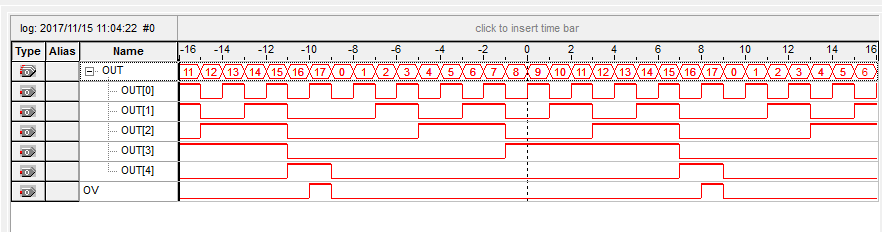

5、SignalTap验证波形

- 实验二:针对以上计数器,修改输出逻辑,当计数值为0-8时,OV输出0,9-17时OV输出1

1、 例化的子模块代码

module cnt_0to17(

CLK ,

CNTVAL,

OV );

input CLK;

output [4:0] CNTVAL;

output OV;

reg [4:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(CNTVAL >= 17)

CNTVAL <= 0;

else

CNTVAL <= CNTVAL + 1'b1;

end

always @ (CNTVAL) begin

if(CNTVAL >=9)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule

2、原理图、RTL图【同实验一】

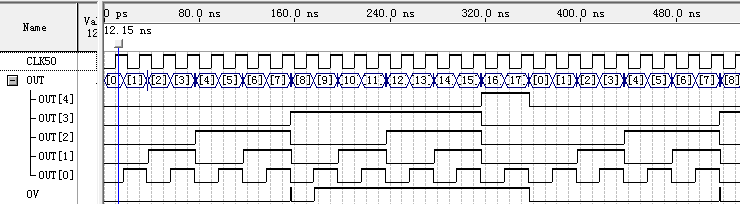

3、仿真波形

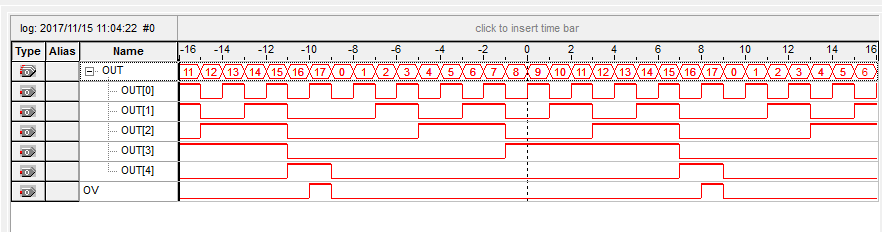

4、SignalTap验证波形

打开微信“扫一扫”,打开网页后点击屏幕右上角分享按钮

3、RTL图

3、RTL图

4、仿真波形

4、仿真波形

5、SignalTap验证波形

5、SignalTap验证波形

4、SignalTap验证波形

4、SignalTap验证波形