一、特性参数

1、12位高速AD 2、高达40MSPS的高速AD芯片 3、噪声小

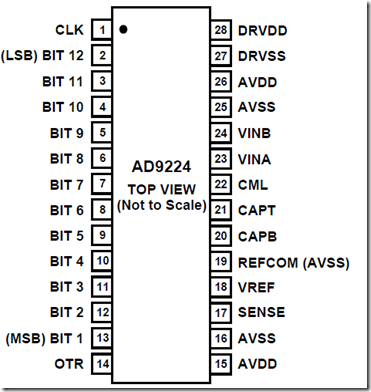

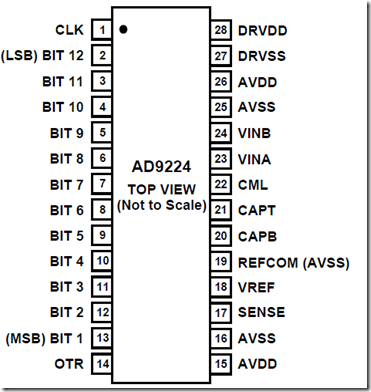

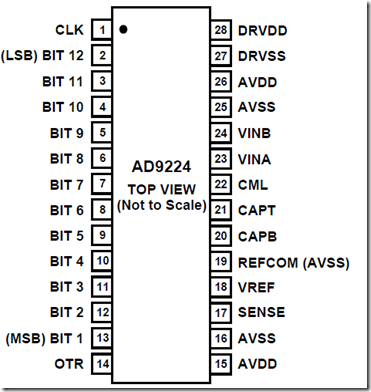

二、芯片管脚图

三、管脚功能说明

管脚名称 功能 CLK 参考时钟输入端 BIT12-1 数据输出端(1是低位,12是高位) OTR “1”超出参考电压范围,“0”表示不超出范围 AVDD 模拟电源输入端 +5V AVSS 模拟地 SENSE 参考源选择。“1”选择内部的1.225V参考源,否则使用外接参考源 VREF 参考源输入端 REFCOM 参考源地 CAPB 降噪端 CAPT 降噪端 CML Common-Mode Level (Midsupply) VINA 差分输入正端 VINB 差分输入负端 DRVSS 数字地 DRVDD 数字电源输入端,+5V或者+3V