今天我们从理论以及仿真的角度上分析一下电路的端接问题,其中可能有不当之处,也请各位指出。

本文讨论时所使用ADS以及cadence公司的sigxplorer进行仿真。 一、什么是端接,怎样的信号传输线需要端接

1.为什么需要端接

首先,我们需要讨论一下,信号传输的电路为什么需要端接,以及通过仿真得出一下怎样的传输线电路需要端接。

电路的端接是目的是为了保证信号传输过程中的完整性问题。由于驱动器的和接收器的阻抗不匹配,即使在点对点通过互连线传播的过程中,也容易出现一些干扰,具体的表现最多的就是“振铃现象”。产生振铃现象的原因先做简单的分析,驱动器输出阻抗比较低,一般CMOS电路的话输出阻抗大约在20欧姆左右,接收器输入阻抗一般都会较大,理想状态的输入阻抗是无穷大的。

由于阻抗的不匹配,在传输线的末端会发生反射系数ρ=1的全反射,然而这个反射信号在返回到输入端的时候,因为阻抗的不匹配再次产生反射系数为负值的反射,然后如此往复就会造成“振铃现象”的发生,从而造成信号完整性问题。

图1 此时我们选用一个幅值为3.3V,上升沿为0.833ns的驱动器进行仿真,其终端直接接接收器,得到如下的仿真图:

图2 可以从仿真结构中看到,信号的过冲的最大值已经可以达到了4.7V左右,并且其次高峰也超过了3.3V,这样的情况是很不理想的,所以正是由于这样的阻抗不匹配使得电路的端接尤为重要。下图三是我们ADS用一个上升沿为0的脉冲信号做的一个极限的仿真,图中结果是其输入端信号,能够更直观的看到反射现象对输入信号的影响。

图3 2.反射噪声与传输时延之间的关系

对于传输线足够端的信号线来说是可以不需要端接,但是多短的信号线是足够端呢,这个足够短是与谁相较足够短呢。其实这里也没有一个统一的标准,但我们可以通过仿真来客观的认识一下这个反射噪声与线长的关系。

首先对于一个信号来说,其衡量一个信号要求的很重要的一个指标是信号的上升时间,所以传输线的延迟应该是与信号的上升时间来比较,而不是信号的频率,这里我们先就此做一个仿真,仍旧去一个驱动电压为3.3V的驱动器,信号上升时间为0.833ns,我们分别输出不同频率的信号,50Mhz,100Mhz和150Mhz仿真其输入端的信号情况,得到图4,图5结果:

图4

图5 从上述仿真结果可以看出,上升沿相同是,不同频率信号的反射噪声是一样大的。

接下来我们将改变传输线的时间延迟来进行仿真,时间延迟分别为Tr/4、Tr/5、Tr/6,得到如下结果:

图6 由于我们实际工程中选用的芯片的驱动器可能不同,其仿真结果也会有差异,在此结果中可以看出当传输时间延迟控制在Tr/6时,反射噪声可以控制在10%以内。

二、端接的分类及其各自的优缺点

端接方式从大类上可以分为这么几类:串联端接,并联端接,RC端接。并联端接中一般又会有上拉,下拉以及戴维南端接,我们就以上所述的几种端接进行一些仿真,并尝试总结一下他的优缺点。

1.串联端接

图7 串联端接形式如图7所示,相信大家在熟悉不过,很多传输线都会在源端串一个33欧姆或者27欧姆的电阻,这种形式就是串联端接。这里笔者自己提出几个问题,串联电阻为什么要串在源端?为什么串的电阻是33欧姆左右?这样做对信号传输会有什么好处?

为什么要串在源端:这个问题很简单,我们进行端接的目的是防止信号的反射,源端输出电阻一般为10~30欧姆左右(CMOS),所以在源端串接电阻,当反射信号再次到达远端时,信号将不再发生反射(理想情况)。同时由于CMOS电路的输出电阻,也就同时要求了串接电阻的大小。

这样做对信号有什么好处呢,我们用仿真图来说明问题,该仿真条件与图4电路相同,但进行了33欧姆的源端串联端接,其仿真结果如下:

图8 可以看到,其振铃现象基本消失,只有上升沿和下降沿的过冲存在,过冲幅度也不大,可以保持在10%以内。

但同时我们也发现,下降沿的过冲现象要大于上升沿的过冲现象,这里就会有这样一个问题,CMOS驱动器的高电平输出电阻与低电平输出电阻大小是不同,低电平输出电阻要小于高电平输出电阻。所以当不同沿的过冲现象会有不同。

2.并联上拉端接 图9

图9

图10

图10

接收器阻抗接近于无穷大,所以当信号传输到末端时会有反射发生,并联50欧姆电阻,使接收端阻抗接近于50欧姆,则信号传输的末端时不发生反射。当传输电路输出低电平时,进行等效如上图10所示,R2为端接电阻,R1为驱动器低电平输入电阻,仿真并联上拉端接如下: 图11

图11

可以看到,信号的低电平被抬高。信号不再有明显的振铃现象。如果驱动器低电平输出电阻较大,低电平信号抬高超过接收器阈值的话,则不能得到低电平信号,这是上拉端接的局限性。 3.并联下拉端接 图12

该电路分析跟并联上拉端接相同,所以这里直接贴仿真图。

图12

该电路分析跟并联上拉端接相同,所以这里直接贴仿真图。

图13

图13

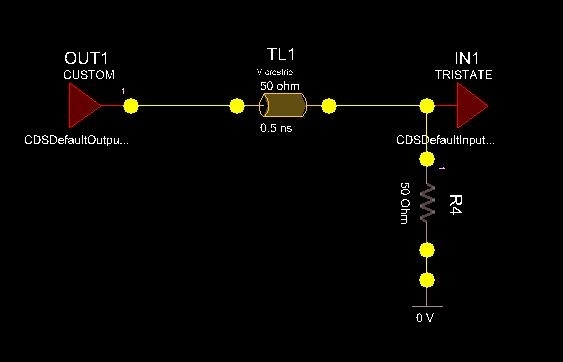

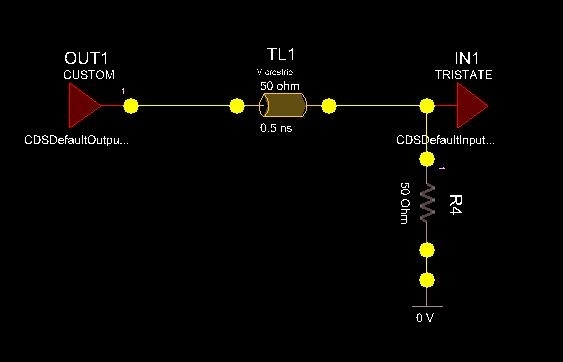

4.戴维南端接 图14

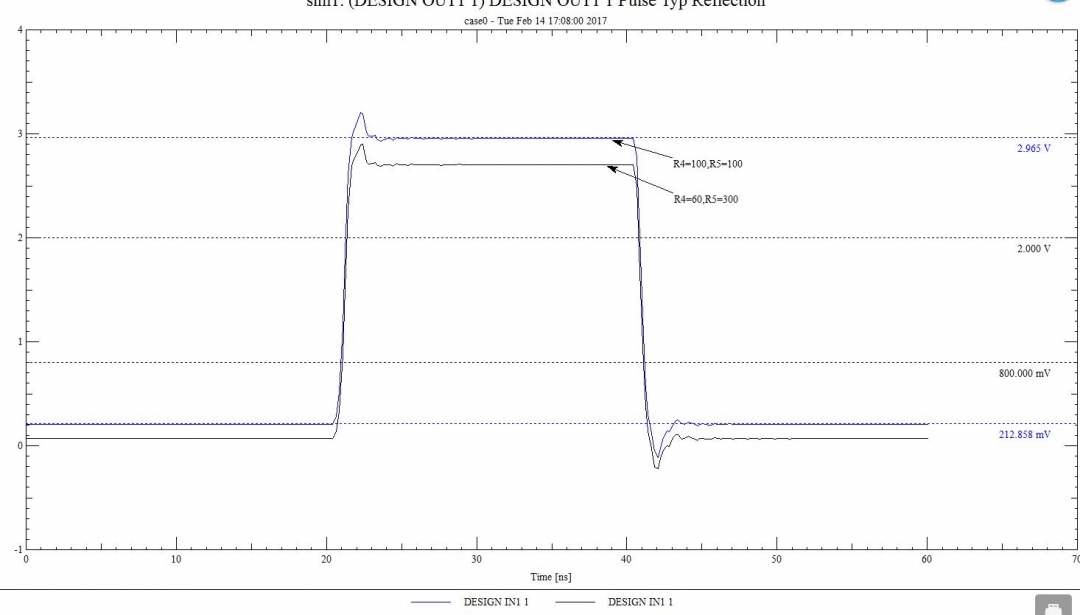

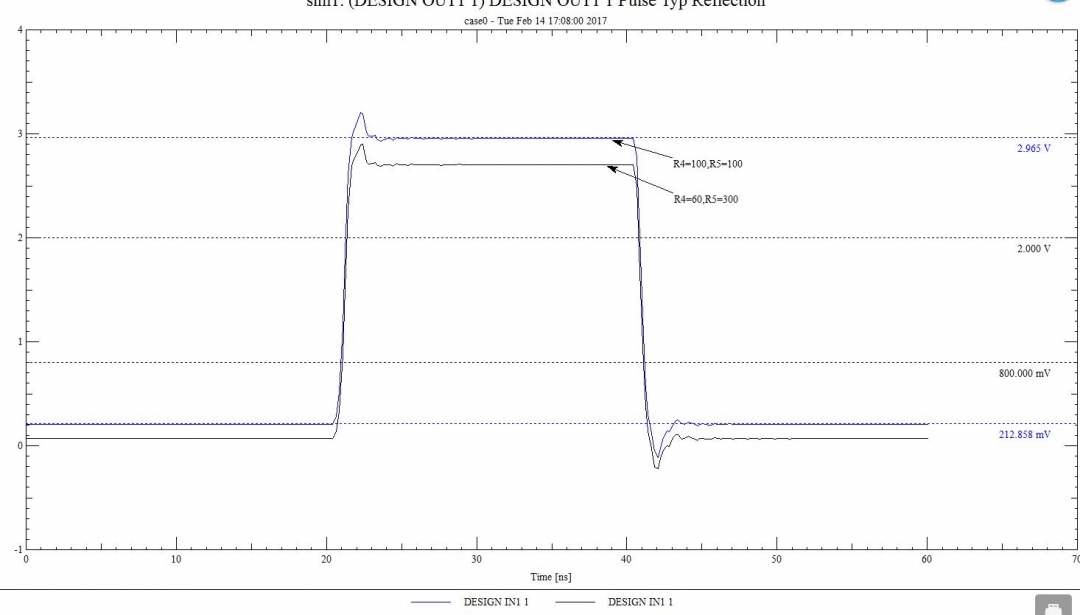

戴维南端接,即在终端加入高低两个信号并联,但末端阻抗仍需要满足50欧姆阻抗匹配,戴维南端接的好处可以通过并联电阻值的大小来改变信号的抬高或者拉低的值,从而得到符合阈值要求的信号。其中图15为并接两个100欧姆电阻的信号,图16为并接不同电阻值末端信号的比较。其整体趋势为R4增大,信号整体上升。

图14

戴维南端接,即在终端加入高低两个信号并联,但末端阻抗仍需要满足50欧姆阻抗匹配,戴维南端接的好处可以通过并联电阻值的大小来改变信号的抬高或者拉低的值,从而得到符合阈值要求的信号。其中图15为并接两个100欧姆电阻的信号,图16为并接不同电阻值末端信号的比较。其整体趋势为R4增大,信号整体上升。

图15

图15

图16 5.RC端接

本文讨论时所使用ADS以及cadence公司的sigxplorer进行仿真。 一、什么是端接,怎样的信号传输线需要端接

1.为什么需要端接

首先,我们需要讨论一下,信号传输的电路为什么需要端接,以及通过仿真得出一下怎样的传输线电路需要端接。

电路的端接是目的是为了保证信号传输过程中的完整性问题。由于驱动器的和接收器的阻抗不匹配,即使在点对点通过互连线传播的过程中,也容易出现一些干扰,具体的表现最多的就是“振铃现象”。产生振铃现象的原因先做简单的分析,驱动器输出阻抗比较低,一般CMOS电路的话输出阻抗大约在20欧姆左右,接收器输入阻抗一般都会较大,理想状态的输入阻抗是无穷大的。

由于阻抗的不匹配,在传输线的末端会发生反射系数ρ=1的全反射,然而这个反射信号在返回到输入端的时候,因为阻抗的不匹配再次产生反射系数为负值的反射,然后如此往复就会造成“振铃现象”的发生,从而造成信号完整性问题。

图1 此时我们选用一个幅值为3.3V,上升沿为0.833ns的驱动器进行仿真,其终端直接接接收器,得到如下的仿真图:

图2 可以从仿真结构中看到,信号的过冲的最大值已经可以达到了4.7V左右,并且其次高峰也超过了3.3V,这样的情况是很不理想的,所以正是由于这样的阻抗不匹配使得电路的端接尤为重要。下图三是我们ADS用一个上升沿为0的脉冲信号做的一个极限的仿真,图中结果是其输入端信号,能够更直观的看到反射现象对输入信号的影响。

图3 2.反射噪声与传输时延之间的关系

对于传输线足够端的信号线来说是可以不需要端接,但是多短的信号线是足够端呢,这个足够短是与谁相较足够短呢。其实这里也没有一个统一的标准,但我们可以通过仿真来客观的认识一下这个反射噪声与线长的关系。

首先对于一个信号来说,其衡量一个信号要求的很重要的一个指标是信号的上升时间,所以传输线的延迟应该是与信号的上升时间来比较,而不是信号的频率,这里我们先就此做一个仿真,仍旧去一个驱动电压为3.3V的驱动器,信号上升时间为0.833ns,我们分别输出不同频率的信号,50Mhz,100Mhz和150Mhz仿真其输入端的信号情况,得到图4,图5结果:

图4

图5 从上述仿真结果可以看出,上升沿相同是,不同频率信号的反射噪声是一样大的。

接下来我们将改变传输线的时间延迟来进行仿真,时间延迟分别为Tr/4、Tr/5、Tr/6,得到如下结果:

图6 由于我们实际工程中选用的芯片的驱动器可能不同,其仿真结果也会有差异,在此结果中可以看出当传输时间延迟控制在Tr/6时,反射噪声可以控制在10%以内。

二、端接的分类及其各自的优缺点

端接方式从大类上可以分为这么几类:串联端接,并联端接,RC端接。并联端接中一般又会有上拉,下拉以及戴维南端接,我们就以上所述的几种端接进行一些仿真,并尝试总结一下他的优缺点。

1.串联端接

图7 串联端接形式如图7所示,相信大家在熟悉不过,很多传输线都会在源端串一个33欧姆或者27欧姆的电阻,这种形式就是串联端接。这里笔者自己提出几个问题,串联电阻为什么要串在源端?为什么串的电阻是33欧姆左右?这样做对信号传输会有什么好处?

为什么要串在源端:这个问题很简单,我们进行端接的目的是防止信号的反射,源端输出电阻一般为10~30欧姆左右(CMOS),所以在源端串接电阻,当反射信号再次到达远端时,信号将不再发生反射(理想情况)。同时由于CMOS电路的输出电阻,也就同时要求了串接电阻的大小。

这样做对信号有什么好处呢,我们用仿真图来说明问题,该仿真条件与图4电路相同,但进行了33欧姆的源端串联端接,其仿真结果如下:

图8 可以看到,其振铃现象基本消失,只有上升沿和下降沿的过冲存在,过冲幅度也不大,可以保持在10%以内。

但同时我们也发现,下降沿的过冲现象要大于上升沿的过冲现象,这里就会有这样一个问题,CMOS驱动器的高电平输出电阻与低电平输出电阻大小是不同,低电平输出电阻要小于高电平输出电阻。所以当不同沿的过冲现象会有不同。

2.并联上拉端接

图9

图9

图10

图10接收器阻抗接近于无穷大,所以当信号传输到末端时会有反射发生,并联50欧姆电阻,使接收端阻抗接近于50欧姆,则信号传输的末端时不发生反射。当传输电路输出低电平时,进行等效如上图10所示,R2为端接电阻,R1为驱动器低电平输入电阻,仿真并联上拉端接如下:

图11

图11可以看到,信号的低电平被抬高。信号不再有明显的振铃现象。如果驱动器低电平输出电阻较大,低电平信号抬高超过接收器阈值的话,则不能得到低电平信号,这是上拉端接的局限性。 3.并联下拉端接

图12

该电路分析跟并联上拉端接相同,所以这里直接贴仿真图。

图12

该电路分析跟并联上拉端接相同,所以这里直接贴仿真图。

图13

图134.戴维南端接

图14

戴维南端接,即在终端加入高低两个信号并联,但末端阻抗仍需要满足50欧姆阻抗匹配,戴维南端接的好处可以通过并联电阻值的大小来改变信号的抬高或者拉低的值,从而得到符合阈值要求的信号。其中图15为并接两个100欧姆电阻的信号,图16为并接不同电阻值末端信号的比较。其整体趋势为R4增大,信号整体上升。

图14

戴维南端接,即在终端加入高低两个信号并联,但末端阻抗仍需要满足50欧姆阻抗匹配,戴维南端接的好处可以通过并联电阻值的大小来改变信号的抬高或者拉低的值,从而得到符合阈值要求的信号。其中图15为并接两个100欧姆电阻的信号,图16为并接不同电阻值末端信号的比较。其整体趋势为R4增大,信号整体上升。

图15

图15

图16 5.RC端接