计数器模块

2019-04-14 15:25发布

生成海报

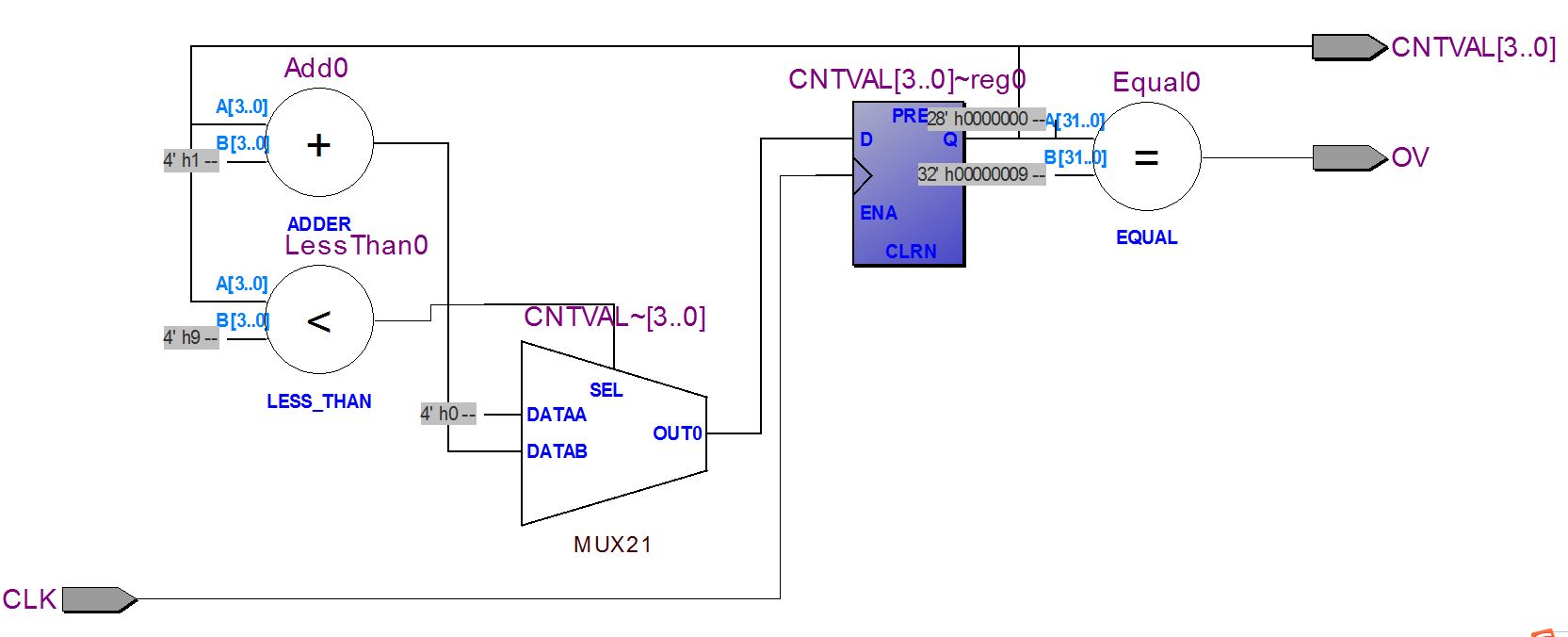

简单的0-9计数器

- RTL:

- 代码片:

module cnt_0to9(

CLK ,

CNTVAL,

OV );

parameter CNTVAL_MAX = 9 ;

parameter CNTVAL_WL = 4 ;

input CLK;

output [CNTVAL_WL-1:0] CNTVAL;

output OV;

reg [CNTVAL_WL-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(CNTVAL < CNTVAL_MAX)

CNTVAL <= CNTVAL + 1'b1;

else

CNTVAL <= 0;

end

always @ (CNTVAL) begin

if(CNTVAL == CNTVAL_MAX)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule

时间基准电路 和 带使能的多周期计数器

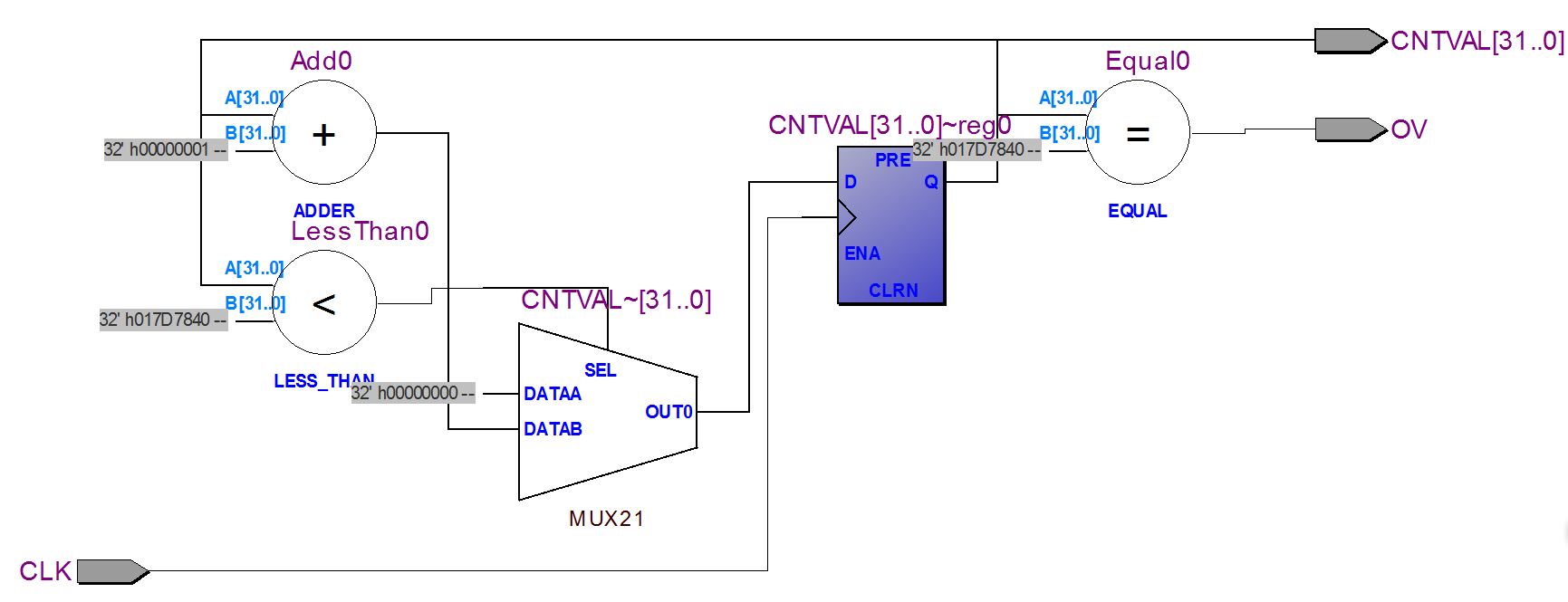

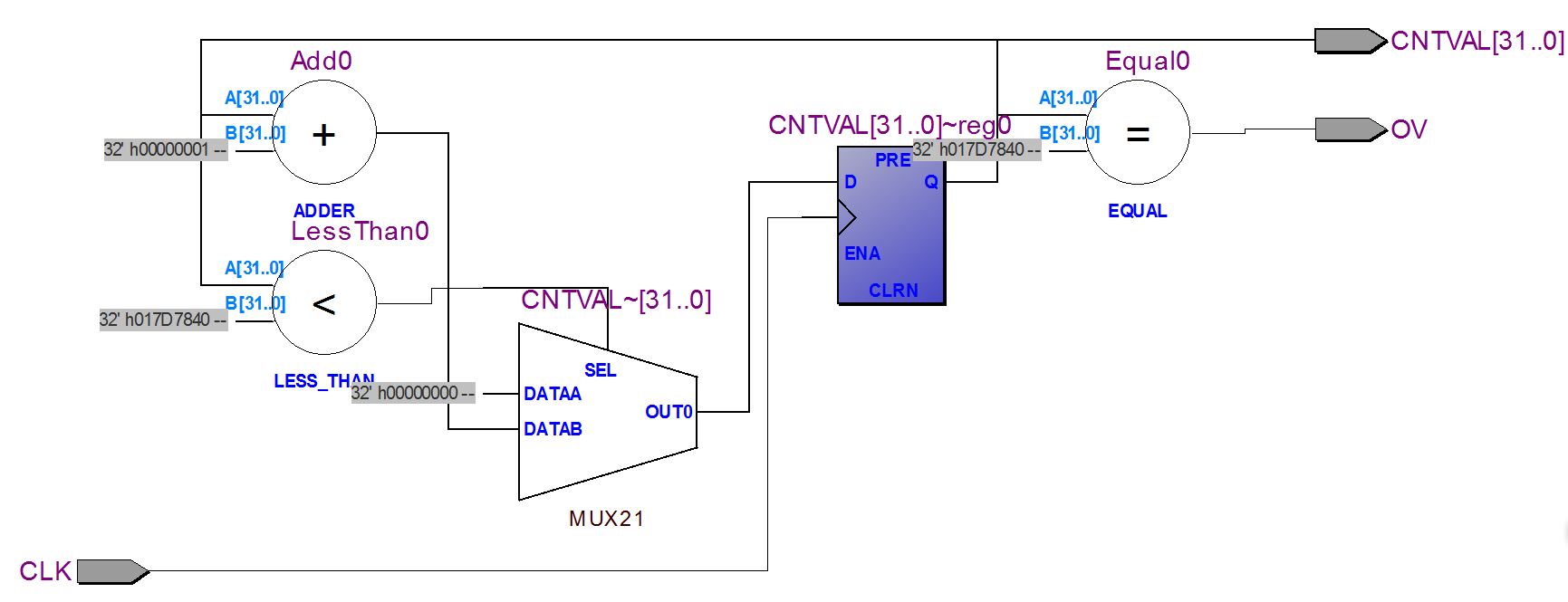

- 时间基准电路

- RTL:

- 代码片:

module cnt_sync(

CLK ,

CNTVAL,

OV );

input CLK;

output [32-1:0] CNTVAL;

output OV;

parameter MAX_VAL = 25_000_000;

reg [32-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(CNTVAL < MAX_VAL)

CNTVAL <= CNTVAL + 1'b1;

else

CNTVAL <= 0;

end

always @ (CNTVAL) begin

if(CNTVAL == MAX_VAL)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule

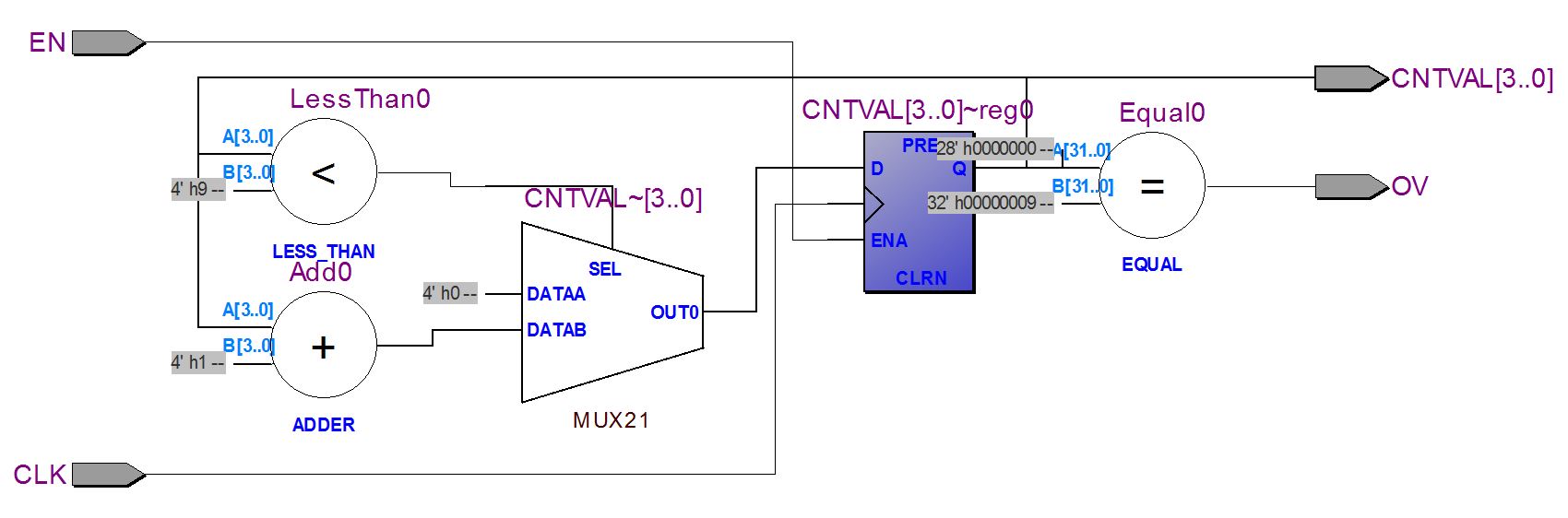

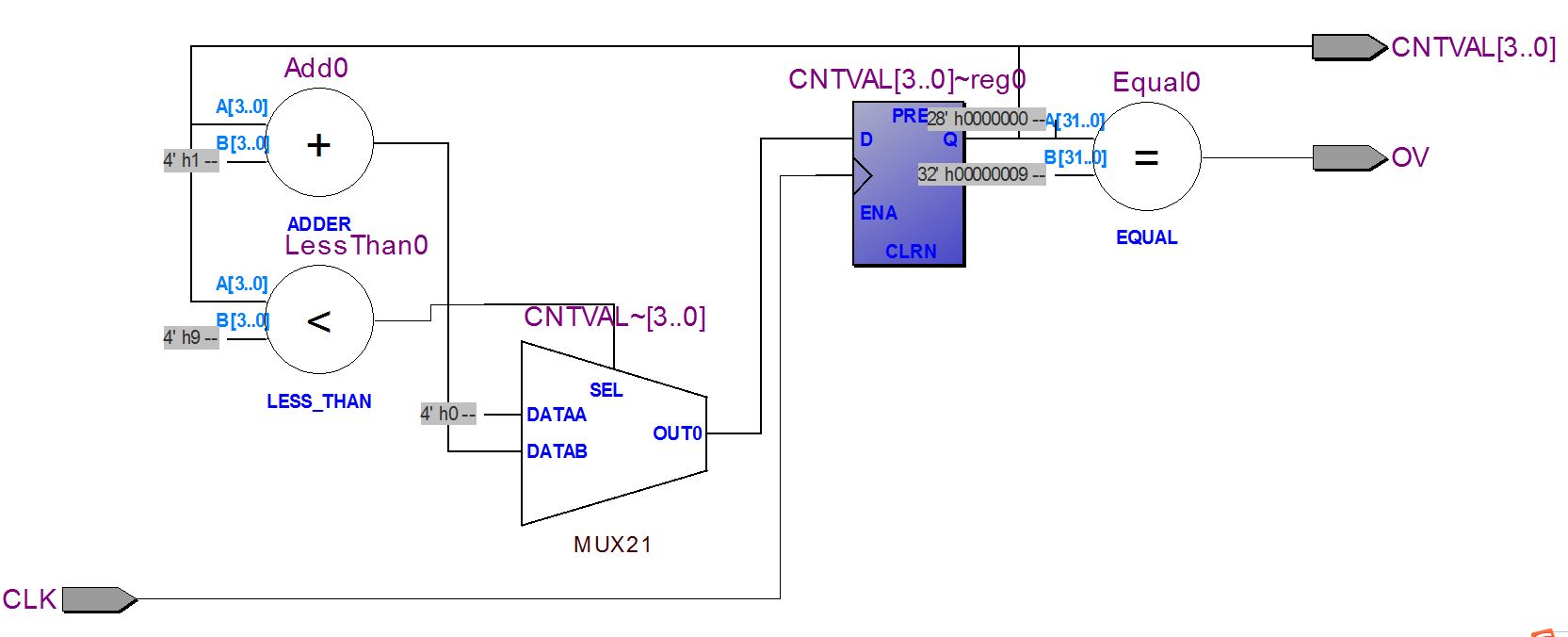

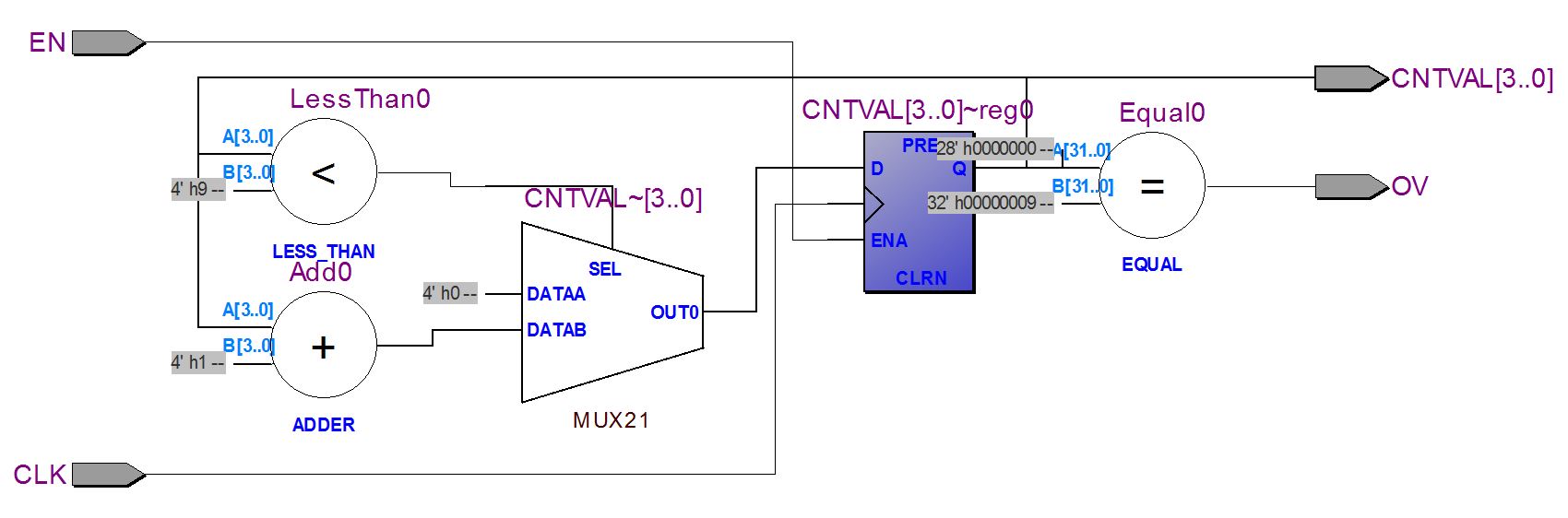

- 带使能的多周期计数器

- RTL:

- 代码片:

module cnt_en_0to9(

CLK ,

CNTVAL,

EN ,

OV );

input CLK;

input EN;

output [4-1:0] CNTVAL;

output OV;

reg [4-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(EN) begin

if(CNTVAL < 9)

CNTVAL <= CNTVAL + 1'b1;

else

CNTVAL <= 0;

end

else

CNTVAL <= CNTVAL ;

end

always @ (CNTVAL) begin

if(CNTVAL == 9)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule

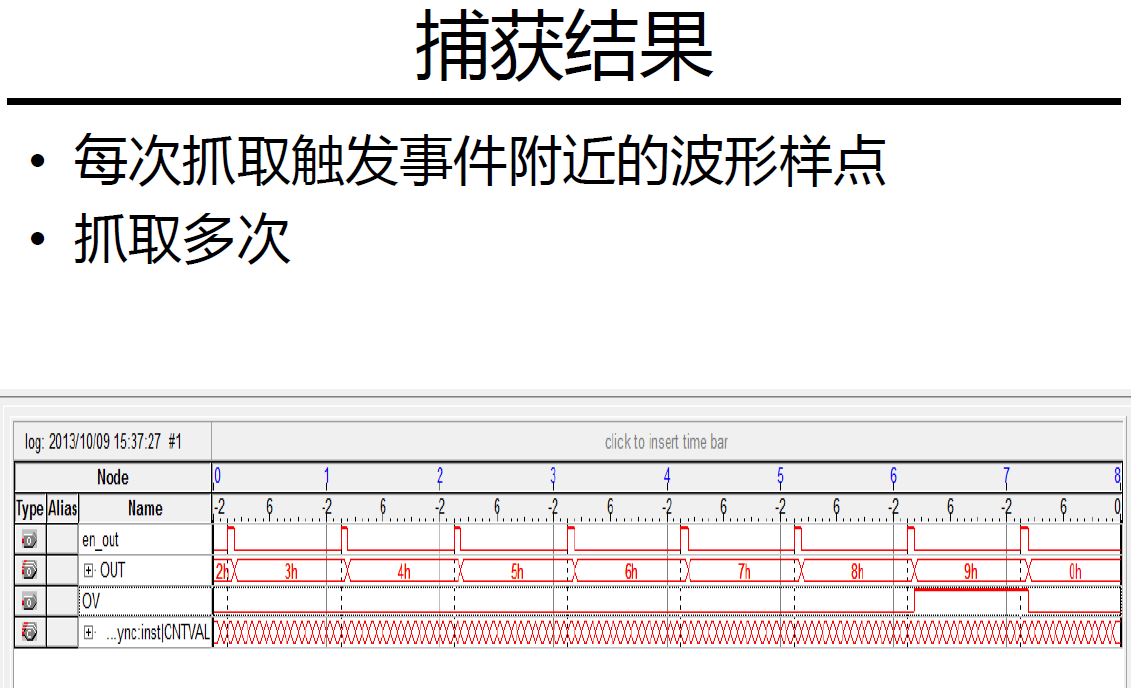

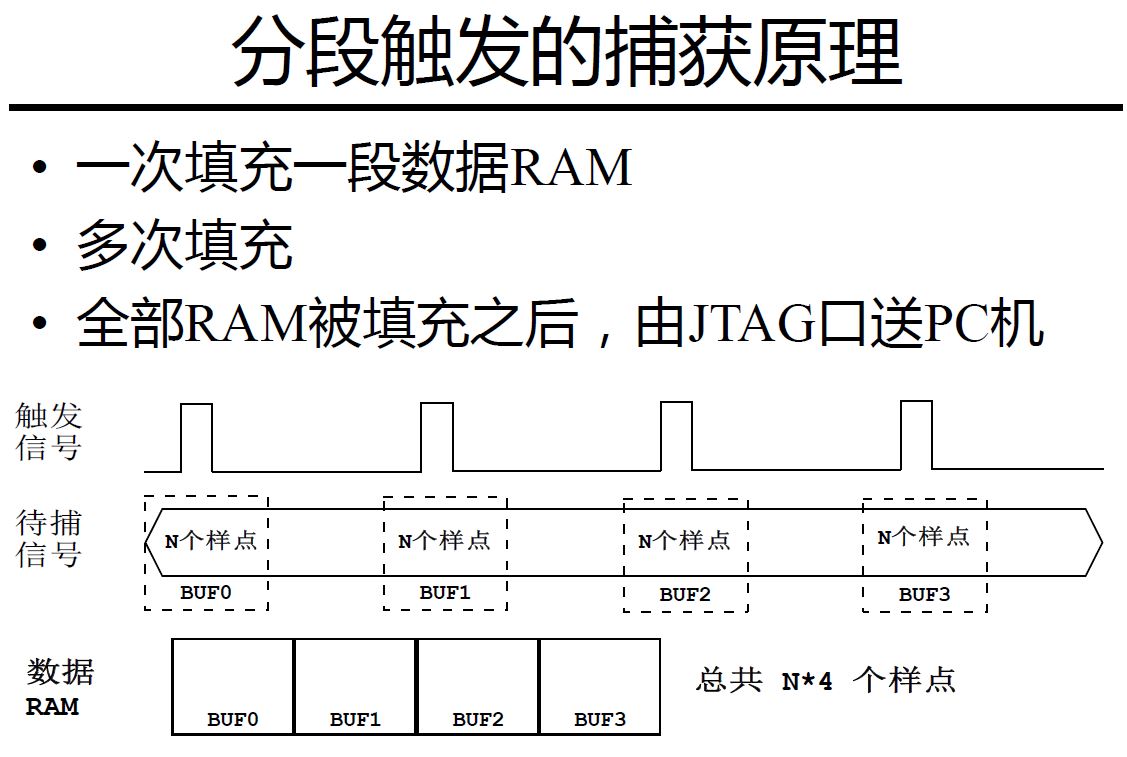

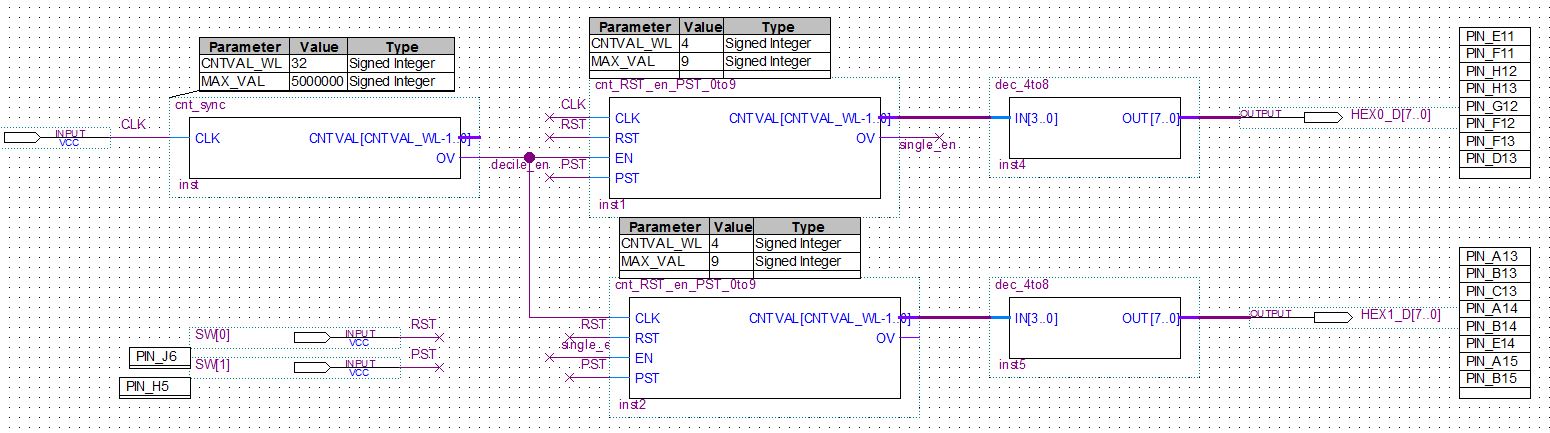

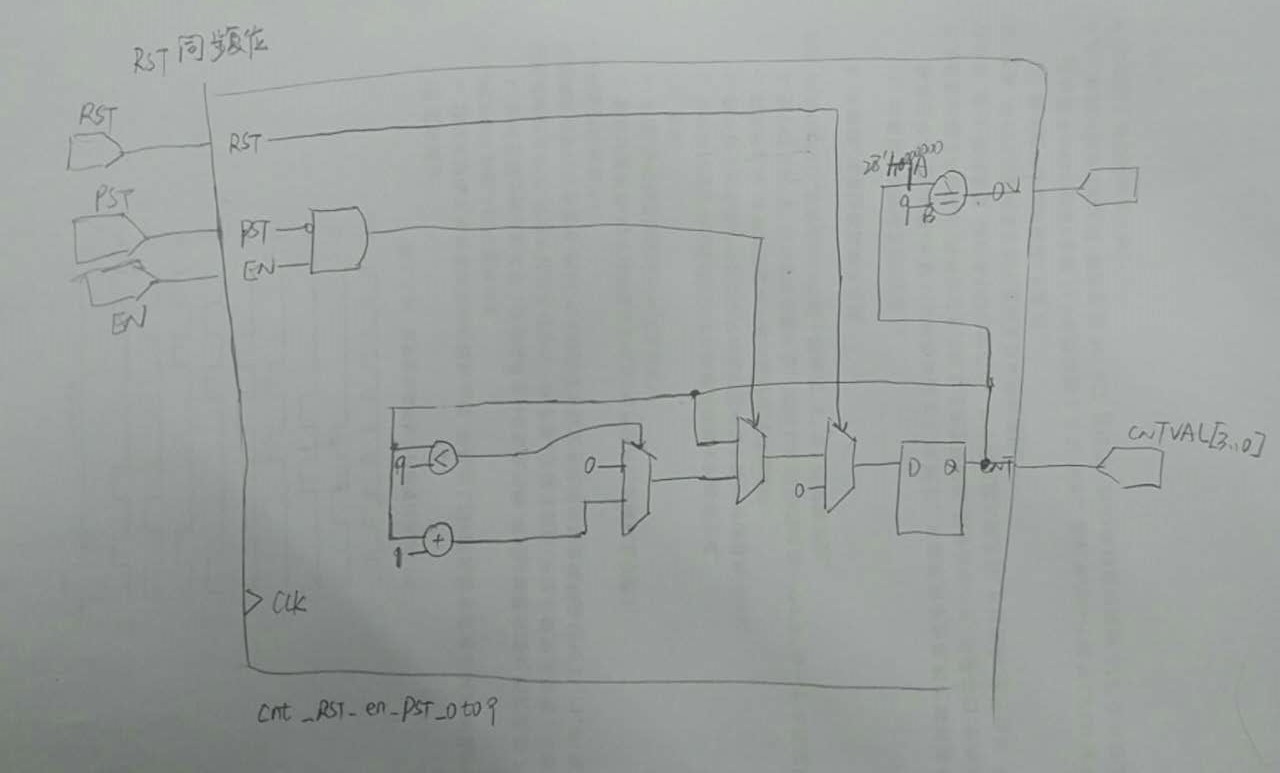

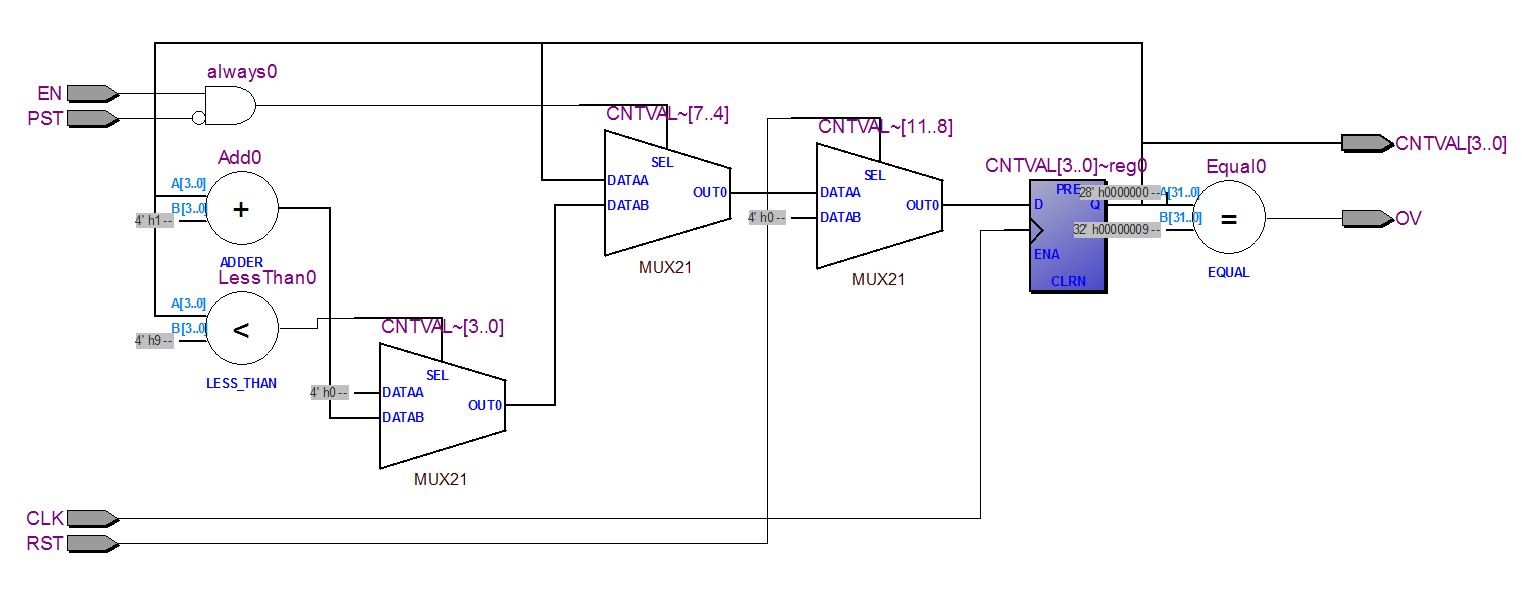

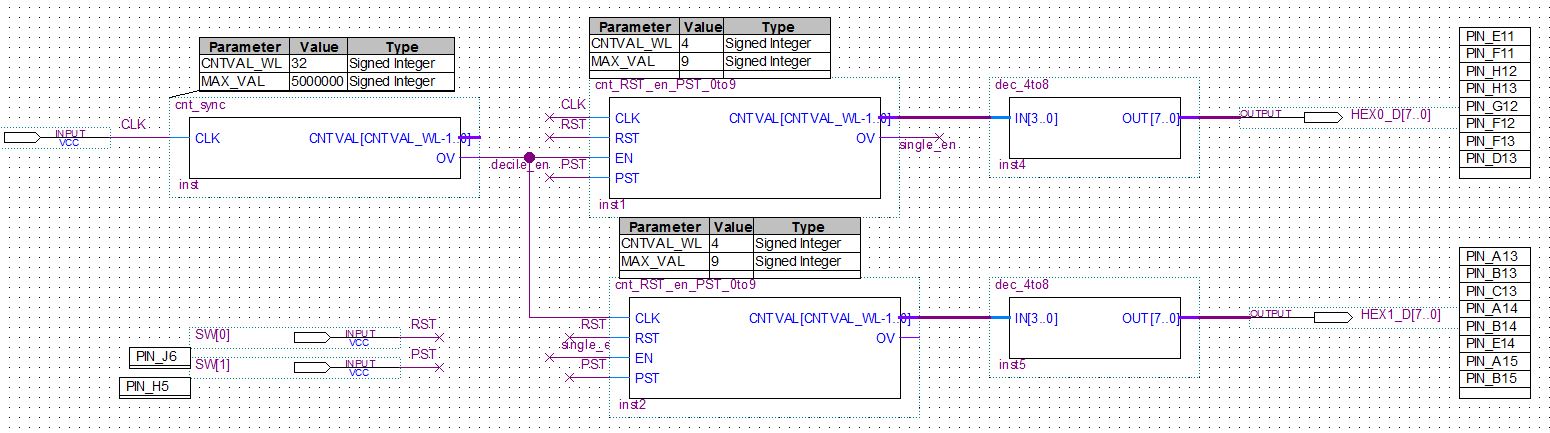

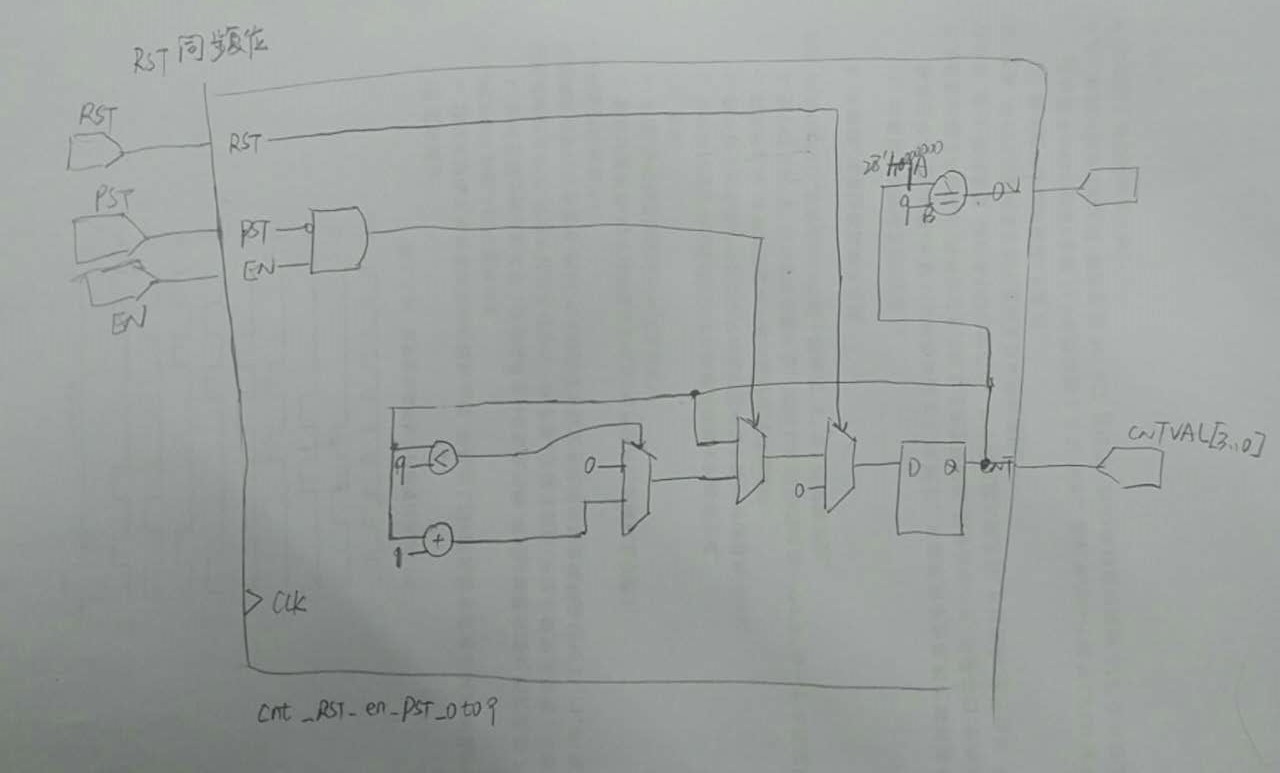

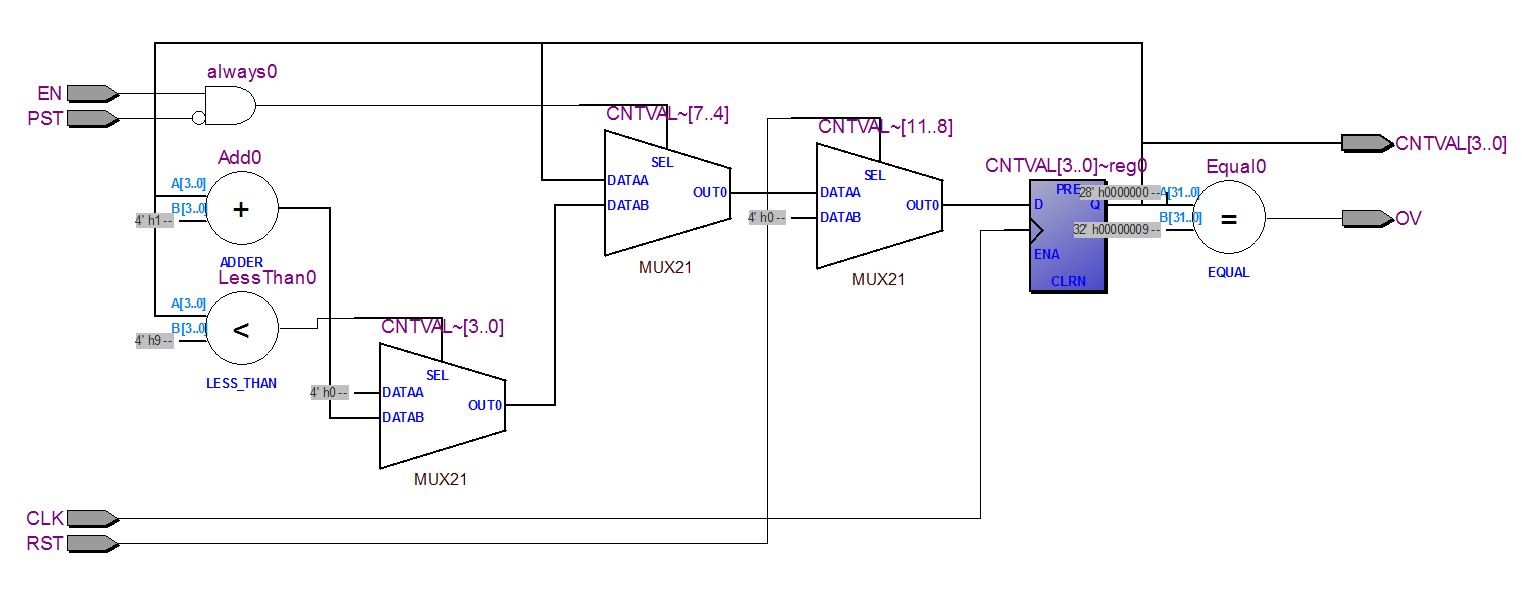

带清零、暂停功能的0-9.9s的计时秒表

- 原理图

- 代码片(RST同步复位)

module cnt_RST_en_PST_0to9(

CLK ,

CNTVAL,

RST ,

EN ,

PST ,

OV );

parameter CNTVAL_WL = 4;

parameter MAX_VAL = 9;

input CLK , RST , EN , PST ;

output [CNTVAL_WL-1:0] CNTVAL;

output OV;

reg [CNTVAL_WL-1:0] CNTVAL;

reg OV;

always @ (posedge CLK) begin

if(RST)begin

CNTVAL <= 0 ;

end

else begin

if(EN&&!PST) begin

if(CNTVAL < 9)

CNTVAL <= CNTVAL + 1'b1;

else

CNTVAL <= 0;

end

else

CNTVAL <= CNTVAL ;

end

end

always @ (CNTVAL) begin

if(CNTVAL == MAX_VAL)

OV = 1'b1;

else

OV = 1'b0;

end

endmodule

- 手绘RTL

- 生成RTL

打开微信“扫一扫”,打开网页后点击屏幕右上角分享按钮