T2080复位时序分析

1、T2080简介

T2080具有四个双线程内核,总共八个线程。(双线程:在CPU上,双线程指的是一个CPU在物理上虚拟为两个CPU,提升了程序运行效率)。该芯片可用于数据中心,WAN优化控制器,应用交付控制器,路由器,交换机,网关,应用和存储服务器以及通用嵌入式计算系统中的组合控制,数据路径和应用层处理。芯片框图如下:

单核可达1.8G主频,DDR3最高可达1866MHz,两个USB2.0控制器,SERDES可用来PCIE3.0、PCIE2.0、SRIO、SATA2.0及以太网。

2、芯片复位信号

上电复位(PORESET_B置位)和使用复位配置字(RCW)功能期间,通过复位配置信号选择配置模式。PORESET_B:上电复位信号,复位期间使芯片中止所有当前的内部和外部事务,并将所有寄存器设置为其默认值。

HRESET_B:硬件复位,上电复位初期作为输出,而后变为输入。

RESET_REQ_B:复位请求,触发后直到芯片被复位才正常状态。

CKSTP_OUT_B:低有效,触发后直到芯片被复位才正常状态。

3、上电复位时序

上电复位PORESET_B拉低后,芯片开始进入全复位过程及RCW(复位配置模式)进程。复位和RCW配置时间取决于配置源和SYSCLK频率。首先,对外部配置引脚进行采样来决定配置源。再开始加载复位配置字。系统PLL开始锁定,一旦PLL锁定并加载RCW数据,器件就会释放HRESET_B(不是RCW加载完成后拉高,同步进行),并且时钟单元开始在整个器件中分配PLL输出。而后芯片启动。具体时序如下:① 、PORESET_B触发(低电平)使所有寄存器初始化为默认状态,大多I/O

驱动器被释放为高阻抗(某些时钟,时钟使能,系统控制信号有效)。JTAG可独立触发PORESET_B及TRST_B信号以完全控制芯片。如果不使用JTAG接口,建议将PORESET_B及TRST_B连接在一起。

② 、系统切换SYSCLK,PLL以旁路模式运行,开始驱动HRESET_B

③、PORESET_B拉低一段时间后,开始对配置引脚进行采样,确定RCW源并读取预引导加载程,预引导加载程序(PBL)开始从cfg_rcw_src [0:n]配置输入指定的接口加载RCW数据,并将该64字节数据存储到设备配置块中的RCWSR寄存器。。

③ 、芯片启动

④、系统时钟开始锁定,等待预引导加载程序(PBL)完成,完成后切换为PLL输出驱动,而后停止驱动HRESET_B

T2080上电复位时序图

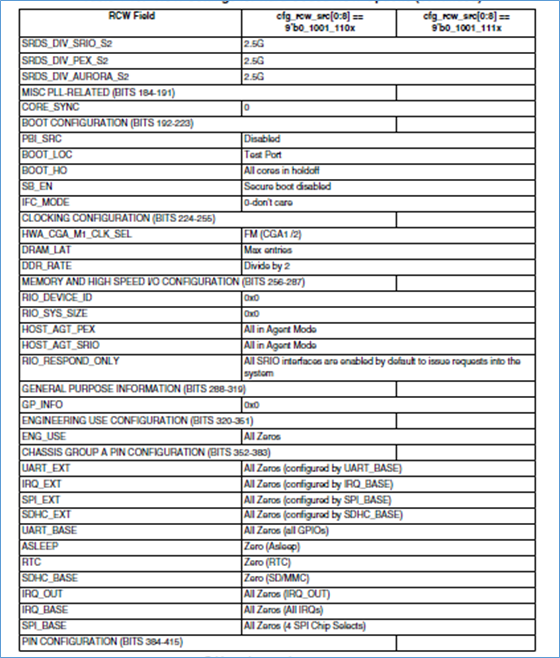

4、上电配置信号(RCW)

所有上电配置信号均存在内部上拉电阻,如果设置的状态为一,则不需要新增上拉电阻。复位配置字可通过IIC、SPI、NOR FLASH、NAND FLASH、SD卡中进行加载。如果无法通过上述接口进行加载,也可通过硬件进行配置,使用硬件进行配置时,上电期间有如下限制:①不能启动DDR控制器;②SERDES不可用;③根据SYSCLK及DDRCLK选择相应配置。在RCW加载成功后,可启用DDR及SERDES两功能。硬件RCW加载完成后,内核处于禁止引导状态,通过JTAG将RCW写入相应的存储器内。硬件配置如下:

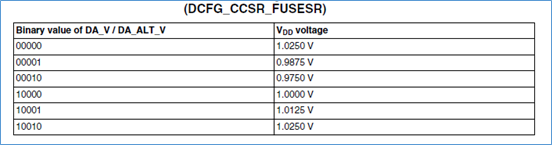

5、VID(Voltage ID)

为了以最小的漏电流保证最大性能,需要选择最佳电压电平。芯片实现不同主频时所需的电压不同,通过器件配置模块(DCFG_FUSESR)中的熔丝状态寄存器访问VID值。使用此功能时,通过调节系统电压使之达到合适的电压值。首次上电,其电压需为默认值1.025V,上电初期,软件读取DCFG_FUSESR中的值,并将该值转换为命令序列,该序列将为调节器编程新的电压值。注:过快的改变电压值将导致芯片故障或关机,应选用延迟时间可编程的电源。