引言

Octopus System中最难搞定的估计就是camera模块和VGA模块了。“明知山有虎,偏向虎山行”。“FFT计划”就拿这两个模块开刀。本小节将搭建一个RTL测试系统,来对这两个模块进行RTL的测试与验证。1,实验目标

采集camera图像数据,并通过VGA接口显示到显示器上。2,测试系统结构

1》整体结构

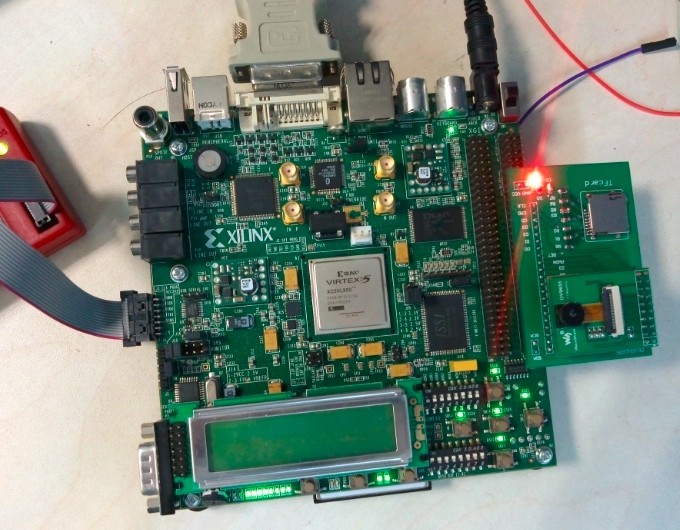

测试系统由ov9655 camera board,ML501开发板,自己做的转接板。三部分组成。ov9655:

整个系统如下所示:

2》RTL结构

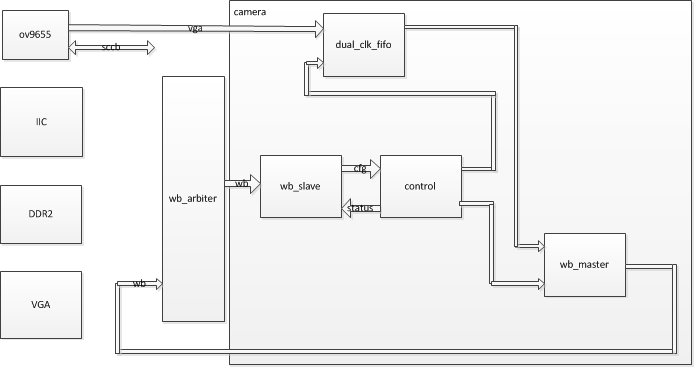

a,整体结构如下所示:

需要说明的是,为了测试方便,camera和vga进行数据交换的framebuffer采用片内的blokram来实现。

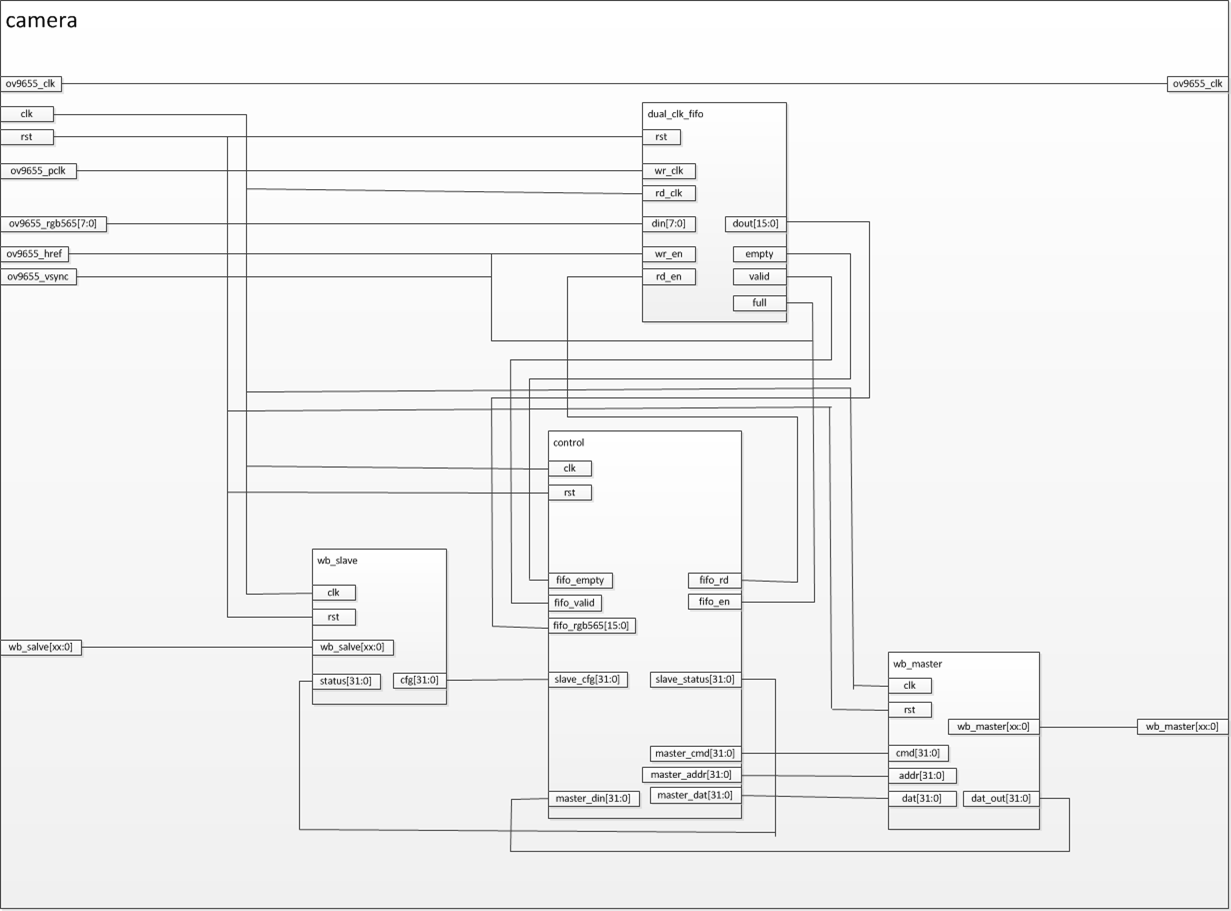

b,模块接口定义

在确定具体实现方案并完成模块划分之后,在正式编写RTL之前,我们还需要确定模块的具体端口。VGA模块,我们之前已经进行过详细的测试和验证了,这里不再赘述。下面是camera模块的端口定义。如下图所示:

3,RTL编码

确定好所有模块的端口之后,我们就可以进行RTL的编码工作了。整个测试工程,我已上传:http://download.csdn.net/detail/rill_zhen/7137673需要说明的是,整个测试工作最烦人的地方就是配置ov9655了。这里给出最终配置结果:

//-------------------OV9655_CFG5---------------------------------------------->

`ifdef OV9655_CFG5

parameter width=154;

wire [7:0] OV9655_REG_ADDR[width:0];

wire [7:0] OV9655_REG_DATA[width:0];

assign OV9655_REG_ADDR[0]=8'h12;assign OV9655_REG_DATA[0]=8'h80;//-00:COM3,reset

//assign OV9655_REG_ADDR[0]=8'h00;assign OV9655_REG_DATA[0]=8'h00;//00:GAIN

assign OV9655_REG_ADDR[1]=8'h01;assign OV9655_REG_DATA[1]=8'h80;//80:blue channel gain set

assign OV9655_REG_ADDR[2]=8'h02;assign OV9655_REG_DATA[2]=8'h80;//80:red channel gain set

assign OV9655_REG_ADDR[3]=8'h03;assign OV9655_REG_DATA[3]=8'h02;//-4a:vertical frame control

assign OV9655_REG_ADDR[4]=8'h04;assign OV9655_REG_DATA[4]=8'h00;//00:COM1

assign OV9655_REG_ADDR[5]=8'h09;assign OV9655_REG_DATA[5]=8'h03;//-01:COM2

assign OV9655_REG_ADDR[6]=8'h0c;assign OV9655_REG_DATA[6]=8'h00;//00:COM3

assign OV9655_REG_ADDR[7]=8'h0d;assign OV9655_REG_DATA[7]=8'h40;//40:COM4

//assign OV9655_REG_ADDR[7]=8'h0e;assign OV9655_REG_DATA[7]=8'h01;//01:COM5

assign OV9655_REG_ADDR[8]=8'h0f;assign OV9655_REG_DATA[8]=8'hc0;//-42:COM6

assign OV9655_REG_ADDR[9]=8'h10;assign OV9655_REG_DATA[9]=8'h50;//-40:exposure value(middle 8bits)

assign OV9655_REG_ADDR[10]=8'h11;assign OV9655_REG_DATA[10]=8'h00;//=80=00:internal clk,pre-scalar

assign OV9655_REG_ADDR[11]=8'h12;assign OV9655_REG_DATA[11]=8'h63;//=63=00:COM7

assign OV9655_REG_ADDR[12]=8'h13;assign OV9655_REG_DATA[12]=8'hef;//8f:COM8

assign OV9655_REG_ADDR[13]=8'h14;assign OV9655_REG_DATA[13]=8'h2e;//-4a:COM9

assign OV9655_REG_ADDR[14]=8'h15;assign OV9655_REG_DATA[14]=8'h00;//=08=00:Com10,HREF reverse ******************

assign OV9655_REG_ADDR[15]=8'h16;assign OV9655_REG_DATA[15]=8'h04;//=24=04:REG16

assign OV9655_REG_ADDR[16]=8'h17;assign OV9655_REG_DATA[16]=8'h16;//=16,18=24:HSTART high 8bits ******************

assign OV9655_REG_ADDR[17]=8'h18;assign OV9655_REG_DATA[17]=8'h02;//=02,04=c4:HSTOP high 8bits ******************

assign OV9655_REG_ADDR[18]=8'h19;assign OV9655_REG_DATA[18]=8'h04;//01:VSTART high 8bits

assign OV9655_REG_ADDR[19]=8'h1a;assign OV9655_REG_DATA[19]=8'h3d;//=81=f1:VSTOP high 8bits

assign OV9655_REG_ADDR[20]=8'h1e;assign OV9655_REG_DATA[20]=8'h18;//=00=00:mirror/vflip ******************

assign OV9655_REG_ADDR[21]=8'h24;assign OV9655_REG_DATA[21]=8'h3c;//-78:AGC/AEC upper limit

assign OV9655_REG_ADDR[22]=8'h25;assign OV9655_REG_DATA[22]=8'h36;//-68:AGC/AEC lower limit

assign OV9655_REG_ADDR[23]=8'h26;assign OV9655_REG_DATA[23]=8'h72;//-d4:faster mode upper lower limit

assign OV9655_REG_ADDR[24]=8'h27;assign OV9655_REG_DATA[24]=8'h08;//-80:B bias,COM6[0]=1

assign OV9655_REG_ADDR[25]=8'h28;assign OV9655_REG_DATA[25]=8'h08;//-80:Gb bias,COM6[0]=1

assign OV9655_REG_ADDR[26]=8'h29;assign OV9655_REG_DATA[26]=8'h15;//-00:RGB pre-gain

assign OV9655_REG_ADDR[27]=8'h2a;assign OV9655_REG_DATA[27]=8'h00;//00:dumy pixel insert MSB

assign OV9655_REG_ADDR[28]=8'h2b;assign OV9655_REG_DATA[28]=8'h00;//00:dumy pixel insert LSB

assign OV9655_REG_ADDR[29]=8'h2c;assign OV9655_REG_DATA[29]=8'h08;//-80:B bias,COM6[0]=1

assign OV9655_REG_ADDR[30]=8'h32;assign OV9655_REG_DATA[30]=8'hc0;//=12=a4:HREF control ******************

assign OV9655_REG_ADDR[31]=8'h33;assign OV9655_REG_DATA[31]=8'h00;//00:array control

assign OV9655_REG_ADDR[32]=8'h34;assign OV9655_REG_DATA[32]=8'h3f;//3f:array control

assign OV9655_REG_ADDR[33]=8'h35;assign OV9655_REG_DATA[33]=8'h00;//=00=90:array control******************

assign OV9655_REG_ADDR[34]=8'h36;assign OV9655_REG_DATA[34]=8'h00;//=3a=f9:array control******************

assign OV9655_REG_ADDR[35]=8'h38;assign OV9655_REG_DATA[35]=8'h72;//72:ADC

assign OV9655_REG_ADDR[36]=8'h39;assign OV9655_REG_DATA[36]=8'h57;//=57=10:analog ******************

assign OV9655_REG_ADDR[37]=8'h3a;assign OV9655_REG_DATA[37]=8'h02;//=ca=0c: ******************

assign OV9655_REG_ADDR[38]=8'h3b;assign OV9655_REG_DATA[38]=8'h04;//80:night mode

assign OV9655_REG_ADDR[39]=8'h3d;assign OV9655_REG_DATA[39]=8'h99;//99:gamma,vsync,YUV delay

assign OV9655_REG_ADDR[40]=8'h3e;assign OV9655_REG_DATA[40]=8'h02;//=02=0e:black white correct, zoom(reg:3e[1],41[0],72,74,75)

assign OV9655_REG_ADDR[41]=8'h3f;assign OV9655_REG_DATA[41]=8'hc1;//88:edge enhancement factor

assign OV9655_REG_ADDR[42]=8'h40;assign OV9655_REG_DATA[42]=8'hd0;//c0:RGB565

assign OV9655_REG_ADDR[43]=8'h41;assign OV9655_REG_DATA[43]=8'h41;//=41=00:color mix,scaling down******************

assign OV9655_REG_ADDR[44]=8'h42;assign OV9655_REG_DATA[44]=8'hc0;//=c0=08:de-noise,edge enhancement

assign OV9655_REG_ADDR[45]=8'h43;assign OV9655_REG_DATA[45]=8'h0a;//xx reserved

assign OV9655_REG_ADDR[46]=8'h44;assign OV9655_REG_DATA[46]=8'hf0;//xx

assign OV9655_REG_ADDR[47]=8'h45;assign OV9655_REG_DATA[47]=8'h46;//xx

assign OV9655_REG_ADDR[48]=8'h46;assign OV9655_REG_DATA[48]=8'h62;//xx

assign OV9655_REG_ADDR[49]=8'h47;assign OV9655_REG_DATA[49]=8'h2a;//xx

assign OV9655_REG_ADDR[50]=8'h48;assign OV9655_REG_DATA[50]=8'h3c;//xx

assign OV9655_REG_ADDR[51]=8'h4a;assign OV9655_REG_DATA[51]=8'hfc;//xx

assign OV9655_REG_ADDR[52]=8'h4b;assign OV9655_REG_DATA[52]=8'hfc;//xx

assign OV9655_REG_ADDR[53]=8'h4c;assign OV9655_REG_DATA[53]=8'h7f;//xx

assign OV9655_REG_ADDR[54]=8'h4d;assign OV9655_REG_DATA[54]=8'h7f;//xx

assign OV9655_REG_ADDR[55]=8'h4e;assign OV9655_REG_DATA[55]=8'h7f;//xx

assign OV9655_REG_ADDR[56]=8'h4f;assign OV9655_REG_DATA[56]=8'h98;//-40:matrix coefficient 1

assign OV9655_REG_ADDR[57]=8'h50;assign OV9655_REG_DATA[57]=8'h98;//-34:matrix coefficient 2

assign OV9655_REG_ADDR[58]=8'h51;assign OV9655_REG_DATA[58]=8'h00;//-0c:matrix coefficient 3

assign OV9655_REG_ADDR[59]=8'h52;assign OV9655_REG_DATA[59]=8'h28;//-17:matrix coefficient 4

assign OV9655_REG_ADDR[60]=8'h53;assign OV9655_REG_DATA[60]=8'h70;//-29:matrix coefficient 5

assign OV9655_REG_ADDR[61]=8'h54;assign OV9655_REG_DATA[61]=8'h98;//-40:matrix coefficient 6

assign OV9655_REG_ADDR[62]=8'h58;assign OV9655_REG_DATA[62]=8'h1a;//-1e:matrix coefficient sign

assign OV9655_REG_ADDR[63]=8'h59;assign OV9655_REG_DATA[63]=8'h85;//-91:AWB control 1

assign OV9655_REG_ADDR[64]=8'h5a;assign OV9655_REG_DATA[64]=8'ha9;//-94:AWB control 2

assign OV9655_REG_ADDR[65]=8'h5b;assign OV9655_REG_DATA[65]=8'h64;//-aa:AWB control 3

assign OV9655_REG_ADDR[66]=8'h5c;assign OV9655_REG_DATA[66]=8'h84;//-71:AWB control 4

assign OV9655_REG_ADDR[67]=8'h5d;assign OV9655_REG_DATA[67]=8'h53;//-8d:AWB control 5

assign OV9655_REG_ADDR[68]=8'h5e;assign OV9655_REG_DATA[68]=8'h0e;//-0f:AWB control 6

assign OV9655_REG_ADDR[69]=8'h5f;assign OV9655_REG_DATA[69]=8'hf0;//f0:AWB blue gain limit

assign OV9655_REG_ADDR[70]=8'h60;assign OV9655_REG_DATA[70]=8'hf0;//f0:AWB red gain limit

assign OV9655_REG_ADDR[71]=8'h61;assign OV9655_REG_DATA[71]=8'hf0;//f0:AWB green gain limit

assign OV9655_REG_ADDR[72]=8'h62;assign OV9655_REG_DATA[72]=8'h00;//00:lens corrent 1

assign OV9655_REG_ADDR[73]=8'h63;assign OV9655_REG_DATA[73]=8'h00;//00:lens corrent 2

assign OV9655_REG_ADDR[74]=8'h64;assign OV9655_REG_DATA[74]=8'h02;//-10:lens corrent 3

assign OV9655_REG_ADDR[75]=8'h65;assign OV9655_REG_DATA[75]=8'h20;//-80:lens corrent 4

assign OV9655_REG_ADDR[76]=8'h66;assign OV9655_REG_DATA[76]=8'h00;//00:lens control

assign OV9655_REG_ADDR[77]=8'h69;assign OV9655_REG_DATA[77]=8'h0a;//xx reserved

assign OV9655_REG_ADDR[78]=8'h6b;assign OV9655_REG_DATA[78]=8'h0a;//0a:band gap,PLL

assign OV9655_REG_ADDR[79]=8'h6c;assign OV9655_REG_DATA[79]=8'h04;//xx

assign OV9655_REG_ADDR[80]=8'h6d;assign OV9655_REG_DATA[80]=8'h55;//xx

assign OV9655_REG_ADDR[81]=8'h6e;assign OV9655_REG_DATA[81]=8'h00;//xx

assign OV9655_REG_ADDR[82]=8'h6f;assign OV9655_REG_DATA[82]=8'h9d;//xx

assign OV9655_REG_ADDR[83]=8'h70;assign OV9655_REG_DATA[83]=8'h21;//-01:de-noise ***************

assign OV9655_REG_ADDR[84]=8'h71;assign OV9655_REG_DATA[84]=8'h78;//xx

assign OV9655_REG_ADDR[85]=8'h72;assign OV9655_REG_DATA[85]=8'h11;//=11=00: pixel output index ***************

assign OV9655_REG_ADDR[86]=8'h73;assign OV9655_REG_DATA[86]=8'h01;//01:pixel clk adjust

assign OV9655_REG_ADDR[87]=8'h74;assign OV9655_REG_DATA[87]=8'h10;//=10=3a:H scaling down coefficient(reg*40)

assign OV9655_REG_ADDR[88]=8'h75;assign OV9655_REG_DATA[88]=8'h10;//=10=3a:V scaling down coefficient(reg*30)

assign OV9655_REG_ADDR[89]=8'h76;assign OV9655_REG_DATA[89]=8'h01;//xx

assign OV9655_REG_ADDR[90]=8'h77;assign OV9655_REG_DATA[90]=8'h02;//xx

assign OV9655_REG_ADDR[91]=8'h7A;assign OV9655_REG_DATA[91]=8'h12;//gamma curve

assign OV9655_REG_ADDR[92]=8'h7B;assign OV9655_REG_DATA[92]=8'h08;//gamma curve

assign OV9655_REG_ADDR[93]=8'h7C;assign OV9655_REG_DATA[93]=8'h16;//gamma curve

assign OV9655_REG_ADDR[94]=8'h7D;assign OV9655_REG_DATA[94]=8'h30;//gamma curve

assign OV9655_REG_ADDR[95]=8'h7E;assign OV9655_REG_DATA[95]=8'h5e;//gamma curve

assign OV9655_REG_ADDR[96]=8'h7F;assign OV9655_REG_DATA[96]=8'h72;//gamma curve

assign OV9655_REG_ADDR[97]=8'h80;assign OV9655_REG_DATA[97]=8'h82;//gamma curve

assign OV9655_REG_ADDR[98]=8'h81;assign OV9655_REG_DATA[98]=8'h8e;//gamma curve

assign OV9655_REG_ADDR[99]=8'h82;assign OV9655_REG_DATA[99]=8'h9a;//gamma curve

assign OV9655_REG_ADDR[100]=8'h83;assign OV9655_REG_DATA[100]=8'ha4;//gamma curve

assign OV9655_REG_ADDR[101]=8'h84;assign OV9655_REG_DATA[101]=8'hac;//gamma curve

assign OV9655_REG_ADDR[102]=8'h85;assign OV9655_REG_DATA[102]=8'hb8;//gamma curve

assign OV9655_REG_ADDR[103]=8'h86;assign OV9655_REG_DATA[103]=8'hc3;//gamma curve

assign OV9655_REG_ADDR[104]=8'h87;assign OV9655_REG_DATA[104]=8'hd6;//gamma curve

assign OV9655_REG_ADDR[105]=8'h88;assign OV9655_REG_DATA[105]=8'he6;//gamma curve

assign OV9655_REG_ADDR[106]=8'h89;assign OV9655_REG_DATA[106]=8'hf2;//gamma curve

assign OV9655_REG_ADDR[107]=8'h8a;assign OV9655_REG_DATA[107]=8'h24;//xx

assign OV9655_REG_ADDR[108]=8'h8c;assign OV9655_REG_DATA[108]=8'h80;//-0c:UV adjust average

assign OV9655_REG_ADDR[109]=8'h90;assign OV9655_REG_DATA[109]=8'h7d;//xx

assign OV9655_REG_ADDR[110]=8'h91;assign OV9655_REG_DATA[110]=8'h7b;//xx

assign OV9655_REG_ADDR[111]=8'h9d;assign OV9655_REG_DATA[111]=8'h02;//00:lens corrent 6

assign OV9655_REG_ADDR[112]=8'h9e;assign OV9655_REG_DATA[112]=8'h02;//00:lens corrent 7

assign OV9655_REG_ADDR[113]=8'h9f;assign OV9655_REG_DATA[113]=8'h7a;//xx

assign OV9655_REG_ADDR[114]=8'ha0;assign OV9655_REG_DATA[114]=8'h79;//xx

assign OV9655_REG_ADDR[115]=8'ha1;assign OV9655_REG_DATA[115]=8'h1f;//-40:exposure value *****************

assign OV9655_REG_ADDR[116]=8'ha4;assign OV9655_REG_DATA[116]=8'h50;//78:digital gain value

assign OV9655_REG_ADDR[117]=8'ha5;assign OV9655_REG_DATA[117]=8'h68;//xx

assign OV9655_REG_ADDR[118]=8'ha6;assign OV9655_REG_DATA[118]=8'h4a;//86:AWB green component gain set

assign OV9655_REG_ADDR[119]=8'ha8;assign OV9655_REG_DATA[119]=8'hc1;//01:nanalog control

assign OV9655_REG_ADDR[120]=8'ha9;assign OV9655_REG_DATA[120]=8'hef;//00:nanalog control

assign OV9655_REG_ADDR[121]=8'haa;assign OV9655_REG_DATA[121]=8'h92;//xx

assign OV9655_REG_ADDR[122]=8'hab;assign OV9655_REG_DATA[122]=8'h04;//xx

assign OV9655_REG_ADDR[123]=8'hac;assign OV9655_REG_DATA[123]=8'h80;//-84:black level 1

assign OV9655_REG_ADDR[124]=8'had;assign OV9655_REG_DATA[124]=8'h80;//-84:black level 2

assign OV9655_REG_ADDR[125]=8'hae;assign OV9655_REG_DATA[125]=8'h80;//-84:black level 3

assign OV9655_REG_ADDR[126]=8'haf;assign OV9655_REG_DATA[126]=8'h80;//-84:black level 4

assign OV9655_REG_ADDR[127]=8'hb2;assign OV9655_REG_DATA[127]=8'hf2;//-01:black level 7

assign OV9655_REG_ADDR[128]=8'hb3;assign OV9655_REG_DATA[128]=8'h20;//-0f:black level 8

assign OV9655_REG_ADDR[129]=8'hb4;assign OV9655_REG_DATA[129]=8'h20;//-00:UV adjust,strop

assign OV9655_REG_ADDR[130]=8'hb5;assign OV9655_REG_DATA[130]=8'h00;//xx

assign OV9655_REG_ADDR[131]=8'hb6;assign OV9655_REG_DATA[131]=8'haf;//xx

assign OV9655_REG_ADDR[132]=8'hb6;assign OV9655_REG_DATA[132]=8'haf;//xx

assign OV9655_REG_ADDR[133]=8'hbb;assign OV9655_REG_DATA[133]=8'hae;//xx

assign OV9655_REG_ADDR[134]=8'hbc;assign OV9655_REG_DATA[134]=8'h7f;//-40:ADC B channal offset

assign OV9655_REG_ADDR[135]=8'hbd;assign OV9655_REG_DATA[135]=8'h7f;//-40:ADC R channal offset

assign OV9655_REG_ADDR[136]=8'hbe;assign OV9655_REG_DATA[136]=8'h7f;//-40:ADC Gb channal offset

assign OV9655_REG_ADDR[137]=8'hbf;assign OV9655_REG_DATA[137]=8'h7f;//-40:ADC Gr channal offset

assign OV9655_REG_ADDR[138]=8'hbf;assign OV9655_REG_DATA[138]=8'h7f;//-40:ADC Gr channal offset

assign OV9655_REG_ADDR[139]=8'hc0;assign OV9655_REG_DATA[139]=8'h10;//xx

assign OV9655_REG_ADDR[140]=8'hc1;assign OV9655_REG_DATA[140]=8'hc0;//xx

assign OV9655_REG_ADDR[141]=8'hc2;assign OV9655_REG_DATA[141]=8'h01;//xx

assign OV9655_REG_ADDR[142]=8'hc3;assign OV9655_REG_DATA[142]=8'h4e;//xx

assign OV9655_REG_ADDR[143]=8'hc6;assign OV9655_REG_DATA[143]=8'h05;//xx

assign OV9655_REG_ADDR[144]=8'hc7;assign OV9655_REG_DATA[144]=8'h81;//-80:pixel clk freq select

assign OV9655_REG_ADDR[145]=8'hc9;assign OV9655_REG_DATA[145]=8'he0;//xx

assign OV9655_REG_ADDR[146]=8'hca;assign OV9655_REG_DATA[146]=8'he8;//xx

assign OV9655_REG_ADDR[147]=8'hcb;assign OV9655_REG_DATA[147]=8'hf0;//xx

assign OV9655_REG_ADDR[148]=8'hcc;assign OV9655_REG_DATA[148]=8'hd8;//xx

assign OV9655_REG_ADDR[149]=8'hcd;assign OV9655_REG_DATA[149]=8'h93;//xx

/*assign OV9655_REG_ADDR[150]=8'h8d;//com20 bit[4] color bar test mode

assign OV9655_REG_DATA[150]=8'h10;//color bar

assign OV9655_REG_ADDR[151]=8'h0c;//com3 bit[7] color bar out

assign OV9655_REG_DATA[151]=8'h80;//color bar*/

assign OV9655_REG_ADDR[150]=8'h00;assign OV9655_REG_DATA[150]=8'h00;

//Rill add

assign OV9655_REG_ADDR[151]=8'h55;assign OV9655_REG_DATA[151]=8'h00;//00:brightness *******************

assign OV9655_REG_ADDR[152]=8'h56;assign OV9655_REG_DATA[152]=8'h40;//40:contrast 1 *******************

assign OV9655_REG_ADDR[153]=8'h57;assign OV9655_REG_DATA[153]=8'h80;//80:contrast 2 *******************

assign OV9655_REG_ADDR[154]=8'h8b;assign OV9655_REG_DATA[154]=8'h04;//04:zoom mode under VGA timing *******************

`endif4,验证结果

经过近一周的努力,现在camera和vga模块都work了,我们可以通过显示器显示ov9655采集到的图像了。下面是320X240的输出效果:需要说明的是由于片上blokram资源有限,这里采用的framebuffer为64KB,但是320X240大于64KB,略大于framebuffer,所以会出现图像重复。