一、上电时序分析

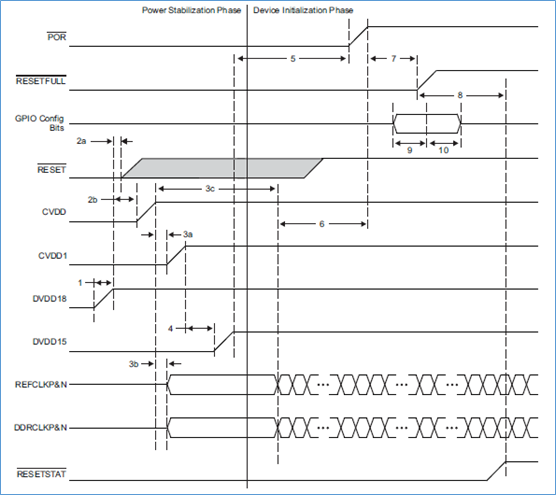

C6678上电时序如下图所示,时序分析如下:1、 所有电源及时钟稳定(RESET、POR、RESETFULL信号初始为低)

2、 拉高RESET信号

3、 拉高RESET后,POR信号至少保持100us后拉高

4、 保持GPIO引脚状态有效2ms后拉高RESETFULL,继续保持GPIO引脚状态有效2ms

5、 最后RESETSTAT信号将拉高(该信号芯片内部驱动输出)

上电时序

二、复位

C6678复位包括四种类型1、 上电复位

2、 硬复位

3、 软复位

4、 CPU局部复位

1、 上电复位说明

在上电期间,必须先将POR引脚置为有效(驱动为低电平),直到电源达到正常工作状态。 还提供RESETFULL引脚,允许板载主机复位整个器件,包括复位隔离逻辑。 假设器件已经上电,因此与POR不同,RESETFULL引脚将由电源良好电路以外的板载主机控制驱动。 对于上电复位,主PLL控制器进入旁路模式,PLL未使能。 其他复位不会影响PLL的状态或PLL控制器中的分频器。上电复位期间必须遵循以下顺序:① 等待所有电源达到正常工作状态,同时保持POR引脚有效(驱动为低电平)。 当POR置位时,除RESETSTAT外的所有引脚都将被设置为高阻态。 在POR引脚置为无效(驱动为高电平)后,所有Z组引脚,低组引脚和高组引脚都将置于其复位状态,并保持其复位状态,直到其各自的外设配置为止。 所有受电源管理的外设在上电复位后都会被禁用,必须通过器件状态控制寄存器启用

② 时钟被复位,它们在整个芯片中传播,以重置任何同步使用复位的逻辑。 现在所有逻辑都被复位,RESETSTAT将被驱动为低电平,表示器件处于复位状态。

③ POR必须保持有效,直到电路板上的所有电源都稳定,然后芯片级PLL才能锁定至少一段时间。

④ 现在可以取消激活POR引脚。 此时复位采样引脚值被锁存。 芯片级PLL退出复位并开始其锁定序列,所有上电设备初始化也开始。

⑤ 器件初始化完成后,RESETSTAT引脚被置低(驱动为高电平)。 此时,DDR3 PLL已完成锁定序列并输出有效时钟。 允许两个PLL控制器的系统时钟完成其当前周期,然后暂停其各自系统参考时钟的10个周期。 暂停后,系统时钟将按默认值除以设置重新启动。

⑥ 设备现在处于复位状态,设备执行将根据所选的引导模式开始执行。

对于大多数器件,只有当POR和RESET引脚都被置低(驱动为高电平)时,复位才会被置低。 因此,按照上述顺序,如果RESET引脚保持低电平超过POR引脚的低电平周期,则器件的大部分将保持复位状态。 RESET引脚不应与POR引脚连接在一起。