在移植Nboot时,发现串口输出乱码,检查串口配置没问题后,觉得应该是时钟配置没配好,修改后果然ok,所以补习一下!

2440时钟配置详细说明,以上电为顺序讲述:

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD

controller, the DMA and USB host block.

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,

ADC, UART, GPIO, RTC and SPI. UCLK专门为USB供电,有UPLL输出。 3、有两个锁相环,一个MPLL负责FCLK,HCLK,PCLK,一个UPLL负责USB的48MHz,通过三个倍频因子MDIV、PDIV和SDIV来 设置倍频。

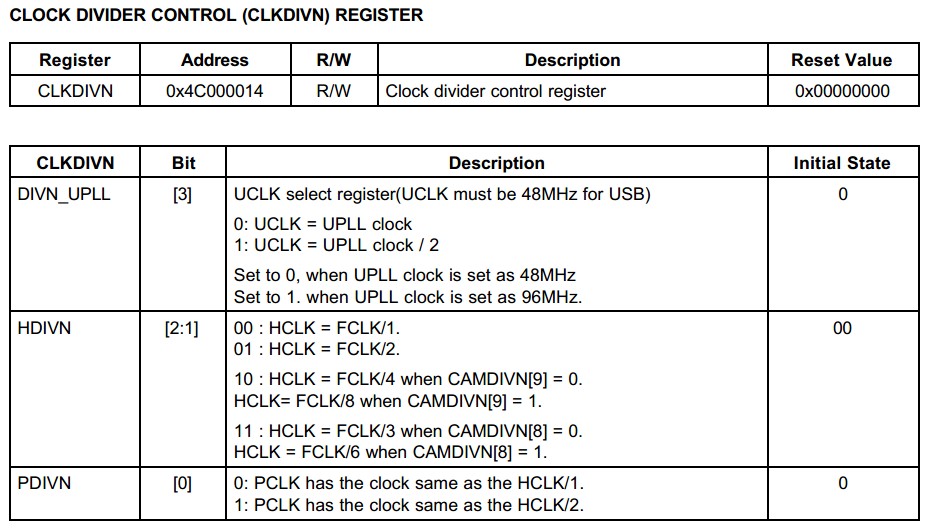

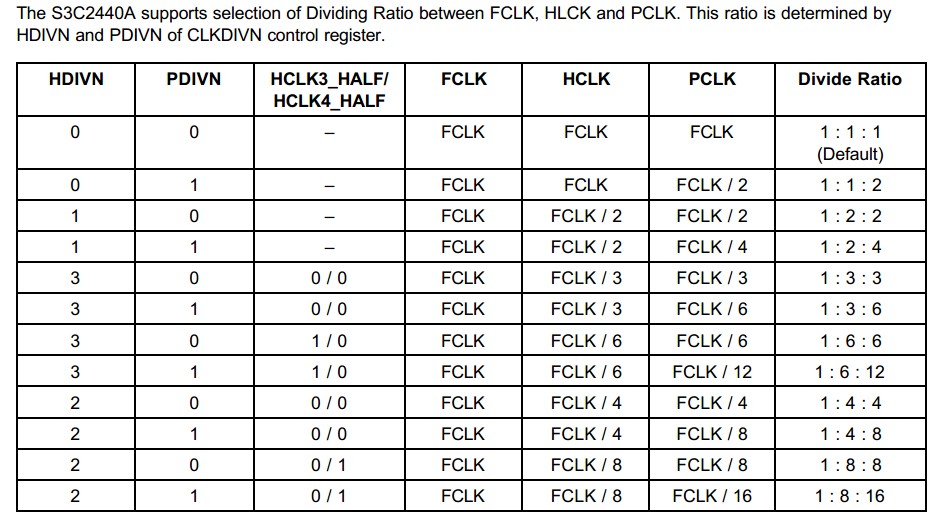

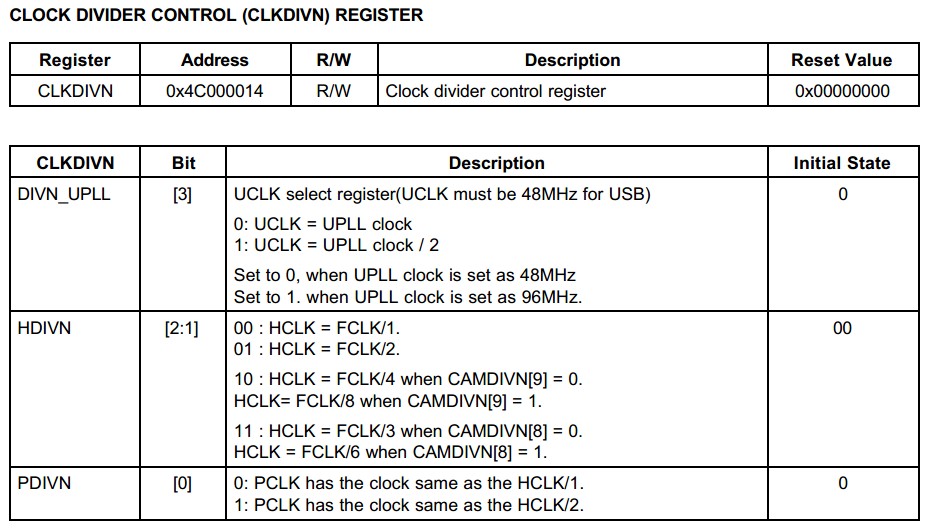

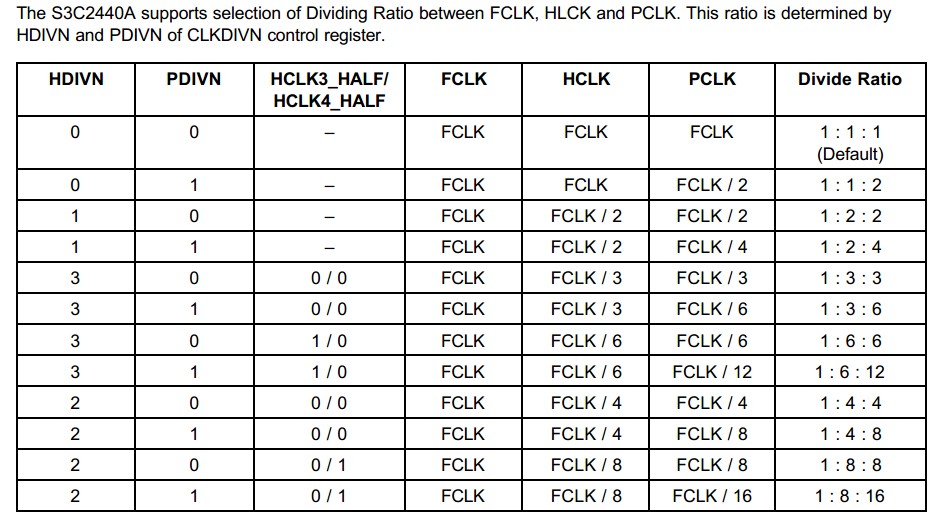

图HDIVN 和PDIVN对应的比例,HCLK4_HALF和HCLK3_HALF在摄像头CAMDIVN寄存器中。

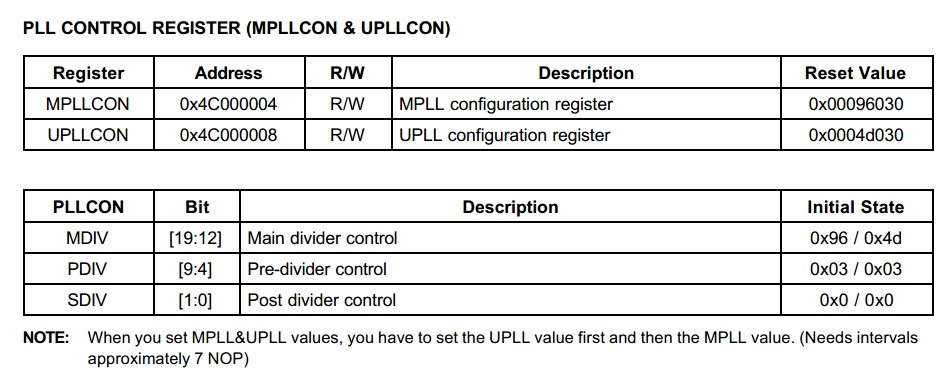

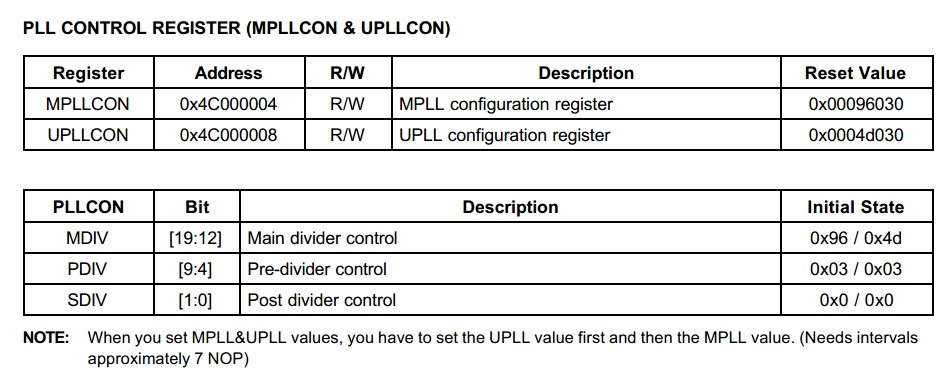

图HDIVN 和PDIVN对应的比例,HCLK4_HALF和HCLK3_HALF在摄像头CAMDIVN寄存器中。  ( 3)MPLLCON寄存器位[19:12]-MDIV(Main divider control);[9:4]-PDIV(Pre-divider control);[1:0]-SDIV(Post divider

control)。

( 3)MPLLCON寄存器位[19:12]-MDIV(Main divider control);[9:4]-PDIV(Pre-divider control);[1:0]-SDIV(Post divider

control)。

锁相环输出时钟MPLL(FCLK) 通过如下计算公式得出:

MPLL(FCLK) = (m * Fin)/(p * 2^s);其中:m

= (MDIV + 8), p = (PDIV + 2), s = SDIV,Fin 输入的时钟频率。

如:MPLLCON设为(0x5c << 12)|(0x01 << 4)|(0x1),即0x5c010,可以计算出FCLK=200MHz,假设CLKDIVN设置

HDIV=1和PDIV=1;可知比例FCLK、HCLK、PCLK比率为1:2:4,所以HCLK=100MHz,PCLK=50MHz。

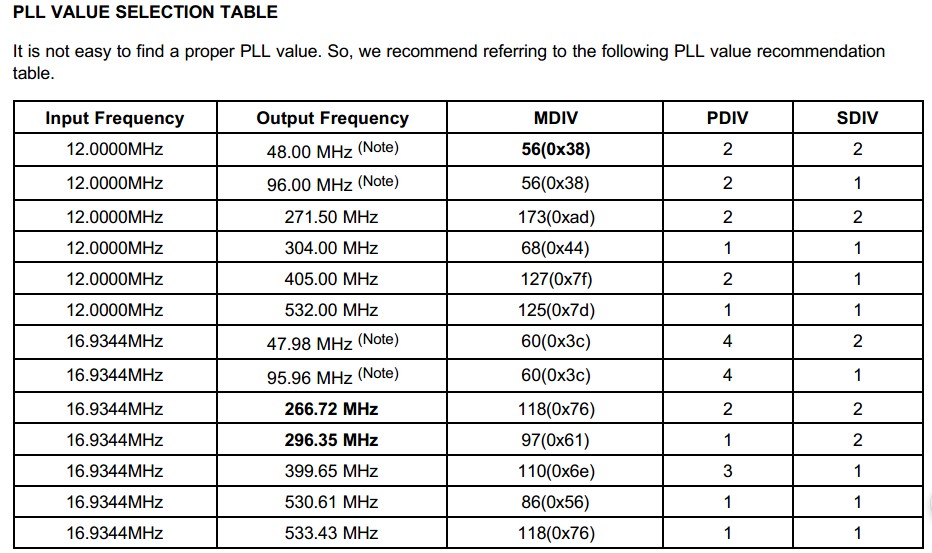

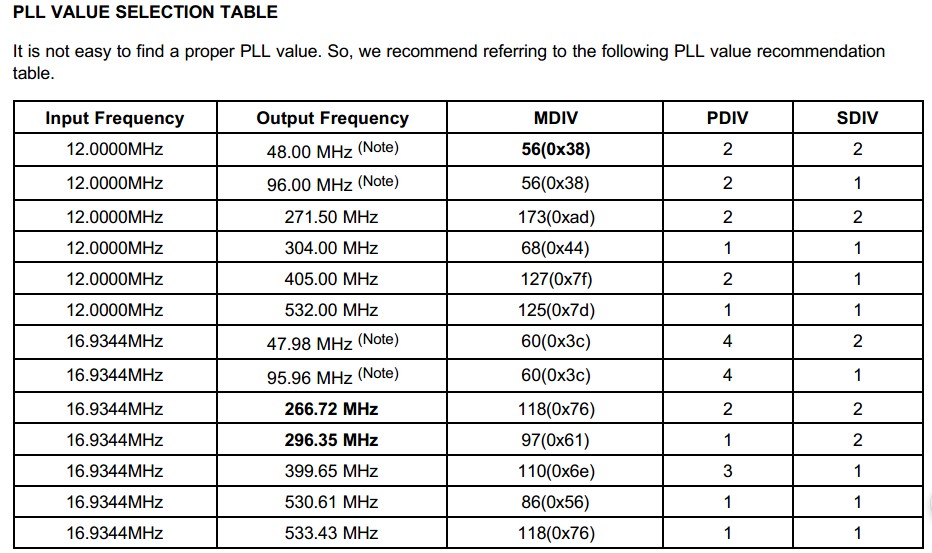

下图 为锁相环配置推荐表。

锁相环输出时钟MPLL(FCLK) 通过如下计算公式得出:

MPLL(FCLK) = (m * Fin)/(p * 2^s);其中:m

= (MDIV + 8), p = (PDIV + 2), s = SDIV,Fin 输入的时钟频率。

如:MPLLCON设为(0x5c << 12)|(0x01 << 4)|(0x1),即0x5c010,可以计算出FCLK=200MHz,假设CLKDIVN设置

HDIV=1和PDIV=1;可知比例FCLK、HCLK、PCLK比率为1:2:4,所以HCLK=100MHz,PCLK=50MHz。

下图 为锁相环配置推荐表。

UPLLCON同理一样设置,计算公式如下:UPLL(UCLK) = (m * Fin) / (p * 2^s),m = (MDIV + 8), p = (PDIV + 2), s =SDIV。 Fin 输入的时钟频率。 (4)程序:

在移植程序是要注意时钟修改后对应的模块频率也改变了,我的Nboot移植时,需要修改两个地方:UART 和 SDRAM。 UART,它是接在APB总线上,对应的时钟信号为PCLK,假设现在为50MHz。如果想要设置波特率为115200bps,那么根公式 UBRDIV0=(int)(PCLK/(bps*16))-1计算,应该为26。程序:UBRDIV0 = ((int)(PCLK/16./UART_BAUD_RATE) -1).

2440时钟配置详细说明,以上电为顺序讲述:

一、S3C2440A时钟概述

1、S3C2440A的电源管理有4种模式:NORMAL,SLOW,IDLE,SLEEP。 2、 有4种时钟:FCLK,HCLK,PCLK,UCLK具体分工如下: FCLK is used by ARM920T.HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD

controller, the DMA and USB host block.

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,

ADC, UART, GPIO, RTC and SPI. UCLK专门为USB供电,有UPLL输出。 3、有两个锁相环,一个MPLL负责FCLK,HCLK,PCLK,一个UPLL负责USB的48MHz,通过三个倍频因子MDIV、PDIV和SDIV来 设置倍频。

二、S3C2440A时钟上电过程

1、主时钟源可以由外部时钟(EXTCLK)或者外部晶振(XTIPll)提供,时钟源由模式控制引脚OM3和OM2选择,在复位信号 的上升沿检测OM3和OM2引脚状态并锁定在OM[3:2]中。 2、我们可以在程序开头启动MPLL,在设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段 (Lock Time)时间内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定。Lock Time之后,MPLL输出平 稳。在上电没有设置MPLL时,系统时钟为晶振时钟。三、S3C2440A时钟配置流程和样例

1、设置S3C2440A的时钟频率需要配置4个寄存器:LOCKTIME(0x4C000000)、CLKDIVN (0x4C000014)、MPLLCON ( 0x4C000004)、UPLLCON(0x4C000008)。 2、时钟配置顺序如上:LOCKTIME => CLKDIVN => MPLLCON => UPLLCON。注意:UPLL的设置要先于MPLL,切超前7个时钟 设置。 3、时钟样例: (1)、LOCKTIME:位[31:16]用于UPLL,位[15:0]用于MPLL。确省值为0xFFFFFFFF (2)、CLKDIVN:DIVN _UPLL[3]:HDIVN [2:1]:PDIVN [0]用来设置FCLK:HCLK:PCLK的比例关系,默认为1:1:1。 CLKDIVN不同的设置及对应的时钟比例关系如下图: 图HDIVN 和PDIVN对应的比例,HCLK4_HALF和HCLK3_HALF在摄像头CAMDIVN寄存器中。

图HDIVN 和PDIVN对应的比例,HCLK4_HALF和HCLK3_HALF在摄像头CAMDIVN寄存器中。  ( 3)MPLLCON寄存器位[19:12]-MDIV(Main divider control);[9:4]-PDIV(Pre-divider control);[1:0]-SDIV(Post divider

control)。

( 3)MPLLCON寄存器位[19:12]-MDIV(Main divider control);[9:4]-PDIV(Pre-divider control);[1:0]-SDIV(Post divider

control)。

锁相环输出时钟MPLL(FCLK) 通过如下计算公式得出:

MPLL(FCLK) = (m * Fin)/(p * 2^s);其中:m

= (MDIV + 8), p = (PDIV + 2), s = SDIV,Fin 输入的时钟频率。

如:MPLLCON设为(0x5c << 12)|(0x01 << 4)|(0x1),即0x5c010,可以计算出FCLK=200MHz,假设CLKDIVN设置

HDIV=1和PDIV=1;可知比例FCLK、HCLK、PCLK比率为1:2:4,所以HCLK=100MHz,PCLK=50MHz。

下图 为锁相环配置推荐表。

锁相环输出时钟MPLL(FCLK) 通过如下计算公式得出:

MPLL(FCLK) = (m * Fin)/(p * 2^s);其中:m

= (MDIV + 8), p = (PDIV + 2), s = SDIV,Fin 输入的时钟频率。

如:MPLLCON设为(0x5c << 12)|(0x01 << 4)|(0x1),即0x5c010,可以计算出FCLK=200MHz,假设CLKDIVN设置

HDIV=1和PDIV=1;可知比例FCLK、HCLK、PCLK比率为1:2:4,所以HCLK=100MHz,PCLK=50MHz。

下图 为锁相环配置推荐表。

UPLLCON同理一样设置,计算公式如下:UPLL(UCLK) = (m * Fin) / (p * 2^s),m = (MDIV + 8), p = (PDIV + 2), s =SDIV。 Fin 输入的时钟频率。 (4)程序:

;To reduce PLL lock time, adjust the LOCKTIME register.

ldr r0,=LOCKTIMEldr r1,=0xffffffstr r1,[r0] ;Configure CLKDIVN

; Added for confirm clock divide. for 2440.; Setting value Fclk:Hclk:Pclkldr r0,=CLKDIVNldr r1,=CLKDIV_VAL; 0=1:1:1, 1=1:1:2, 2=1:2:2, 3=1:2:4, 4=1:4:4, 5=1:4:8, 6=1:3:3, 7=1:3:6.str r1,[r0];Configure UPLL

ldr r0,=UPLLCON

ldr r1,=((U_MDIV<<12)+(U_PDIV<<4)+U_SDIV)

str r1,[r0]

nop ; Caution: After UPLL setting, at least 7-clocks delay must be inserted for setting hardware be completed.

nop

nop

nop

nop

nop

nop

;Configure MPLL

ldr r0,=MPLLCON

ldr r1,=((96<<12)+(M_PDIV<<4)+M_SDIV) ;Fin=16.9344MHz 68<<12+1<<4+1

str r1,[r0]四、时钟修改影响单元

在移植程序是要注意时钟修改后对应的模块频率也改变了,我的Nboot移植时,需要修改两个地方:UART 和 SDRAM。 UART,它是接在APB总线上,对应的时钟信号为PCLK,假设现在为50MHz。如果想要设置波特率为115200bps,那么根公式 UBRDIV0=(int)(PCLK/(bps*16))-1计算,应该为26。程序:UBRDIV0 = ((int)(PCLK/16./UART_BAUD_RATE) -1).