一、本文内容

本文主要包含以下三个基本外围电路的调试过程与调试结果:- 电源模块

- 时钟模块

- 复位模块

二、电源模块调试

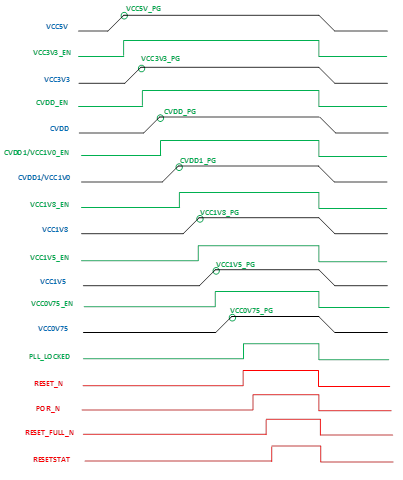

无论对FPGA还是DSP而言,对电源的上电顺序都有一定的要求,且不同型号的器件对电源轨的顺序要求不一定相同,因此建议对FPGA和DSP这两种器件采用各自独立的供电电路,以便于独立的控制各自的上电顺序。电源的上电顺序一般由电源管理芯片的PowerGood信号配合Enable信号来实现,如下图:

当该级电源使能后,通过PWRGD信号可以获取其输出状态,确定输出状态稳定后,再启动下一级需要上电的电源轨。通过示波器的single功能,抓取上电瞬间的电源芯片输出上升沿,从而确定实际顺序与设计顺序是否一致:

三、时钟配置

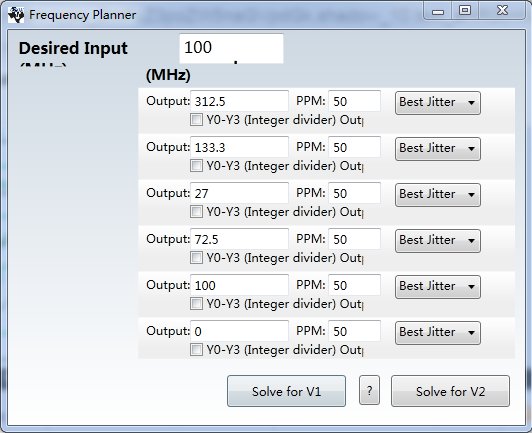

随着一些高速接口的波特率越来越高,器件对时钟源的品质要求也越来越高,同时,不同的接口类型,如PCIE,SRIO等,也需要不同的参考时钟频率。独立的晶振从性能、性价比、能耗比等方面很难满足系统设计要求,因此系统中采用cdcm6208芯片作为时钟源,实现整板时钟的管理。- 坑1:cdcm6208的输出有8路,但实际上只能输出6中不同频率的时钟,因为Y0,Y1共用一组分频系数,Y2,Y3共用一组分频系数,如下图:

- 坑2:采用SPI接口对CDCM6208进行配置时,关于SPI模式的CPOL,CPHA的设置问题,手册中并未明确说明,根据给出的timing进行猜测与测试,可以确定其SPI模式为:

- CPOL = 0;

- CPHA = 0;

- 福利:手动的计算各路时钟的倍频,分频,还要保证各个节点的频率满足芯片的限制范围,是一件十分繁琐和头痛的事情,好在TI官方提供了一个计算软件,可以自动计算出所有寄存器的值:

【Tools】/【Frequency Planner】中,设置好共6路需要输出的频率值:

【Tools】/【Registers】,可以直接查看软件计算所得的寄存器值,如有不满意,可以在软件的界面上直接调整,会自动实时更新到Registers窗口中:

四、 复位

在上电和时钟初始化过程中,DSP要一致保持在复位状态,然后按照手册规定的顺序释放即可,不再复述。五、 总结

最终得到的上电顺序、时钟Lock、复位顺序的前后关系如下图所示: 外围电路具备状态后,C6657可以正常连接仿真器,进行DDR3/RapidIO等功能的测试。

外围电路具备状态后,C6657可以正常连接仿真器,进行DDR3/RapidIO等功能的测试。