来自:http://blog.csdn.net/hezp1984/article/details/5841593

3.6.2.1 PIC Mode

PIC Mode is software compatible with the PC/AT because it actually employs the same hardware

interrupt configuration. As Figure 3-2 illustrates, the hardware for PIC Mode bypasses the APIC

components by using an interrupt mode configuration register (IMCR). This register controls

whether the interrupt signals that reach the BSP come from the master PIC or from the local APIC.

Before entering Symmetric I/O Mode, either the BIOS or the operating system must switch out of

PIC Mode by changing the IMCR. 3.6.2.2 Virtual Wire Mode

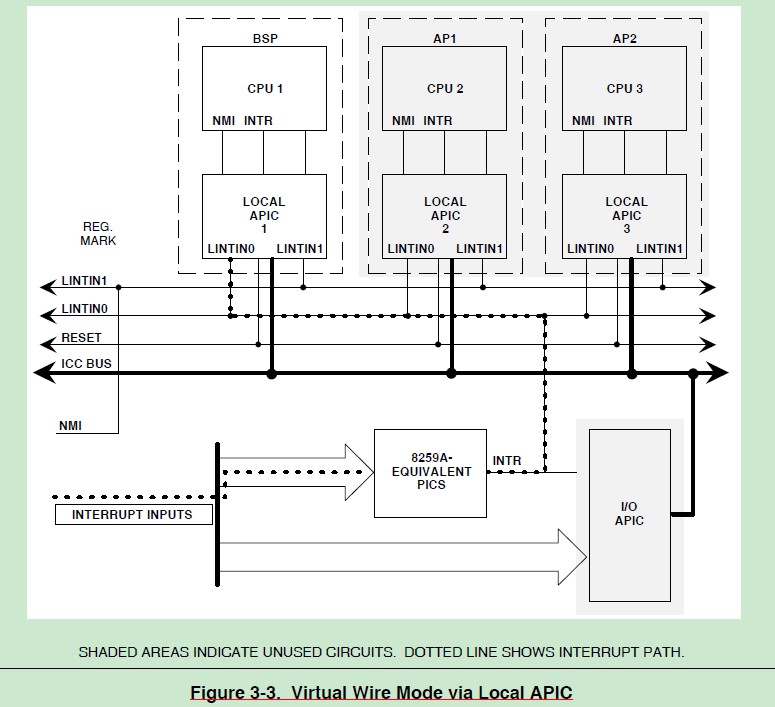

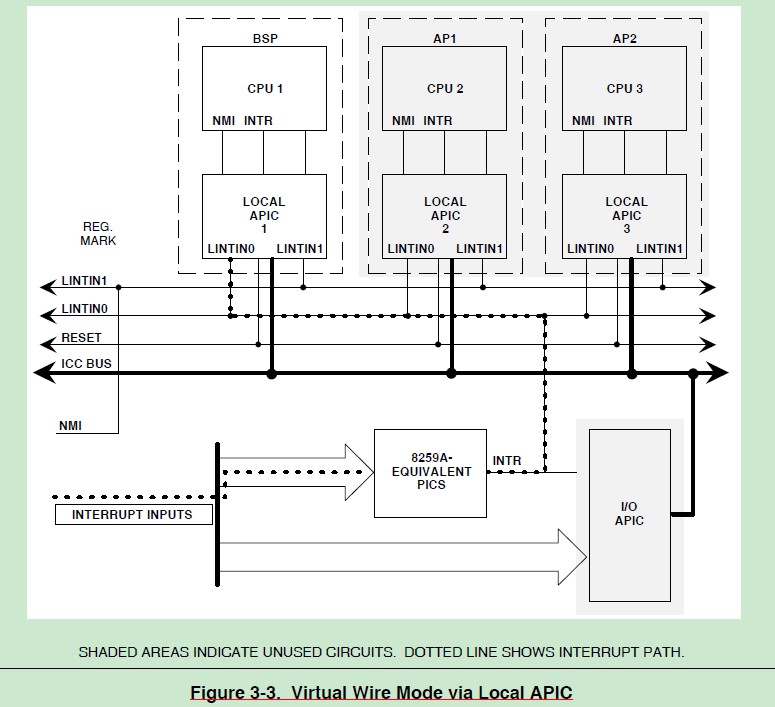

In Virtual Wire Mode, as shown in Figure 3-3, the 8259A-equivalent PIC fields all interrupts, and

3.6.2.2 Virtual Wire Mode

In Virtual Wire Mode, as shown in Figure 3-3, the 8259A-equivalent PIC fields all interrupts, and

the local APIC of the BSP becomes a virtual wire, which delivers interrupts from the PIC to the

BSP via the local APIC’s local interrupt 0 (LINTIN0). The LINTIN0 pin of the local APIC is

programmed as ExtINT, specifying to the APIC that the PIC is to serve as an external interrupt

controller. Whenever the local APIC finds that a particular interrupt is of type ExtINT, it asserts

the ExtINTA transaction along with the PINT interrupt to the processor. In this case, the I/O APIC

is not used. Figure 3-3 shows how Virtual Wire Mode can be implemented through the BSP’s local APIC. It is

Figure 3-3 shows how Virtual Wire Mode can be implemented through the BSP’s local APIC. It is

also permissible to program the I/O APIC for Virtual Wire Mode, as shown in Figure 3-4. In this

case the interrupt signal passes through both the I/O APIC and the BSP’s local APIC. 3.6.2.3 Symmetric I/O Mode

Some MP operating systems operate in Symmetric I/O Mode. This mode requires at least one I/O

3.6.2.3 Symmetric I/O Mode

Some MP operating systems operate in Symmetric I/O Mode. This mode requires at least one I/O

APIC to operate. In this mode, I/O interrupts are generated by the I/O APIC. All 8259 interrupt

lines are either masked or work together with the I/O APIC in a mixed mode. See Figure 3-5 for

an overview of Symmetric I/O Mode.

PIC Mode is software compatible with the PC/AT because it actually employs the same hardware

interrupt configuration. As Figure 3-2 illustrates, the hardware for PIC Mode bypasses the APIC

components by using an interrupt mode configuration register (IMCR). This register controls

whether the interrupt signals that reach the BSP come from the master PIC or from the local APIC.

Before entering Symmetric I/O Mode, either the BIOS or the operating system must switch out of

PIC Mode by changing the IMCR.

3.6.2.2 Virtual Wire Mode

In Virtual Wire Mode, as shown in Figure 3-3, the 8259A-equivalent PIC fields all interrupts, and

3.6.2.2 Virtual Wire Mode

In Virtual Wire Mode, as shown in Figure 3-3, the 8259A-equivalent PIC fields all interrupts, andthe local APIC of the BSP becomes a virtual wire, which delivers interrupts from the PIC to the

BSP via the local APIC’s local interrupt 0 (LINTIN0). The LINTIN0 pin of the local APIC is

programmed as ExtINT, specifying to the APIC that the PIC is to serve as an external interrupt

controller. Whenever the local APIC finds that a particular interrupt is of type ExtINT, it asserts

the ExtINTA transaction along with the PINT interrupt to the processor. In this case, the I/O APIC

is not used.

Figure 3-3 shows how Virtual Wire Mode can be implemented through the BSP’s local APIC. It is

Figure 3-3 shows how Virtual Wire Mode can be implemented through the BSP’s local APIC. It isalso permissible to program the I/O APIC for Virtual Wire Mode, as shown in Figure 3-4. In this

case the interrupt signal passes through both the I/O APIC and the BSP’s local APIC.

3.6.2.3 Symmetric I/O Mode

Some MP operating systems operate in Symmetric I/O Mode. This mode requires at least one I/O

3.6.2.3 Symmetric I/O Mode

Some MP operating systems operate in Symmetric I/O Mode. This mode requires at least one I/OAPIC to operate. In this mode, I/O interrupts are generated by the I/O APIC. All 8259 interrupt

lines are either masked or work together with the I/O APIC in a mixed mode. See Figure 3-5 for

an overview of Symmetric I/O Mode.