系统外设通过生成中断要求CPU的响应。每个外设都有一个或多个绑定到可编程中断控制器(Programmable Interrupt Controller,PIC)的中断线,PIC将把未完成的中断集中到CPU。ARM核心只有两种中断输入,即普通中断请求(normal Interrupt ReQuest,IRQ)和快速中断请求(Fast Interrupt reQuest,FIQ)。FIQ的优先级比IRQ高,它还有额外的备份寄存器。

EKA2中断分发代码通过读PIC寄存器确定中断源,然后调用正确的服务函数。第六章中断和异常对此进行了解释。

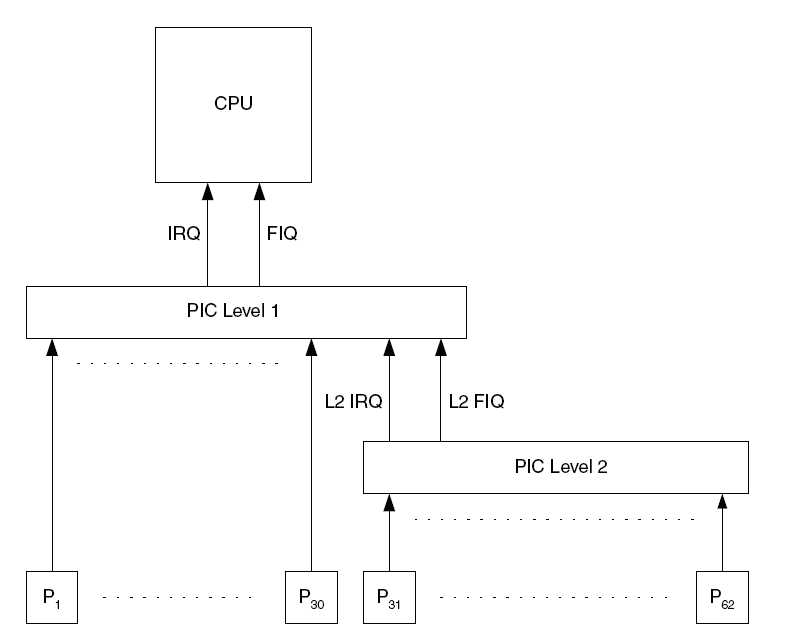

在图2.4中,可以看到一个62中断系统,这种设计包含两层,它重复使用同样的PIC块以把第二级串联到第一级。

图2.4 两层中断控制器

层内的每个中断用控制寄存器内部32比特位中的一个进行表示。这个寄存器允许中断分发软件设定、激活和纠正中断:

中断类型

IRQ

FIQ

输出状态

True

False

是否激活

True

False

锁存中断输入

True

False

侦测类型

Edge

Level

极性

Rising

Edge/High Level

Falling

Edge/Low Level

下面是一些使用中的中断类型的例子:

串行端口输出FIFO有半空的设置,只要在FIFO里有空间,它所产生的优先级都是高等级。只要中断设备程序往FIFO里被写满了数据,就会产生中断输出。

上升沿中断被用来侦测LCD控制器在一个新的输出流开始时发出的VSync脉冲。

为了确定当前未完成的中断,分发器必须读取状态,从PIC激活寄存器,然后把它们进行与运算,并找到设置比特位以决定分发哪一个中断。比特数被用来对函数指针表进行索引以修正中断服务程序(interrupt service routine,ISR)。把最高优先级的中断放到1级的最高位,第一个合法比特位可以很快地用计算前导零(count leading zeros,CLZ)指令发现。

中断分发延迟,是介于发出一个IRQ输入和在ISR中执行第一个指令之间的一个时间值,这个时间也是上段文字中所描述的软件分发器和前导码线程所花费的时间。这段时间内要运行数十条指令,导致一个50周期的中断消耗,或者是在200MHz核心花费250纳秒。如果考虑到后同步码和内核分发器,一次中断的总开销将接近1微秒。

你可以使用更成熟的PIC以减少中断延迟。比如,分发软件用一个可以马上使用的包含最高优先级中断数的状态寄存器以取代位模式。

ARM矢量中断控制器(Vectored Interrupt Controller,VIC)是一个更复杂的系统,CPU在这个系统上有专用的VIC端口。VIC允许往CPU里直接注入ISR地址,以消除软件中断分发的总开销,并在每个中断上节省了数十个周期。但Symbian OS电话不需要VIC和相关的硅复杂性,它们也没有毫微秒级延迟的硬实时中断。

在设计电话的时候,应该志在减少系统内活动中断的数量,因为这样做会增强全局系统中断响应的健壮性并减少电量消耗。为达到这个目的,可以使用DMA接口外设,而不是从快速计时器中轮询(polling)外设。

=====================================================================================

说明: 本文由Bequan翻译自Symbian Press的Symbian OS Internals: Real-time Kernal Programming一书。任何人需要转载或引用,请先通过Email(a-pangu@163.com或symbianchn@gmail.com)与Bequan联系,在获得许可后方可转载或引用,否则视为侵权行为。转载或引用时,请在文章中注明上述翻译信息。

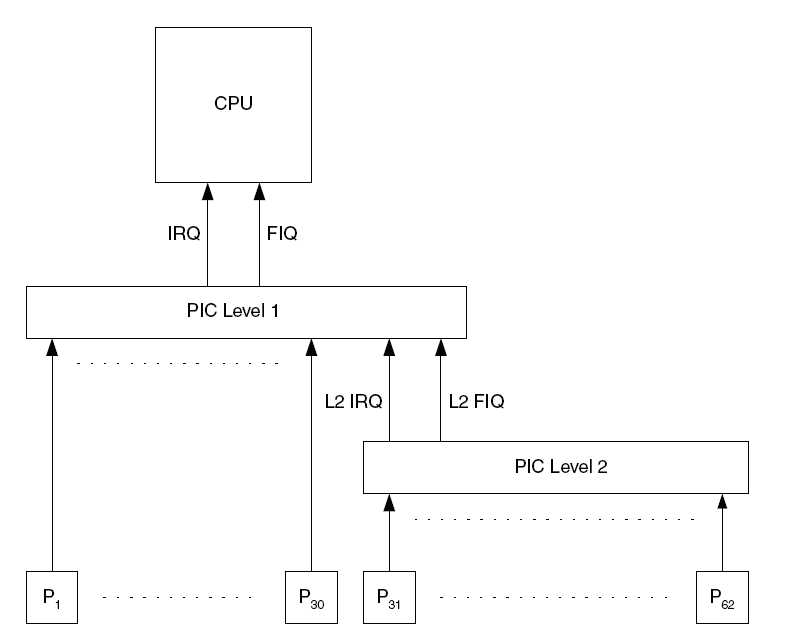

图2.4 两层中断控制器

层内的每个中断用控制寄存器内部32比特位中的一个进行表示。这个寄存器允许中断分发软件设定、激活和纠正中断:

中断类型

IRQ

FIQ

输出状态

True

False

是否激活

True

False

锁存中断输入

True

False

侦测类型

Edge

Level

极性

Rising

Edge/High Level

Falling

Edge/Low Level

下面是一些使用中的中断类型的例子:

串行端口输出FIFO有半空的设置,只要在FIFO里有空间,它所产生的优先级都是高等级。只要中断设备程序往FIFO里被写满了数据,就会产生中断输出。

上升沿中断被用来侦测LCD控制器在一个新的输出流开始时发出的VSync脉冲。

为了确定当前未完成的中断,分发器必须读取状态,从PIC激活寄存器,然后把它们进行与运算,并找到设置比特位以决定分发哪一个中断。比特数被用来对函数指针表进行索引以修正中断服务程序(interrupt service routine,ISR)。把最高优先级的中断放到1级的最高位,第一个合法比特位可以很快地用计算前导零(count leading zeros,CLZ)指令发现。

中断分发延迟,是介于发出一个IRQ输入和在ISR中执行第一个指令之间的一个时间值,这个时间也是上段文字中所描述的软件分发器和前导码线程所花费的时间。这段时间内要运行数十条指令,导致一个50周期的中断消耗,或者是在200MHz核心花费250纳秒。如果考虑到后同步码和内核分发器,一次中断的总开销将接近1微秒。

你可以使用更成熟的PIC以减少中断延迟。比如,分发软件用一个可以马上使用的包含最高优先级中断数的状态寄存器以取代位模式。

ARM矢量中断控制器(Vectored Interrupt Controller,VIC)是一个更复杂的系统,CPU在这个系统上有专用的VIC端口。VIC允许往CPU里直接注入ISR地址,以消除软件中断分发的总开销,并在每个中断上节省了数十个周期。但Symbian OS电话不需要VIC和相关的硅复杂性,它们也没有毫微秒级延迟的硬实时中断。

在设计电话的时候,应该志在减少系统内活动中断的数量,因为这样做会增强全局系统中断响应的健壮性并减少电量消耗。为达到这个目的,可以使用DMA接口外设,而不是从快速计时器中轮询(polling)外设。

=====================================================================================

说明: 本文由Bequan翻译自Symbian Press的Symbian OS Internals: Real-time Kernal Programming一书。任何人需要转载或引用,请先通过Email(a-pangu@163.com或symbianchn@gmail.com)与Bequan联系,在获得许可后方可转载或引用,否则视为侵权行为。转载或引用时,请在文章中注明上述翻译信息。

图2.4 两层中断控制器

层内的每个中断用控制寄存器内部32比特位中的一个进行表示。这个寄存器允许中断分发软件设定、激活和纠正中断:

中断类型

IRQ

FIQ

输出状态

True

False

是否激活

True

False

锁存中断输入

True

False

侦测类型

Edge

Level

极性

Rising

Edge/High Level

Falling

Edge/Low Level

下面是一些使用中的中断类型的例子:

串行端口输出FIFO有半空的设置,只要在FIFO里有空间,它所产生的优先级都是高等级。只要中断设备程序往FIFO里被写满了数据,就会产生中断输出。

上升沿中断被用来侦测LCD控制器在一个新的输出流开始时发出的VSync脉冲。

为了确定当前未完成的中断,分发器必须读取状态,从PIC激活寄存器,然后把它们进行与运算,并找到设置比特位以决定分发哪一个中断。比特数被用来对函数指针表进行索引以修正中断服务程序(interrupt service routine,ISR)。把最高优先级的中断放到1级的最高位,第一个合法比特位可以很快地用计算前导零(count leading zeros,CLZ)指令发现。

中断分发延迟,是介于发出一个IRQ输入和在ISR中执行第一个指令之间的一个时间值,这个时间也是上段文字中所描述的软件分发器和前导码线程所花费的时间。这段时间内要运行数十条指令,导致一个50周期的中断消耗,或者是在200MHz核心花费250纳秒。如果考虑到后同步码和内核分发器,一次中断的总开销将接近1微秒。

你可以使用更成熟的PIC以减少中断延迟。比如,分发软件用一个可以马上使用的包含最高优先级中断数的状态寄存器以取代位模式。

ARM矢量中断控制器(Vectored Interrupt Controller,VIC)是一个更复杂的系统,CPU在这个系统上有专用的VIC端口。VIC允许往CPU里直接注入ISR地址,以消除软件中断分发的总开销,并在每个中断上节省了数十个周期。但Symbian OS电话不需要VIC和相关的硅复杂性,它们也没有毫微秒级延迟的硬实时中断。

在设计电话的时候,应该志在减少系统内活动中断的数量,因为这样做会增强全局系统中断响应的健壮性并减少电量消耗。为达到这个目的,可以使用DMA接口外设,而不是从快速计时器中轮询(polling)外设。

=====================================================================================

说明: 本文由Bequan翻译自Symbian Press的Symbian OS Internals: Real-time Kernal Programming一书。任何人需要转载或引用,请先通过Email(a-pangu@163.com或symbianchn@gmail.com)与Bequan联系,在获得许可后方可转载或引用,否则视为侵权行为。转载或引用时,请在文章中注明上述翻译信息。

图2.4 两层中断控制器

层内的每个中断用控制寄存器内部32比特位中的一个进行表示。这个寄存器允许中断分发软件设定、激活和纠正中断:

中断类型

IRQ

FIQ

输出状态

True

False

是否激活

True

False

锁存中断输入

True

False

侦测类型

Edge

Level

极性

Rising

Edge/High Level

Falling

Edge/Low Level

下面是一些使用中的中断类型的例子:

串行端口输出FIFO有半空的设置,只要在FIFO里有空间,它所产生的优先级都是高等级。只要中断设备程序往FIFO里被写满了数据,就会产生中断输出。

上升沿中断被用来侦测LCD控制器在一个新的输出流开始时发出的VSync脉冲。

为了确定当前未完成的中断,分发器必须读取状态,从PIC激活寄存器,然后把它们进行与运算,并找到设置比特位以决定分发哪一个中断。比特数被用来对函数指针表进行索引以修正中断服务程序(interrupt service routine,ISR)。把最高优先级的中断放到1级的最高位,第一个合法比特位可以很快地用计算前导零(count leading zeros,CLZ)指令发现。

中断分发延迟,是介于发出一个IRQ输入和在ISR中执行第一个指令之间的一个时间值,这个时间也是上段文字中所描述的软件分发器和前导码线程所花费的时间。这段时间内要运行数十条指令,导致一个50周期的中断消耗,或者是在200MHz核心花费250纳秒。如果考虑到后同步码和内核分发器,一次中断的总开销将接近1微秒。

你可以使用更成熟的PIC以减少中断延迟。比如,分发软件用一个可以马上使用的包含最高优先级中断数的状态寄存器以取代位模式。

ARM矢量中断控制器(Vectored Interrupt Controller,VIC)是一个更复杂的系统,CPU在这个系统上有专用的VIC端口。VIC允许往CPU里直接注入ISR地址,以消除软件中断分发的总开销,并在每个中断上节省了数十个周期。但Symbian OS电话不需要VIC和相关的硅复杂性,它们也没有毫微秒级延迟的硬实时中断。

在设计电话的时候,应该志在减少系统内活动中断的数量,因为这样做会增强全局系统中断响应的健壮性并减少电量消耗。为达到这个目的,可以使用DMA接口外设,而不是从快速计时器中轮询(polling)外设。

=====================================================================================

说明: 本文由Bequan翻译自Symbian Press的Symbian OS Internals: Real-time Kernal Programming一书。任何人需要转载或引用,请先通过Email(a-pangu@163.com或symbianchn@gmail.com)与Bequan联系,在获得许可后方可转载或引用,否则视为侵权行为。转载或引用时,请在文章中注明上述翻译信息。