1.时钟结构图

图1 片内时钟结构图

图1 片内时钟结构图2.时钟分配

有三种方式可为5744提供时钟源,分别为外部有源晶振、外部无源晶振和内部16MHz RC晶振。其中16MHz内部RC晶振一般作为PLL或外部晶振失效情况下的备用时钟,系统复位后5744默认选择16MHz内部RC晶振作为时钟源。5744内含有PLL0和PLL1两个PLL,PLL0输出为PLL0_PHI、PLL0_PHI1,PLL1输出为PLL1_PHI,其中PLL0_PHI1还可以作为PLL1的输入时钟。选择的时钟源经过PLL后可为系统和片内外设提供时钟。系统和片内外设可利用对应AUX Clock Selector选择不同的时钟源,在选择好时钟源之后可根据对应的Divider分频器来获取不同频率的时钟。

3.频率限制

5744对系统和片内外设时钟做了限制,在设置时不应超过对应的时钟限制值,各个模块的最高时钟频率如下:

表1 系统和片内外设频率限制表

表1 系统和片内外设频率限制表4.时钟选择和分频因子

5744利用MC_CGM模块对系统和片内外设进行时钟源的选择和分频因子的设置,主要包含图1中的各个AUX Clock Selector和Divider。

图2 系统和外设时钟时钟源选择和分频控制模块

图2 系统和外设时钟时钟源选择和分频控制模块5.系统时钟配置

1.Mode Entry Module(MC_ME)

5744可对各个模块进行使能和失能以进行能耗管理,默认情况下一些模块处于失能状态,在使用该模块时需要对其使能。5744通过Mode Entry Module(MC_ME)对各个片内外设模块进行管理。MC_ME的模块如下:

图3 MC_ME模块图

图3 MC_ME模块图 5744一共有RESET、TEST、SAFE、DRUN、RUN0-3、HALT0、STOP0等运行模式,其中RESET_FUNC、SAFE、 DRUN、 RUN0、 RESET_DEST模式总是使能,若使用其他模式需要实时MC_ME_ME使能。各个模式可以互相转换,可以通过MC_ME_MODEx_MC寄存器对外设有不同的设置。在系统时钟设置时,我们应先选择想要的运行模式,然后设置对应的MC_ME_MODEx_MC寄存起对外设配置,然后转换到对应的运行模式。

2.PLL配置

由图3 MC_ME模块图可知外部晶振XOSC、PLL0和PLL1由MC_ME控制,PLL0、PLL1的时钟源选择有MC_CGM控制,则PLL配置步骤如下:

1)选择运行模式;

2)关闭XOSC、PLLs(配置MC_ME.MODEx_MC寄存器,MODEx为1中所选的运行模式)

3)配置分频和倍频因子(配置PLLDIG_PLL0DV、PLLDIG_PLL1DV寄存器);

4)利用MC_CGM模块选择时钟源(配置MC_CGM.ACx_SC);

5)利用MC_ME使能对应模块(XOSC、PLLs);

6)进行模式转换。

3.PLL参数的计算

5744对PLL的输入输出频率有所限制,PLL0的输入频率应为8~56MHz,输出应为4.762~625MHz;PLL1的输入频率应为37.5~78.125MHz,输出应为4.764~625MHz,此外还有一个重要限制为PLL内部Fvco的频率范围为600~1250MHz 。

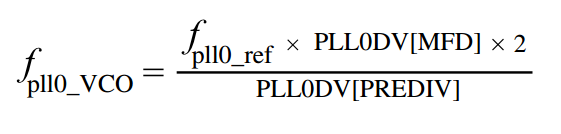

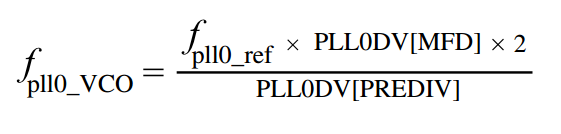

PLL0的计算公式如下:

其中fpll0_ref为PLL0所选时钟源的时钟频率,fpll0_phi,fpll0_phi1分别为PLL0输出PHI和PHI1非频率

PLL1的计算公式如下:

其中fpll1_ref为PLL1的输入时钟频率,

若不使能PLLDIG_PLL1FD寄存器,默认情况下不使能,则PLL1计算公式可简化为

fpll1_VCO = fpll1_ref × PLL1DV[MFD]

fpll1_phi = fpll1_ref × PLL1DV[MFD] / ( 2 * PLL1DV[RFDPHI ] )

4.示例代码

/*******************************************

* 函数名 CLOCK_Config_System_180mhz

* 功能 配置系统时钟为180mhz

* 输入参数 无

* 返回值 无

* 示例 CLOCK_Config_System_180mhz();//配置系统时钟为180mhz

*******************************************

*/

static void CLOCK_Config_System_180mhz()

{

//PLL0设置

MC_ME.RUN0_MC.R&=0xFFFFFF9F; //关闭PLL0,XOSC,需以字访问

//PLL0分频倍频因子配置

//配置Fpll0_phi=Fref*MFD/(PREDIV*RFDPHI)=40*24/(2*4)=120Mhz

//配置Fpll0_phi1=Fref*MFD/(PREDIV*RFDPHI*2)=40*24/(2*8)=60Mhz

PLLDIG.PLL0DV.B.MFD=24;

PLLDIG.PLL0DV.B.PREDIV=2;

PLLDIG.PLL0DV.B.RFDPHI=4;

PLLDIG.PLL0DV.B.RFDPHI1=8;

MC_CGM.AC3_SC.B.SELCTL=1; //选择XOSC作为PLL0时钟

MC_ME.RUN0_MC.R|=0x00000020; //打开XOSC,需以字访问

MC_CGM.AC4_SC.B.SELCTL=3; //选择PLL0_PHI1作为PLL1时钟源

MC_ME.RUN0_MC.R|=0x00000040; //打开PLL0,需以字访问

//模式转换

//选择目标运行模式为RUN0,并设置KEY,该寄存器只能以字访问

MC_ME.MCTL.R = 0x40005AF0;

//选择目标运行模式为RUN0,并设置反转KEY,该寄存器只能以字访问

MC_ME.MCTL.R = 0x4000A50F;

while(MC_ME.GS.B.S_MTRANS);

while(MC_ME.GS.B.S_CURRENT_MODE!=4); //转换到RUN0模式并等待模式转换完成

//PLL1设置

MC_ME.RUN0_MC.R&=0xFFFFFF7F; //关闭PLL1

/PLL1分频倍频因子设定

//配置Fpll1_phi=Fref*MFD/(RFDPHI*2)=60*18/(2*3)=180Mhz

PLLDIG.PLL1DV.B.MFD=18;

PLLDIG.PLL1DV.B.RFDPHI=3;

//设置运行外设配置模式寄存器0,表示外设全模式运行,不同外设可选择不同的配置寄存器

//该寄存器有8个

MC_ME.RUN_PC[0].R=0x000000FE;

MC_ME.RUN0_MC.R|=0x00000080; //打开PLL1,需以字访问

MC_ME.RUN0_MC.R&=0xFFFFFFF0;

MC_ME.RUN0_MC.R|=0x00000004; //选择PLL1_PHI作为系统时钟源,需以字访问

//模式转换

//选择目标运行模式为RUN0,并设置KEY,该寄存器只能以字访问

MC_ME.MCTL.R = 0x40005AF0 ;

//选择目标运行模式为RUN0,并设置反转KEY,该寄存器只能以字访问

MC_ME.MCTL.R = 0x4000A50F;

while(MC_ME.GS.B.S_MTRANS);

while(MC_ME.GS.B.S_CURRENT_MODE!=4); //转换到RUN0模式并等待模式转换完成

//等待XOSC、PLL0、PLL1稳定

while((!MC_ME.GS.B.S_XOSC)||(!MC_ME.GS.B.S_PLL0)||(!MC_ME.GS.B.S_PLL1));

}

6.片内外设时钟配置

在系统时钟配置完成后,需要进行片内外设时钟的配置,片内外设的时钟结构如下图:

由于大部分外设挂在外设桥上,所以通过配置外设桥即可。ADC模块除了需要配置外设桥,还需要配置单独ADC_CLK时钟。

在系统时钟配置完成的情况下,外设时钟只需要通过选择时钟源,设置分配因子即可获得所需频率的时钟,则配置步骤如下:

1)通过MC_CGM.ACx_DCx使能分频因子并设置分频因子数值。

2)通过MC_CGM.ACx_SCx_选择所采用的时钟源。

所需要的Aux Clock Selector和Aux Clock Divider可根据所配置的外设在图1查得。

1.外设桥时钟配置

由于外设桥时钟源直接选为系统时钟,故不需要进行时钟源的选择,直接对分频寄存器进行操作即可,代码如下:

**************************************

* 函数名 CLOCK_Config_Peripheral_Bridge_45mhz

* 功能 配置外设桥时钟频率为45mhz

* 输入参数 无

* 返回值 无

* 示例 CLOCK_Config_Peripheral_Bridge_45mhz();//配置外设桥频率为45mhz

*/

static void CLOCK_Config_Peripheral_Bridge_45mhz()

{

//该寄存器只能以字访问,设置PA_CLK=PB_CLK=SYS_CLK/(3+1)=180mhz/4=45mhz

//PB_CLK,PA_CLK频率最高为45mhz

MC_CGM.SC_DC0.R=0x80030000;

}

2.ADC_CLK的配置

ADC模块除一般外设桥时钟外,还需配置ADC_CLK时钟,代码如下:

/**************************************

* 函数名 CLOCK_Config_ADC_60mhz

* 功能 配置ADC模块时钟频率为60mhz

* 输入参数 无

* 返回值 无

* 示例 CLOCK_Config_ADC_60mhz();//配置ADC模块时钟频率为60mhz

*/

static void CLOCK_Config_ADC_60mhz()

{

//使能DC0,DIV=1,CLK_ADC=CLK_PLL0_PHI/(1+1)=120Mhz/2=60mhz

MC_CGM.AC0_DC2.R=0x80010000;

MC_CGM.AC0_SC.B.SELCTL=2; //选择PLL0 PHI作为时钟源

}

其中fpll0_ref为PLL0所选时钟源的时钟频率,fpll0_phi,fpll0_phi1分别为PLL0输出PHI和PHI1非频率

PLL1的计算公式如下:

其中fpll0_ref为PLL0所选时钟源的时钟频率,fpll0_phi,fpll0_phi1分别为PLL0输出PHI和PHI1非频率

PLL1的计算公式如下:

其中fpll1_ref为PLL1的输入时钟频率,若不使能PLLDIG_PLL1FD寄存器,默认情况下不使能,则PLL1计算公式可简化为

fpll1_VCO = fpll1_ref × PLL1DV[MFD]

fpll1_phi = fpll1_ref × PLL1DV[MFD] / ( 2 * PLL1DV[RFDPHI ] )

4.示例代码

其中fpll1_ref为PLL1的输入时钟频率,若不使能PLLDIG_PLL1FD寄存器,默认情况下不使能,则PLL1计算公式可简化为

fpll1_VCO = fpll1_ref × PLL1DV[MFD]

fpll1_phi = fpll1_ref × PLL1DV[MFD] / ( 2 * PLL1DV[RFDPHI ] )

4.示例代码

由于大部分外设挂在外设桥上,所以通过配置外设桥即可。ADC模块除了需要配置外设桥,还需要配置单独ADC_CLK时钟。

在系统时钟配置完成的情况下,外设时钟只需要通过选择时钟源,设置分配因子即可获得所需频率的时钟,则配置步骤如下:

1)通过MC_CGM.ACx_DCx使能分频因子并设置分频因子数值。

2)通过MC_CGM.ACx_SCx_选择所采用的时钟源。

所需要的Aux Clock Selector和Aux Clock Divider可根据所配置的外设在图1查得。

1.外设桥时钟配置

由于外设桥时钟源直接选为系统时钟,故不需要进行时钟源的选择,直接对分频寄存器进行操作即可,代码如下:

由于大部分外设挂在外设桥上,所以通过配置外设桥即可。ADC模块除了需要配置外设桥,还需要配置单独ADC_CLK时钟。

在系统时钟配置完成的情况下,外设时钟只需要通过选择时钟源,设置分配因子即可获得所需频率的时钟,则配置步骤如下:

1)通过MC_CGM.ACx_DCx使能分频因子并设置分频因子数值。

2)通过MC_CGM.ACx_SCx_选择所采用的时钟源。

所需要的Aux Clock Selector和Aux Clock Divider可根据所配置的外设在图1查得。

1.外设桥时钟配置

由于外设桥时钟源直接选为系统时钟,故不需要进行时钟源的选择,直接对分频寄存器进行操作即可,代码如下: