2440的时钟模块如下图(2440芯片手册237页) ,下载链接见上一篇博客。

S3C2440可以使用外部晶振(XTIpll)(默认为12MHZ)

S3C2440可以使用外部晶振(XTIpll)(默认为12MHZ)

和外部时钟(EXTCLK)两种方式输入时钟信号。它由跳

线OM[3:2]决定。 S3C2440 默认的工作主频为12MHz

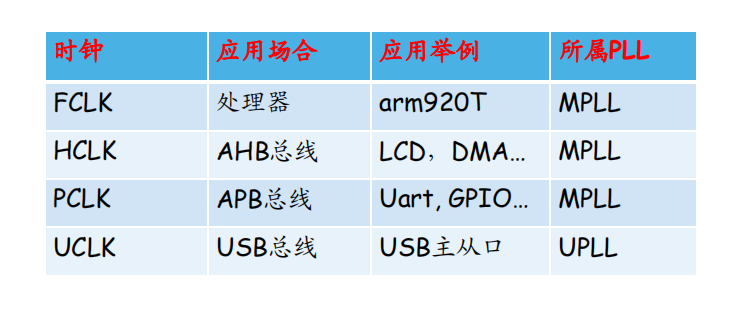

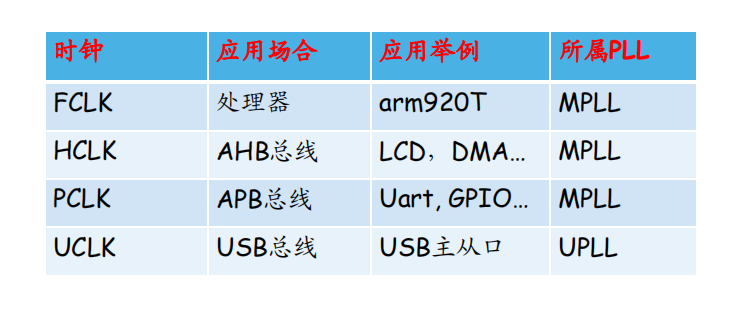

(晶振频率),S3C2440有两个PLL:MPLL和UPLL。通

过MPLL会产生三个部分的时钟频率:FCLK、HCLK、

PLCK。UPLL则负责产生USB所需时钟UCLK。如下图 开发板上电后,时钟初始化流程如下图,刚通电时,FCLK为晶振频率12MHz,经过软件配置及Lock Time之后,FCLK变为高频(本例中为405MHz)。

开发板上电后,时钟初始化流程如下图,刚通电时,FCLK为晶振频率12MHz,经过软件配置及Lock Time之后,FCLK变为高频(本例中为405MHz)。

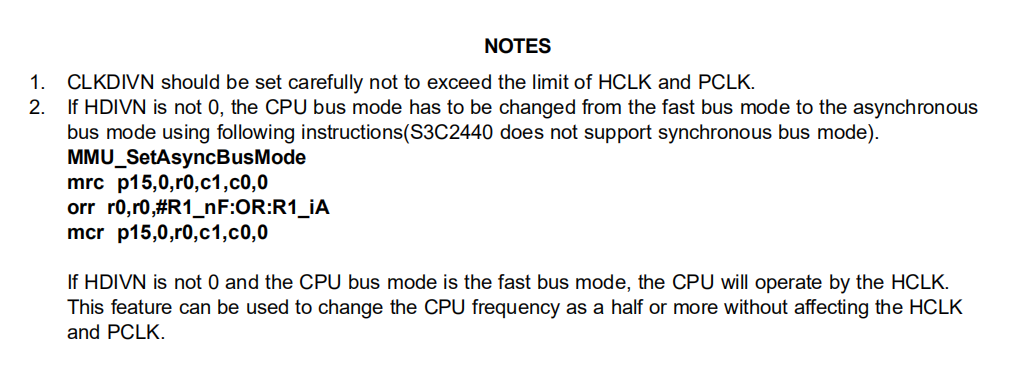

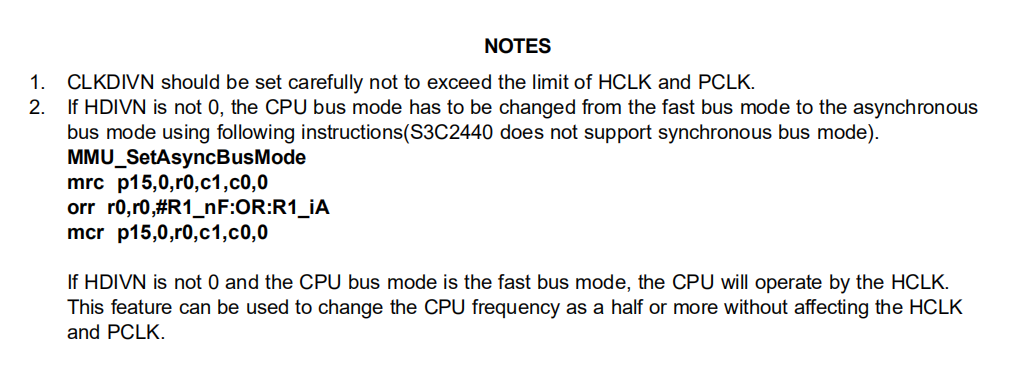

从2440芯片手册243页可以看到下图所示的信息

从2440芯片手册243页可以看到下图所示的信息

于是,可以总结出时钟初始化的流程:

于是,可以总结出时钟初始化的流程:

设置分频系数所使用的寄存器如下图所示,(2440芯片手册258页)

设置分频系数所使用的寄存器如下图所示,(2440芯片手册258页)

S3C2440可以使用外部晶振(XTIpll)(默认为12MHZ)

S3C2440可以使用外部晶振(XTIpll)(默认为12MHZ)和外部时钟(EXTCLK)两种方式输入时钟信号。它由跳

线OM[3:2]决定。 S3C2440 默认的工作主频为12MHz

(晶振频率),S3C2440有两个PLL:MPLL和UPLL。通

过MPLL会产生三个部分的时钟频率:FCLK、HCLK、

PLCK。UPLL则负责产生USB所需时钟UCLK。如下图

开发板上电后,时钟初始化流程如下图,刚通电时,FCLK为晶振频率12MHz,经过软件配置及Lock Time之后,FCLK变为高频(本例中为405MHz)。

开发板上电后,时钟初始化流程如下图,刚通电时,FCLK为晶振频率12MHz,经过软件配置及Lock Time之后,FCLK变为高频(本例中为405MHz)。

从2440芯片手册243页可以看到下图所示的信息

从2440芯片手册243页可以看到下图所示的信息

于是,可以总结出时钟初始化的流程:

于是,可以总结出时钟初始化的流程:

配置Lock Time —》 设置分频系数 —》设置CPU总线模式为异步模式 —》 设置FCLK

首先,

设置Lock Time的寄存器如下图,(2440芯片手册254页)。但由于Lock Time一般取默认值,所以可以省去“配置Lock Time”这一步骤。

之后,

2440设置FCLK、PCLK、HCLK的比例关系如下图所示,本例选1:4:8的比例。(2440芯片手册242页)。 设置分频系数所使用的寄存器如下图所示,(2440芯片手册258页)

设置分频系数所使用的寄存器如下图所示,(2440芯片手册258页)

接下来,

根据243页的NOTES,将CPU总线模式设置为异步模式。最后,

设置FCLK的寄存器如下图(2440芯片手册第255页)

得到以上信息后,时钟初始化的代码如下

#define CLKDIVN 0x4c000014

#define MPLLCON 0x4c000004

#define MPLL_405MHZ ((127<<12)|(2<<4)|(1<<0))

init_clock:

ldr r0, =CLKDIVN

mov r1, #0x5

str r1, [r0]

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000

mcr p15,0,r0,c1,c0,0

ldr r0, =MPLLCON

ldr r1, =MPLL_405MHZ

str r1, [r0]

mov pc, lr