参考:https://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus

SPI(Serial Peripheral Interface)是一种用于短距离的同步串行通信协议,由Motorola开发。

SPI通常需要4根总线,即SCK、MOSI、MISO、SS。

SCK是时钟信号,由主机输出,MOSI即Master Output Slave Input、MISO即Master Input Slave Output,用于数据的传输,而SS是Slave Select,是设备的片选信号,低有效,也为一个主机接多个从设备成为可能。

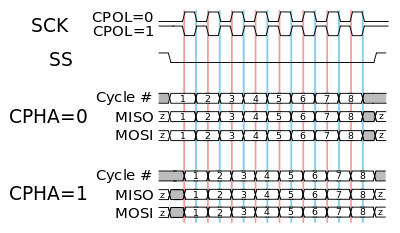

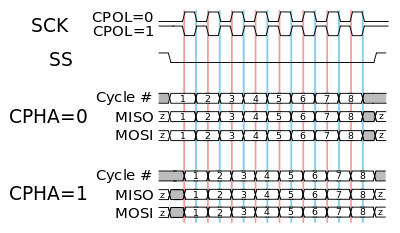

Clock的极性和相位。

1. 极性(CPOL)

CPOL=0,表示Clock空闲时电平是低电平,高电平时Clock有效。

CPOL=1,表示Clock空闲时电平是高电平,低电平时Clock有效。

2. 相位(CPHA)

SPI数据采样都是边沿采样,即上升沿或下降沿,所以这里的CPHA表示是第一个边沿采样还是第二个边沿采样。

CPOL=0、CPHA=0表示第一个边沿上升沿采样。

CPOL=0、CPHA=1表示第二个边沿下降沿采样。

CPOL=1、CPHA=0表示第一个边沿下降沿采样。

CPOL=1、CPHA=1表示第二个边沿上升沿采样。

SPI极性、相位时序图如下:

根据极性和相位共有4中组合,也就是SPI的工作模式。

Mode 0 CPOL=0 CPHA=0

Mode 1 CPOL=0 CPHA=1

Mode 2 CPOL=1 CPHA=0

Mode 3 CPOL=1 CPHA=1

例程:

// 2017-09-04 add

通常SPI的接口的屏会说到3线SPI、4线SPI,那么有什么区别呢?

这个要根据IC的数据手册来看了,通常3线SPI包括SCLK、SDIN、CS,如果是4线SPI的话,多一个DC引脚,这个引脚用来控制发送的是数据还是命令。

SPI(Serial Peripheral Interface)是一种用于短距离的同步串行通信协议,由Motorola开发。

SPI通常需要4根总线,即SCK、MOSI、MISO、SS。

SCK是时钟信号,由主机输出,MOSI即Master Output Slave Input、MISO即Master Input Slave Output,用于数据的传输,而SS是Slave Select,是设备的片选信号,低有效,也为一个主机接多个从设备成为可能。

Clock的极性和相位。

1. 极性(CPOL)

CPOL=0,表示Clock空闲时电平是低电平,高电平时Clock有效。

CPOL=1,表示Clock空闲时电平是高电平,低电平时Clock有效。

2. 相位(CPHA)

SPI数据采样都是边沿采样,即上升沿或下降沿,所以这里的CPHA表示是第一个边沿采样还是第二个边沿采样。

CPOL=0、CPHA=0表示第一个边沿上升沿采样。

CPOL=0、CPHA=1表示第二个边沿下降沿采样。

CPOL=1、CPHA=0表示第一个边沿下降沿采样。

CPOL=1、CPHA=1表示第二个边沿上升沿采样。

SPI极性、相位时序图如下:

根据极性和相位共有4中组合,也就是SPI的工作模式。

Mode 0 CPOL=0 CPHA=0

Mode 1 CPOL=0 CPHA=1

Mode 2 CPOL=1 CPHA=0

Mode 3 CPOL=1 CPHA=1

例程:

/*

* Simultaneously transmit and receive a byte on the SPI.

*

* Polarity and phase are assumed to be both 0, i.e.:

* - input data is captured on rising edge of SCLK.

* - output data is propagated on falling edge of SCLK.

*

* Returns the received byte.

*/

uint8_t SPI_transfer_byte(uint8_t byte_out)

{

uint8_t byte_in = 0;

uint8_t bit;

for (bit = 0x80; bit; bit >>= 1) {

/* Shift-out a bit to the MOSI line */

write_MOSI((byte_out & bit) ? HIGH : LOW);

/* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME);

/* Pull the clock line high */

write_SCLK(HIGH);

/* Shift-in a bit from the MISO line */

if (read_MISO() == HIGH)

byte_in |= bit;

/* Delay for at least the peer's hold time */

delay(SPI_SCLK_HIGH_TIME);

/* Pull the clock line low */

write_SCLK(LOW);

}

return byte_in;

}

// 2017-09-04 add

通常SPI的接口的屏会说到3线SPI、4线SPI,那么有什么区别呢?

这个要根据IC的数据手册来看了,通常3线SPI包括SCLK、SDIN、CS,如果是4线SPI的话,多一个DC引脚,这个引脚用来控制发送的是数据还是命令。