先来看一个整体的图:

主要看图中蓝 {MOD}的箭头,它反映了IPU内部数据总线的连接关系。后面我们研究的DMA传输都需要物理连接的支撑。可以看出来,在IPU中最重要的模块就是这个CM- Control Module模块和IDMAC– Image DMA Control模块了。 这个图中有几点不好理解: (1)IPU和ARM都挂载在AHB总线上面,ARM就是通过CM模块来控制使用IPU。 (2)数据要进行DMA传输全部需要使用IDMAC进行控制,同时IDMAC通过AXI总线与内存相连。

IDMAC的作用: 下面来分析IDMAC:

下面来分析IDMAC:

看看各个子模块的含义: IBIW& IBIR : Internal Bus Interface Write / Read IPU内部总线向IDMAC桥接,可以简单看成多路复用控制模块。 FCW& FCR : Format Converter Write / Read 从框图反映为64位总线向128位总线过渡,其实它的核心工作是数据的压缩存放,和压缩数据进入IPU其他模块前的数据还原。但数据位于RAM中的存储方式与IPU所支持的格式不同。当然要想实现数据的压缩与恢复我们还需要CPMEM与LUT的支持。 BCW& BCR : Buffer Controller Write / Read BUFW& BUFR : Buffer Write / Read 读写端都具有4x 64 bytes buffers,因为RGBA与YUVA都有4种颜 {MOD}分量构成。BCW控制BUFW而BCR控制BUFR。 AXIW& AXIR : AXI Write / Read AXIW/AXIR控制对AXI总线的读写。IPU手册解释为:实时通道控制。因为IPU向AXI发出的请求有实时总线请求与非实时总线请求,并且BCR/BCW会对他们进行控制,可用读取通道数为8,写入通道数为6。因此防止全部非实时通道造成的通道阻塞,因此需要限制IPU同时最高使用的通道数目。 CC_W& CC_R : Channel Control Write / Read 其实CC_W/CC_R才是最重要的IDMAC控制单元 AAU_W& AAU_R : Address Arithmetic Unit Write / Read DMA访问地址计算单元 ATC: Alpha Transparency Controller LUT: Look up table CPMEM: Channel Parameter Memory 每个通道由160bit参数配置区控制。

下面具体分析每一个小模块: (1)IDMAC目前一共有52个channel,如果想要使能一个channel的话,就设置对应的IPU_IDMAC_CH_EN寄存器,由于每个寄存器是32位的,所以需要两个寄存器来对应这52个channel,寄存器如下所示:

(2)IBIW&

IBIR - Internal bus interface for write and read

这个小模块实现了IPU内部的子模块与IDMAC的通信,IPU内部的子模块通过IBIW来向内存中写数据,通过IBIR来从内存中读取数据。

(2)IBIW&

IBIR - Internal bus interface for write and read

这个小模块实现了IPU内部的子模块与IDMAC的通信,IPU内部的子模块通过IBIW来向内存中写数据,通过IBIR来从内存中读取数据。

(3)FCW& FCR - Format converter write and read Formatconverter的主要工作是数据的压缩存放(write的时候)与压缩数据的还原(read的时候)。为什么这么说呢:因为IPU内部只支持下面这两种格式,并且每种格式都是32位的。 而数据在RAM中的存储方式有很多,如下所示:

而数据在RAM中的存储方式有很多,如下所示:

图中R/G/B意味着这个位置可以为R或者G或者B。A代表alpha元素的位置。

这些格式元素保存在CPMEM中。

下面这个图是数据压缩的示意图:

图中R/G/B意味着这个位置可以为R或者G或者B。A代表alpha元素的位置。

这些格式元素保存在CPMEM中。

下面这个图是数据压缩的示意图:

下面这个图是数据解压示意图:

下面这个图是数据解压示意图:

如果要读取的数据是已经编码的格式,需要经过look_uptable来解码。所以LUT必须在IDMAC初始化的时候加载进去。LUT的输出格式必须匹配IPU内部的数据格式:RGB888,同时R在最高位,A在最低位。

(4)Bufferingunits Bufferingunits(BUFW,BUFR)用来存储包含不同颜 {MOD}成分的已编码数据。每一个bufferingunit包含4×64bytes。BUFW被BCW和AXIW控制,BUFR被BCR和AXIR控制。

(5)AXIW- AXI Write and AXIR - AXI Read AXIW/AXIR控制对AXI总线的读写。IPU手册解释为:实时通道控制。因为IPU向AXI发出的请求有实时总线请求与非实时总线请求,并且BCR/BCW会对他们进行控制,可用读取通道数为8,写入通道数为6.因此防止全部非实时通道造成的通道阻塞。因此需要限制IPU同时最高使用的通道数目。需要设置USED_BUFS_MAX_W或者USED_BUFS_MAX_R,但是没有找到这两个寄存器在哪里。

(6)CC_W& CC_R - Channel Control Write and Read 1.Channel Control unit是IDMAC里面最重要的控制单元。 1)它根据各个channel的优先级来仲裁。 2)控制addressarithmetic unit(AAU)。 3)作为CPMEM的接口,从CPMEM里面来读取参数,为参数所对应的控制做准备,然后如果这些参数更新了的话,再将这些参数写到CPMEM中去。 4)CC_R为IBIR单元提供参数。 5)CC_W为AXIW单元提供参数。

2.Channel Control单元几乎计算需要所有的参数,除了地址和BS(burst size)是在AAU中计算。 3.优先级设置: 1)每个channel优先级是在IDMAC_CH_PRI_1和IDMAC_CH_PRI_2寄存器中的对应位中设置的。 2)watermark(水印)从子模块中产生,同时watermark默认是忽视的,除非IDMAC_WM_EN寄存器中的某个channel对应位已经设置了。 3)alpha通道有特殊的优先级。 IDMAC_CH_PRI_1寄存器如下:

IDMAC_CH_PRI_2寄存器中肯定是剩下的channel了,就不截图表示了。 4.其中最终的优先级value是根据上面所说的三个优先级的综合结果,如下所示:

大致意思就是每个alphachannel的优先级权值是1,Channel'spriority bit的优先级权值是2,watermarksignal的优先级权值是1.再对比上图,就很好理解最终的优先级value是怎么计算出来的。

5.Locking the arbitration and reordering the AXI bursts 当通过AXI总线发送连续的burst地址的时候,能够提高系统的整体性能。这样做的方法是将同一个channel的AXIburst地址重新排序后一起发送。有关的寄存器是IPUx_IDMAC_LOCK_EN_1和IPUx_IDMAC_LOCK_EN_2.如下所示:

顺便看一下解释:用两位来表示一个channel,这两位的值代表同时发送这个channel的几个连续AXIburst地址。

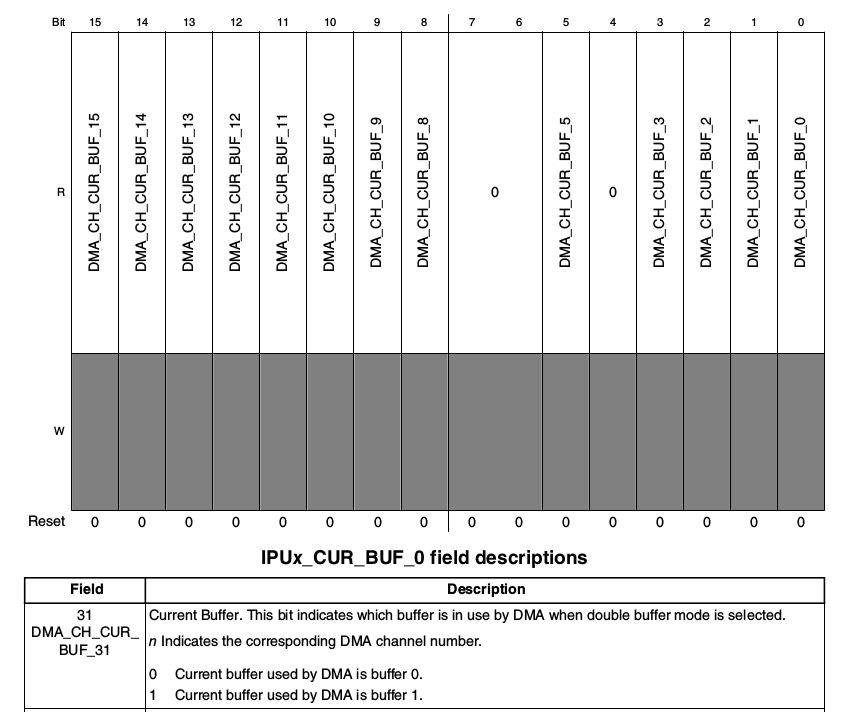

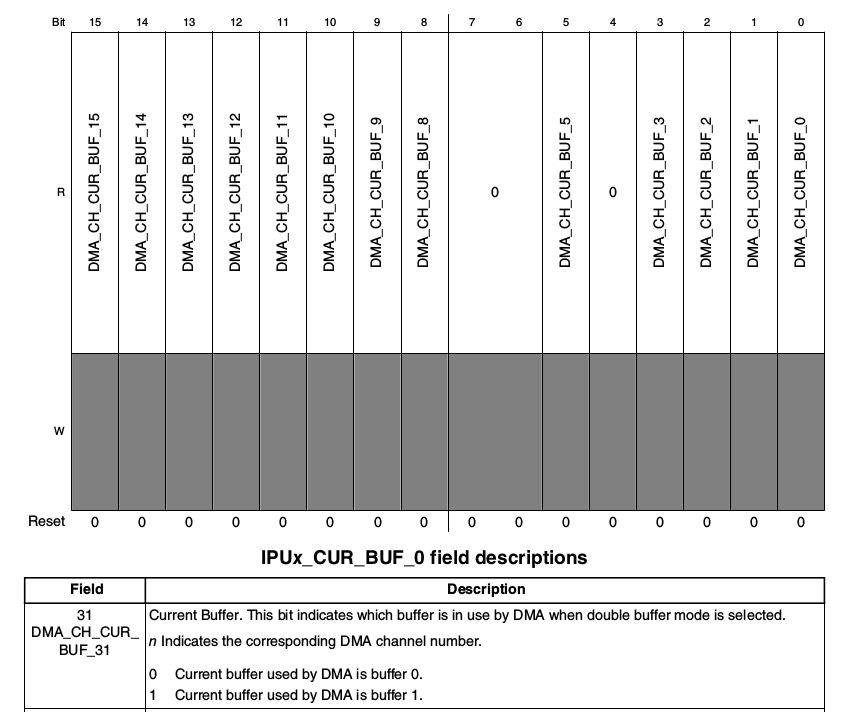

(7)AAU_W& AAU_R- Address Arithmetic Unit for Write and Read DMA访问地址计算单元,计算出IPU能够访问的地址,计算公式是: ADDR= EBA + (XB + SX) * BPP + (YB + SY) * (SL + 1) 当在使用双buffer模式时,EBA0是buffer0的基地址,EBA1是buffer1的基地址。IPU_CHA_CUR_BUF寄存器是一个状态寄存器,里面包含每一个DMAchannel当前使用的buffer的指针,如下所示:

当在使用双buffer模式时,EBA0是buffer0的基地址,EBA1是buffer1的基地址。IPU_CHA_CUR_BUF寄存器是一个状态寄存器,里面包含每一个DMAchannel当前使用的buffer的指针,如下所示:

可以看出来,这个寄存器是只读的。 IPU会自动地将IPU_CHA_CUR_BUF寄存器里面的指针指向当前的buffer。如果双buffer模式的数据来源是ARM平台的话,那么ARM就需要去检查这个寄存器来确定哪一个buffer是当前使用的,并且ARM只能在没有其他dmachannel使用buffer的情况下向其中写数据。当ARM平台将这个buffer中填充满数据以后,需要设置IPU_CHA_BUF0_RDY和IPU_CHA_BUF1_RDY这两个寄存器中的相应位。 因为一共52个dmachannel,所以需要使用4个寄存器来表示这些状态,下面只列出了IPUx_CH_BUF1_RDY0寄存器。 在上面介绍ChannelControl的时候说了,CC是最重要的控制单元,它有几个功能:

作为CPMEM的接口,从CPMEM里面来读取参数,为参数所对应的控制做准备,然后如果这些参数更新了的话,再将这些参数写到CPMEM中去,控制addressarithmetic

unit(AAU)来计算地址。而这个AAU就是通过上述过程来计算地址的。

在上面介绍ChannelControl的时候说了,CC是最重要的控制单元,它有几个功能:

作为CPMEM的接口,从CPMEM里面来读取参数,为参数所对应的控制做准备,然后如果这些参数更新了的话,再将这些参数写到CPMEM中去,控制addressarithmetic

unit(AAU)来计算地址。而这个AAU就是通过上述过程来计算地址的。

(8)ATC- Alpha Transparency Controller 当像素数据和alpha数据分布在不同的buffer的时候,就需要ATC来控制。 首先需要明确的一点是,在52个dmachannel中,一共有7个dmachannel是可以指定像素数据和alpha数据分布在不同的buffer中。这几个dmachannel分别是:14,15,23,24,25,27,29.当然,这几个channel也可以像其他channel

主要看图中蓝 {MOD}的箭头,它反映了IPU内部数据总线的连接关系。后面我们研究的DMA传输都需要物理连接的支撑。可以看出来,在IPU中最重要的模块就是这个CM- Control Module模块和IDMAC– Image DMA Control模块了。 这个图中有几点不好理解: (1)IPU和ARM都挂载在AHB总线上面,ARM就是通过CM模块来控制使用IPU。 (2)数据要进行DMA传输全部需要使用IDMAC进行控制,同时IDMAC通过AXI总线与内存相连。

IDMAC的作用:

下面来分析IDMAC:

下面来分析IDMAC:

看看各个子模块的含义: IBIW& IBIR : Internal Bus Interface Write / Read IPU内部总线向IDMAC桥接,可以简单看成多路复用控制模块。 FCW& FCR : Format Converter Write / Read 从框图反映为64位总线向128位总线过渡,其实它的核心工作是数据的压缩存放,和压缩数据进入IPU其他模块前的数据还原。但数据位于RAM中的存储方式与IPU所支持的格式不同。当然要想实现数据的压缩与恢复我们还需要CPMEM与LUT的支持。 BCW& BCR : Buffer Controller Write / Read BUFW& BUFR : Buffer Write / Read 读写端都具有4x 64 bytes buffers,因为RGBA与YUVA都有4种颜 {MOD}分量构成。BCW控制BUFW而BCR控制BUFR。 AXIW& AXIR : AXI Write / Read AXIW/AXIR控制对AXI总线的读写。IPU手册解释为:实时通道控制。因为IPU向AXI发出的请求有实时总线请求与非实时总线请求,并且BCR/BCW会对他们进行控制,可用读取通道数为8,写入通道数为6。因此防止全部非实时通道造成的通道阻塞,因此需要限制IPU同时最高使用的通道数目。 CC_W& CC_R : Channel Control Write / Read 其实CC_W/CC_R才是最重要的IDMAC控制单元 AAU_W& AAU_R : Address Arithmetic Unit Write / Read DMA访问地址计算单元 ATC: Alpha Transparency Controller LUT: Look up table CPMEM: Channel Parameter Memory 每个通道由160bit参数配置区控制。

下面具体分析每一个小模块: (1)IDMAC目前一共有52个channel,如果想要使能一个channel的话,就设置对应的IPU_IDMAC_CH_EN寄存器,由于每个寄存器是32位的,所以需要两个寄存器来对应这52个channel,寄存器如下所示:

(2)IBIW&

IBIR - Internal bus interface for write and read

这个小模块实现了IPU内部的子模块与IDMAC的通信,IPU内部的子模块通过IBIW来向内存中写数据,通过IBIR来从内存中读取数据。

(2)IBIW&

IBIR - Internal bus interface for write and read

这个小模块实现了IPU内部的子模块与IDMAC的通信,IPU内部的子模块通过IBIW来向内存中写数据,通过IBIR来从内存中读取数据。

(3)FCW& FCR - Format converter write and read Formatconverter的主要工作是数据的压缩存放(write的时候)与压缩数据的还原(read的时候)。为什么这么说呢:因为IPU内部只支持下面这两种格式,并且每种格式都是32位的。

而数据在RAM中的存储方式有很多,如下所示:

而数据在RAM中的存储方式有很多,如下所示:

图中R/G/B意味着这个位置可以为R或者G或者B。A代表alpha元素的位置。

这些格式元素保存在CPMEM中。

下面这个图是数据压缩的示意图:

图中R/G/B意味着这个位置可以为R或者G或者B。A代表alpha元素的位置。

这些格式元素保存在CPMEM中。

下面这个图是数据压缩的示意图:

下面这个图是数据解压示意图:

下面这个图是数据解压示意图:

如果要读取的数据是已经编码的格式,需要经过look_uptable来解码。所以LUT必须在IDMAC初始化的时候加载进去。LUT的输出格式必须匹配IPU内部的数据格式:RGB888,同时R在最高位,A在最低位。

(4)Bufferingunits Bufferingunits(BUFW,BUFR)用来存储包含不同颜 {MOD}成分的已编码数据。每一个bufferingunit包含4×64bytes。BUFW被BCW和AXIW控制,BUFR被BCR和AXIR控制。

(5)AXIW- AXI Write and AXIR - AXI Read AXIW/AXIR控制对AXI总线的读写。IPU手册解释为:实时通道控制。因为IPU向AXI发出的请求有实时总线请求与非实时总线请求,并且BCR/BCW会对他们进行控制,可用读取通道数为8,写入通道数为6.因此防止全部非实时通道造成的通道阻塞。因此需要限制IPU同时最高使用的通道数目。需要设置USED_BUFS_MAX_W或者USED_BUFS_MAX_R,但是没有找到这两个寄存器在哪里。

(6)CC_W& CC_R - Channel Control Write and Read 1.Channel Control unit是IDMAC里面最重要的控制单元。 1)它根据各个channel的优先级来仲裁。 2)控制addressarithmetic unit(AAU)。 3)作为CPMEM的接口,从CPMEM里面来读取参数,为参数所对应的控制做准备,然后如果这些参数更新了的话,再将这些参数写到CPMEM中去。 4)CC_R为IBIR单元提供参数。 5)CC_W为AXIW单元提供参数。

2.Channel Control单元几乎计算需要所有的参数,除了地址和BS(burst size)是在AAU中计算。 3.优先级设置: 1)每个channel优先级是在IDMAC_CH_PRI_1和IDMAC_CH_PRI_2寄存器中的对应位中设置的。 2)watermark(水印)从子模块中产生,同时watermark默认是忽视的,除非IDMAC_WM_EN寄存器中的某个channel对应位已经设置了。 3)alpha通道有特殊的优先级。 IDMAC_CH_PRI_1寄存器如下:

IDMAC_CH_PRI_2寄存器中肯定是剩下的channel了,就不截图表示了。 4.其中最终的优先级value是根据上面所说的三个优先级的综合结果,如下所示:

大致意思就是每个alphachannel的优先级权值是1,Channel'spriority bit的优先级权值是2,watermarksignal的优先级权值是1.再对比上图,就很好理解最终的优先级value是怎么计算出来的。

5.Locking the arbitration and reordering the AXI bursts 当通过AXI总线发送连续的burst地址的时候,能够提高系统的整体性能。这样做的方法是将同一个channel的AXIburst地址重新排序后一起发送。有关的寄存器是IPUx_IDMAC_LOCK_EN_1和IPUx_IDMAC_LOCK_EN_2.如下所示:

顺便看一下解释:用两位来表示一个channel,这两位的值代表同时发送这个channel的几个连续AXIburst地址。

(7)AAU_W& AAU_R- Address Arithmetic Unit for Write and Read DMA访问地址计算单元,计算出IPU能够访问的地址,计算公式是: ADDR= EBA + (XB + SX) * BPP + (YB + SY) * (SL + 1)

当在使用双buffer模式时,EBA0是buffer0的基地址,EBA1是buffer1的基地址。IPU_CHA_CUR_BUF寄存器是一个状态寄存器,里面包含每一个DMAchannel当前使用的buffer的指针,如下所示:

当在使用双buffer模式时,EBA0是buffer0的基地址,EBA1是buffer1的基地址。IPU_CHA_CUR_BUF寄存器是一个状态寄存器,里面包含每一个DMAchannel当前使用的buffer的指针,如下所示:

可以看出来,这个寄存器是只读的。 IPU会自动地将IPU_CHA_CUR_BUF寄存器里面的指针指向当前的buffer。如果双buffer模式的数据来源是ARM平台的话,那么ARM就需要去检查这个寄存器来确定哪一个buffer是当前使用的,并且ARM只能在没有其他dmachannel使用buffer的情况下向其中写数据。当ARM平台将这个buffer中填充满数据以后,需要设置IPU_CHA_BUF0_RDY和IPU_CHA_BUF1_RDY这两个寄存器中的相应位。 因为一共52个dmachannel,所以需要使用4个寄存器来表示这些状态,下面只列出了IPUx_CH_BUF1_RDY0寄存器。

在上面介绍ChannelControl的时候说了,CC是最重要的控制单元,它有几个功能:

作为CPMEM的接口,从CPMEM里面来读取参数,为参数所对应的控制做准备,然后如果这些参数更新了的话,再将这些参数写到CPMEM中去,控制addressarithmetic

unit(AAU)来计算地址。而这个AAU就是通过上述过程来计算地址的。

在上面介绍ChannelControl的时候说了,CC是最重要的控制单元,它有几个功能:

作为CPMEM的接口,从CPMEM里面来读取参数,为参数所对应的控制做准备,然后如果这些参数更新了的话,再将这些参数写到CPMEM中去,控制addressarithmetic

unit(AAU)来计算地址。而这个AAU就是通过上述过程来计算地址的。

(8)ATC- Alpha Transparency Controller 当像素数据和alpha数据分布在不同的buffer的时候,就需要ATC来控制。 首先需要明确的一点是,在52个dmachannel中,一共有7个dmachannel是可以指定像素数据和alpha数据分布在不同的buffer中。这几个dmachannel分别是:14,15,23,24,25,27,29.当然,这几个channel也可以像其他channel