u-boot分析 四 (程序入口start.S)

注:部分内容摘抄自网络,如有问题,请联络博主。

本文内容:了解以stars.S为开始的ARM汇编程序部分。

回顾前几篇博文,咱们见识过了u-boot的目录结构,另外简要分析了u-boot.lds脚本文件的link原理。而今天我们要来听听嵌入式程序君告诉咱们的第一句“话”。

正式开始之前,我们需要准备三样东西:

- u-boot source code

- 常用ARM指令集

- Source Insight(用于trace code,使用方法略过,不会问百度)

bootloader通常stage1和stage2两步骤,u-boot也不例外。

- Stage1:依赖于CPU体系结构的代码(如设备初始化代码等)通常都放在这个程序段,且可以用汇编语言来实现;

- stage2:通常用C语言来实现,这样可以实现复杂的功能,而且有更好的可读性和移植性。

- Stage1 start.S代码结构

u-boot的stage1代码通常放在start.S文件中,用汇编语言写成,其主要代码部分如下:

(1) 定义入口。由于一个可执行文件必须有一个入口点,并且只能有一个全局入口,通常这个入口放在ROM(Flash)的0x0地址。因此,必须通知编译器以使其知道这个入口,该工作可通过修改链接器脚本(.lds文件)来完成。

(2) 设置异常向量(Exception Vector)。

(3) 设置CPU的速度、时钟频率及终端控制寄存器。

(4) 初始化内存控制器。

(5) 将ROM中的代码复制到RAM中。

(6) 初始化堆栈。

(7) 转到RAM中执行,该工作可使用指令ldr pc来完成。 - Stage2 C语言代码部分

./arch/arm/lib/board.c中的board_init_r()是C语言开始的函数,也是整个启动代码中C语言的主函数,同时还是整个u-boot(armboot)的主函数,该函数主要完成如下操作:

(1) 调用一系列的初始化函数。

(2) 初始化Flash设备。

(3) 初始化系统内存分配函数。

(4) 如果目标系统拥有NAND设备,则初始化NAND设备。

(5) 如果目标系统有显示设备,则初始化该类设备。

(6) 初始化相关网络设备,填写IP、MAC地址等。

(7) 进去命令循环(即整个boot的工作循环),接收用户从串口输入的命令,然后进行相应的工作。

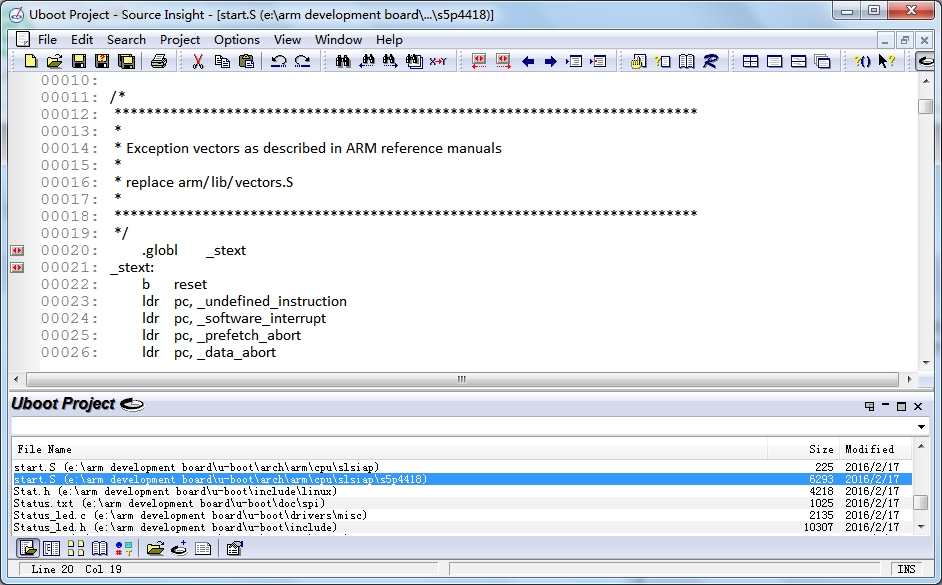

./arch/arm/cpu/slsiap/s5p4418/start.S

/*

* armboot - Startup Code for NXPxxxx/ARM Cortex CPU-core

*/

#include

回顾全文,我们总结一下start.S都干了些什么?

- 首先定义程序入口_stext

- 然后定义了异常向量表

- 一堆初始化,e.g. PLL, MUX, Memory等

- Copy代码从ROM到RAM

- MMU on

- 最后跳转到C入口

参考博客:

http://blog.chinaunix.net/uid-22891435-id-380150.html

完