本文中是看过一些文章后所写,而且可能很多内容都是来自这几篇文章,下面我将我所参考的文章放在下面:

网卡 搭建新通道 DM9000芯片 ARP协议实现

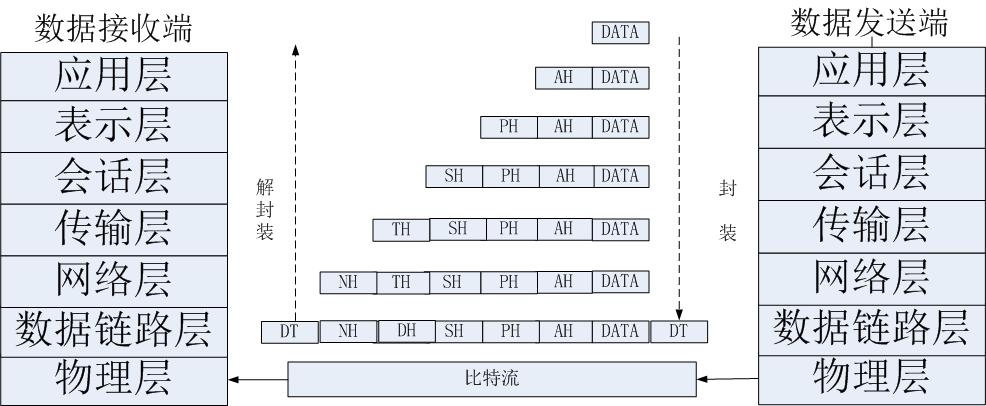

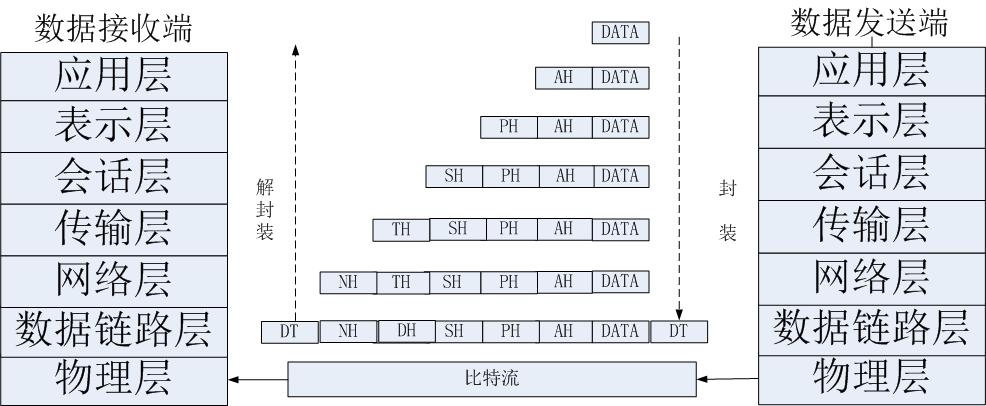

OSI(Open System Interconnection)即开放式系统互联参考模型 。它把网络协议从逻辑上分为了7层。通过七个层次使不同的系统网络之间实现可靠的通讯。

但是OSI参考模型的过于庞大、复杂招致了许多批评。与此对照,由技术人员自己开发的TCP/IP协议栈获得了更为广泛的应用。

OSI(Open System Interconnection)即开放式系统互联参考模型 。它把网络协议从逻辑上分为了7层。通过七个层次使不同的系统网络之间实现可靠的通讯。

但是OSI参考模型的过于庞大、复杂招致了许多批评。与此对照,由技术人员自己开发的TCP/IP协议栈获得了更为广泛的应用。

上图中前面两列就是OSI与TCP/IP的分层对应关系,而后面的一列是其传输对象形式。

而我们今天说的网卡主要工作在数据链路层和物理层,对应到TCP/IP为网络接口层。而他的主要框架为:

上图中前面两列就是OSI与TCP/IP的分层对应关系,而后面的一列是其传输对象形式。

而我们今天说的网卡主要工作在数据链路层和物理层,对应到TCP/IP为网络接口层。而他的主要框架为:

而图中我们用绿 {MOD}方框圈起来的部分为物理层PHY,而用蓝 {MOD}方框圈起来的部分为数据链路层MAC。现在可能有同学要问了:那么MAC和PHY又是什么那?

下面我们一一解释:

MAC是Media Access Control 的缩写,即媒体访问控制子层协议。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。以太网MAC由IEEE-802.3以太网标准定义。

PHY是物理接口收发器,它实现物理层。包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。IEEE-802.3标准定义了以太网PHY。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

而我们知道网卡工作在osi的最后两层,物理层和数据链路层,物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。以太网卡中数据链路层的芯片称之为MAC控制器。很多网卡的这两个部分是做到一起的。他们之间的关系是pci总线接mac总线,mac接 phy,phy接网线(当然也不是直接接上的,还有一个变压装置)。

上面介绍了MAC和PHY,那么他们的关系是什么那?我们用一句简单的话总结就是:

ETHERNET的接口实质是MAC通过MII总线控制PHY的过程。

而图中我们用绿 {MOD}方框圈起来的部分为物理层PHY,而用蓝 {MOD}方框圈起来的部分为数据链路层MAC。现在可能有同学要问了:那么MAC和PHY又是什么那?

下面我们一一解释:

MAC是Media Access Control 的缩写,即媒体访问控制子层协议。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。以太网MAC由IEEE-802.3以太网标准定义。

PHY是物理接口收发器,它实现物理层。包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。IEEE-802.3标准定义了以太网PHY。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

而我们知道网卡工作在osi的最后两层,物理层和数据链路层,物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。以太网卡中数据链路层的芯片称之为MAC控制器。很多网卡的这两个部分是做到一起的。他们之间的关系是pci总线接mac总线,mac接 phy,phy接网线(当然也不是直接接上的,还有一个变压装置)。

上面介绍了MAC和PHY,那么他们的关系是什么那?我们用一句简单的话总结就是:

ETHERNET的接口实质是MAC通过MII总线控制PHY的过程。

而下面用自己画的一幅图来对他们的关系进行说明(可能有错,但是重在理解):

而下面用自己画的一幅图来对他们的关系进行说明(可能有错,但是重在理解):

而上图就是他们的一些关系,下面我们详细说明:

我们知道MAC和PHY是通过MII总线连接的。那么MII总线又是什么那?

MII(Media Independent Interface)即媒体独立接口, “媒体独立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号,包括TX_ER,TXD<3:0>,TX_EN,TX_CLK,COL,RXD<3:0>,RX_EX,RX_CLK,CRS,RX_DV等。

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。MII管理接口是个双信号接口,一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。其管理是使用SMI(Serial Management Interface)总线通过读写PHY的寄存器来完成的。PHY里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,例如连接速度,双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是有IEEE的规范的,因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

通过上面的介绍,我想大家对网卡的数据传输层次有了基本的了解,下面我们介绍DM9000C的传输原理:

DM9000 是Davicom公司的一款以太网控制芯片,在网络中它可自动获得同设定MAC地址一致的IP包,完成IP包的收发,再用一个单片机来结合完成上层协议,就构成了一个完整的网络终端。在单片机中嵌入了一个精简TCP/IP协议栈。

API 总共分7部分,包括网络接口层、动态内存管理模块、缓冲区管理模块、UDP层、TCP层、DHCP模块和DNS模块。

协议栈本身需求ROM空间为21KWord。

(1)内存工作原理DM9000 共有16 K Byte(0000h-3FFFh)内存,而读写内存由MWCMD、MRCMD这两个寄存器来控制。MWRL,MWRH 寄存器提供现在写入内存的位置,MRRL,MRRH 寄存器提供现在读取内存的位置。内存移动工作模式为每次移动1 个Byte(8 bit)或2个Byte(16 bit)。

(2)封包传送工作原理内存中默认值有3 KByte (0000h-0BFFh)提供给传送功能使用。而传送一个封包流程如下:

①将要传送封包的长度,填入到TXPLL,TXPLH寄存器;

② 将要传送封包的资料由MWCMD 寄存器填入内存中;

③由TCR寄存器使DM9000 送出封包资料;

④若内存的写入位置超过0BFFh 时,自动将下一个位置回复到0000h。

(3)封包接收工作原理内存中默认值有13K Byte( 0C00h-03FFFh)提供给接收功能使用。在每一个封包,会有4个Byte存放一些封包相关资料。第1 个Byte 是封包是否已存放在接收内存,若值为“01h”为封包已存放于接收内存,若为“00h”则接收内存尚未有封包存放。在读取其它Byte之前,必需要确定第1 个byte 是否为“01h”。第2 个Byte 则为这个封包的一些相关讯息,它的格式像RSR寄存器的格式。第3和4个Byte是存放这个封包的长度大小。接一个封包的流程如下:

①检查MRCMDX寄存器值是否为01,若是则有封包进入需读取;

②读取MRCMD,将前4 个Byte封包讯息读入;

③由前4 个Byte封包讯息取到待得封包长度(以Byte 为单位),连续读取MRCMD,将封包资料移到系统内存之中;

④若读取位置超过3FFFh 时,自动会移到0C00h。

而上图就是他们的一些关系,下面我们详细说明:

我们知道MAC和PHY是通过MII总线连接的。那么MII总线又是什么那?

MII(Media Independent Interface)即媒体独立接口, “媒体独立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号,包括TX_ER,TXD<3:0>,TX_EN,TX_CLK,COL,RXD<3:0>,RX_EX,RX_CLK,CRS,RX_DV等。

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。MII管理接口是个双信号接口,一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。其管理是使用SMI(Serial Management Interface)总线通过读写PHY的寄存器来完成的。PHY里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,例如连接速度,双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是有IEEE的规范的,因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

通过上面的介绍,我想大家对网卡的数据传输层次有了基本的了解,下面我们介绍DM9000C的传输原理:

DM9000 是Davicom公司的一款以太网控制芯片,在网络中它可自动获得同设定MAC地址一致的IP包,完成IP包的收发,再用一个单片机来结合完成上层协议,就构成了一个完整的网络终端。在单片机中嵌入了一个精简TCP/IP协议栈。

API 总共分7部分,包括网络接口层、动态内存管理模块、缓冲区管理模块、UDP层、TCP层、DHCP模块和DNS模块。

协议栈本身需求ROM空间为21KWord。

(1)内存工作原理DM9000 共有16 K Byte(0000h-3FFFh)内存,而读写内存由MWCMD、MRCMD这两个寄存器来控制。MWRL,MWRH 寄存器提供现在写入内存的位置,MRRL,MRRH 寄存器提供现在读取内存的位置。内存移动工作模式为每次移动1 个Byte(8 bit)或2个Byte(16 bit)。

(2)封包传送工作原理内存中默认值有3 KByte (0000h-0BFFh)提供给传送功能使用。而传送一个封包流程如下:

①将要传送封包的长度,填入到TXPLL,TXPLH寄存器;

② 将要传送封包的资料由MWCMD 寄存器填入内存中;

③由TCR寄存器使DM9000 送出封包资料;

④若内存的写入位置超过0BFFh 时,自动将下一个位置回复到0000h。

(3)封包接收工作原理内存中默认值有13K Byte( 0C00h-03FFFh)提供给接收功能使用。在每一个封包,会有4个Byte存放一些封包相关资料。第1 个Byte 是封包是否已存放在接收内存,若值为“01h”为封包已存放于接收内存,若为“00h”则接收内存尚未有封包存放。在读取其它Byte之前,必需要确定第1 个byte 是否为“01h”。第2 个Byte 则为这个封包的一些相关讯息,它的格式像RSR寄存器的格式。第3和4个Byte是存放这个封包的长度大小。接一个封包的流程如下:

①检查MRCMDX寄存器值是否为01,若是则有封包进入需读取;

②读取MRCMD,将前4 个Byte封包讯息读入;

③由前4 个Byte封包讯息取到待得封包长度(以Byte 为单位),连续读取MRCMD,将封包资料移到系统内存之中;

④若读取位置超过3FFFh 时,自动会移到0C00h。

DM9000网卡芯片驱动的预备知识:MAC/PHY - lagignition的日志

而本篇文章主要是对上述文章内容的一个综合。如有不对,感谢指出。 下面我们开始介绍网卡的工作原理,而要介绍网卡的工作原理就离不开介绍网络模型的分层,下面我们先引进最早的分层OSI七层网络模型 OSI(Open System Interconnection)即开放式系统互联参考模型 。它把网络协议从逻辑上分为了7层。通过七个层次使不同的系统网络之间实现可靠的通讯。

但是OSI参考模型的过于庞大、复杂招致了许多批评。与此对照,由技术人员自己开发的TCP/IP协议栈获得了更为广泛的应用。

OSI(Open System Interconnection)即开放式系统互联参考模型 。它把网络协议从逻辑上分为了7层。通过七个层次使不同的系统网络之间实现可靠的通讯。

但是OSI参考模型的过于庞大、复杂招致了许多批评。与此对照,由技术人员自己开发的TCP/IP协议栈获得了更为广泛的应用。

上图中前面两列就是OSI与TCP/IP的分层对应关系,而后面的一列是其传输对象形式。

而我们今天说的网卡主要工作在数据链路层和物理层,对应到TCP/IP为网络接口层。而他的主要框架为:

上图中前面两列就是OSI与TCP/IP的分层对应关系,而后面的一列是其传输对象形式。

而我们今天说的网卡主要工作在数据链路层和物理层,对应到TCP/IP为网络接口层。而他的主要框架为:

而图中我们用绿 {MOD}方框圈起来的部分为物理层PHY,而用蓝 {MOD}方框圈起来的部分为数据链路层MAC。现在可能有同学要问了:那么MAC和PHY又是什么那?

下面我们一一解释:

MAC是Media Access Control 的缩写,即媒体访问控制子层协议。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。以太网MAC由IEEE-802.3以太网标准定义。

PHY是物理接口收发器,它实现物理层。包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。IEEE-802.3标准定义了以太网PHY。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

而我们知道网卡工作在osi的最后两层,物理层和数据链路层,物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。以太网卡中数据链路层的芯片称之为MAC控制器。很多网卡的这两个部分是做到一起的。他们之间的关系是pci总线接mac总线,mac接 phy,phy接网线(当然也不是直接接上的,还有一个变压装置)。

上面介绍了MAC和PHY,那么他们的关系是什么那?我们用一句简单的话总结就是:

ETHERNET的接口实质是MAC通过MII总线控制PHY的过程。

而图中我们用绿 {MOD}方框圈起来的部分为物理层PHY,而用蓝 {MOD}方框圈起来的部分为数据链路层MAC。现在可能有同学要问了:那么MAC和PHY又是什么那?

下面我们一一解释:

MAC是Media Access Control 的缩写,即媒体访问控制子层协议。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。以太网MAC由IEEE-802.3以太网标准定义。

PHY是物理接口收发器,它实现物理层。包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。IEEE-802.3标准定义了以太网PHY。它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范。PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突。

而我们知道网卡工作在osi的最后两层,物理层和数据链路层,物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。以太网卡中数据链路层的芯片称之为MAC控制器。很多网卡的这两个部分是做到一起的。他们之间的关系是pci总线接mac总线,mac接 phy,phy接网线(当然也不是直接接上的,还有一个变压装置)。

上面介绍了MAC和PHY,那么他们的关系是什么那?我们用一句简单的话总结就是:

ETHERNET的接口实质是MAC通过MII总线控制PHY的过程。

而下面用自己画的一幅图来对他们的关系进行说明(可能有错,但是重在理解):

而下面用自己画的一幅图来对他们的关系进行说明(可能有错,但是重在理解):

而上图就是他们的一些关系,下面我们详细说明:

我们知道MAC和PHY是通过MII总线连接的。那么MII总线又是什么那?

MII(Media Independent Interface)即媒体独立接口, “媒体独立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号,包括TX_ER,TXD<3:0>,TX_EN,TX_CLK,COL,RXD<3:0>,RX_EX,RX_CLK,CRS,RX_DV等。

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。MII管理接口是个双信号接口,一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。其管理是使用SMI(Serial Management Interface)总线通过读写PHY的寄存器来完成的。PHY里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,例如连接速度,双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是有IEEE的规范的,因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

通过上面的介绍,我想大家对网卡的数据传输层次有了基本的了解,下面我们介绍DM9000C的传输原理:

DM9000 是Davicom公司的一款以太网控制芯片,在网络中它可自动获得同设定MAC地址一致的IP包,完成IP包的收发,再用一个单片机来结合完成上层协议,就构成了一个完整的网络终端。在单片机中嵌入了一个精简TCP/IP协议栈。

API 总共分7部分,包括网络接口层、动态内存管理模块、缓冲区管理模块、UDP层、TCP层、DHCP模块和DNS模块。

协议栈本身需求ROM空间为21KWord。

(1)内存工作原理DM9000 共有16 K Byte(0000h-3FFFh)内存,而读写内存由MWCMD、MRCMD这两个寄存器来控制。MWRL,MWRH 寄存器提供现在写入内存的位置,MRRL,MRRH 寄存器提供现在读取内存的位置。内存移动工作模式为每次移动1 个Byte(8 bit)或2个Byte(16 bit)。

(2)封包传送工作原理内存中默认值有3 KByte (0000h-0BFFh)提供给传送功能使用。而传送一个封包流程如下:

①将要传送封包的长度,填入到TXPLL,TXPLH寄存器;

② 将要传送封包的资料由MWCMD 寄存器填入内存中;

③由TCR寄存器使DM9000 送出封包资料;

④若内存的写入位置超过0BFFh 时,自动将下一个位置回复到0000h。

(3)封包接收工作原理内存中默认值有13K Byte( 0C00h-03FFFh)提供给接收功能使用。在每一个封包,会有4个Byte存放一些封包相关资料。第1 个Byte 是封包是否已存放在接收内存,若值为“01h”为封包已存放于接收内存,若为“00h”则接收内存尚未有封包存放。在读取其它Byte之前,必需要确定第1 个byte 是否为“01h”。第2 个Byte 则为这个封包的一些相关讯息,它的格式像RSR寄存器的格式。第3和4个Byte是存放这个封包的长度大小。接一个封包的流程如下:

①检查MRCMDX寄存器值是否为01,若是则有封包进入需读取;

②读取MRCMD,将前4 个Byte封包讯息读入;

③由前4 个Byte封包讯息取到待得封包长度(以Byte 为单位),连续读取MRCMD,将封包资料移到系统内存之中;

④若读取位置超过3FFFh 时,自动会移到0C00h。

而上图就是他们的一些关系,下面我们详细说明:

我们知道MAC和PHY是通过MII总线连接的。那么MII总线又是什么那?

MII(Media Independent Interface)即媒体独立接口, “媒体独立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号,包括TX_ER,TXD<3:0>,TX_EN,TX_CLK,COL,RXD<3:0>,RX_EX,RX_CLK,CRS,RX_DV等。

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。MII管理接口是个双信号接口,一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。其管理是使用SMI(Serial Management Interface)总线通过读写PHY的寄存器来完成的。PHY里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,例如连接速度,双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是有IEEE的规范的,因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改。

通过上面的介绍,我想大家对网卡的数据传输层次有了基本的了解,下面我们介绍DM9000C的传输原理:

DM9000 是Davicom公司的一款以太网控制芯片,在网络中它可自动获得同设定MAC地址一致的IP包,完成IP包的收发,再用一个单片机来结合完成上层协议,就构成了一个完整的网络终端。在单片机中嵌入了一个精简TCP/IP协议栈。

API 总共分7部分,包括网络接口层、动态内存管理模块、缓冲区管理模块、UDP层、TCP层、DHCP模块和DNS模块。

协议栈本身需求ROM空间为21KWord。

(1)内存工作原理DM9000 共有16 K Byte(0000h-3FFFh)内存,而读写内存由MWCMD、MRCMD这两个寄存器来控制。MWRL,MWRH 寄存器提供现在写入内存的位置,MRRL,MRRH 寄存器提供现在读取内存的位置。内存移动工作模式为每次移动1 个Byte(8 bit)或2个Byte(16 bit)。

(2)封包传送工作原理内存中默认值有3 KByte (0000h-0BFFh)提供给传送功能使用。而传送一个封包流程如下:

①将要传送封包的长度,填入到TXPLL,TXPLH寄存器;

② 将要传送封包的资料由MWCMD 寄存器填入内存中;

③由TCR寄存器使DM9000 送出封包资料;

④若内存的写入位置超过0BFFh 时,自动将下一个位置回复到0000h。

(3)封包接收工作原理内存中默认值有13K Byte( 0C00h-03FFFh)提供给接收功能使用。在每一个封包,会有4个Byte存放一些封包相关资料。第1 个Byte 是封包是否已存放在接收内存,若值为“01h”为封包已存放于接收内存,若为“00h”则接收内存尚未有封包存放。在读取其它Byte之前,必需要确定第1 个byte 是否为“01h”。第2 个Byte 则为这个封包的一些相关讯息,它的格式像RSR寄存器的格式。第3和4个Byte是存放这个封包的长度大小。接一个封包的流程如下:

①检查MRCMDX寄存器值是否为01,若是则有封包进入需读取;

②读取MRCMD,将前4 个Byte封包讯息读入;

③由前4 个Byte封包讯息取到待得封包长度(以Byte 为单位),连续读取MRCMD,将封包资料移到系统内存之中;

④若读取位置超过3FFFh 时,自动会移到0C00h。