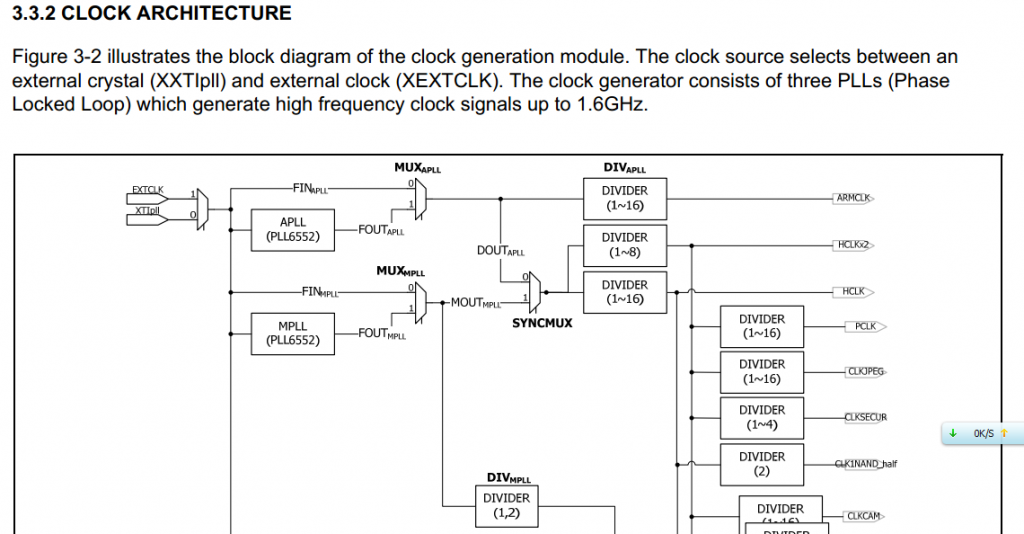

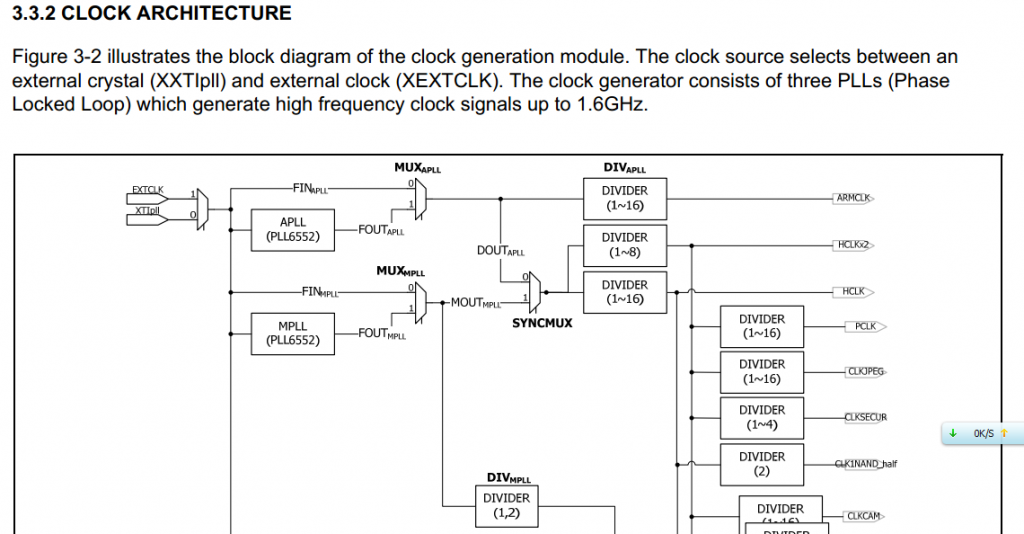

下面这张图,就是6410的系统时钟原理图:

的

6410的时钟频率决定公式:FOUT

= MDIV * FIN / (PDIV * 2^SDIV) 其中这几个值(MDIV,PDIV,SDIV)都在APLL_CON和MPLL_CON中。 FIN就是我们系统输入时钟,ok6410是12Mhz。

要得到最后的输出时钟都要设置 DIV分频器

的

6410的时钟频率决定公式:FOUT

= MDIV * FIN / (PDIV * 2^SDIV) 其中这几个值(MDIV,PDIV,SDIV)都在APLL_CON和MPLL_CON中。 FIN就是我们系统输入时钟,ok6410是12Mhz。

要得到最后的输出时钟都要设置 DIV分频器

ARMCLK = DOUTAPLL / (ARM_RADIO + 1) CLK_DIV0 mainly controls the system clocks and special clocks of multimedia IP s. The output frequencies of

APLL and MPLL are divided by ARM_RATIO and MPLL_RATIO. HCLKX2 clock is the base clock of other

operating system clocks and divided by HCLKX2_RATIO. There is operating frequency limitation. The maximum

operating frequency of HCLKX2, HCLK, and PCLK are 266MHz, 133MHz, and 66MHz, respectively. NAND,

SECUR, JPEG operating clock cannot exceed 66MHz. MFC and CAM operating clock cannot exceed 133MHz.

This operating clock condition must be met through CLK_DIV0 configuration.

这是手册上的一段话,也就是HCLK*2的频率不能超过266Mhz。jpeg,cam频率都有限制。 APLL给ARM CPU使用

MPLL给主设备、HCLK(内存,DDR),PCLK(外设片上模块)

EPLL给其它模块

异步模式: OTHERS寄存器设置为异步模式

读入OTHERS内存的值,并bic清0xc0

当arm时钟和Hclk不一样的时候使,要设置成异步 循环判断,等待设置完成

分频设置:要使我们的时钟正常工作,还要设置相应的分频参数,具体如下: 分频参数主要在CLK_DIV0里面设置。 设置CLK_DVIO

设置ARM_RATIO 0 主核分频为1分频

设置HCLCKX2_RATIO 1 将输入的时钟进行2分频

设置HCLK_RATIO 1 再将输入的时钟2分频,能供内存使用

设置PCLK_RATIO 3 其他RATIO的设置

设置流程:

在汇编启动代码中,在跳转到main函数之前,加上一下一句,即可设置时钟

bl clock_init

main函数,我就按照韦东山老师的视频教学上说的,写流水灯代码,可以看到如果延时不够,则流水灯跑得非常快。

的

6410的时钟频率决定公式:FOUT

= MDIV * FIN / (PDIV * 2^SDIV) 其中这几个值(MDIV,PDIV,SDIV)都在APLL_CON和MPLL_CON中。 FIN就是我们系统输入时钟,ok6410是12Mhz。

要得到最后的输出时钟都要设置 DIV分频器

的

6410的时钟频率决定公式:FOUT

= MDIV * FIN / (PDIV * 2^SDIV) 其中这几个值(MDIV,PDIV,SDIV)都在APLL_CON和MPLL_CON中。 FIN就是我们系统输入时钟,ok6410是12Mhz。

要得到最后的输出时钟都要设置 DIV分频器ARMCLK = DOUTAPLL / (ARM_RADIO + 1) CLK_DIV0 mainly controls the system clocks and special clocks of multimedia IP s. The output frequencies of

APLL and MPLL are divided by ARM_RATIO and MPLL_RATIO. HCLKX2 clock is the base clock of other

operating system clocks and divided by HCLKX2_RATIO. There is operating frequency limitation. The maximum

operating frequency of HCLKX2, HCLK, and PCLK are 266MHz, 133MHz, and 66MHz, respectively. NAND,

SECUR, JPEG operating clock cannot exceed 66MHz. MFC and CAM operating clock cannot exceed 133MHz.

This operating clock condition must be met through CLK_DIV0 configuration.

这是手册上的一段话,也就是HCLK*2的频率不能超过266Mhz。jpeg,cam频率都有限制。 APLL给ARM CPU使用

MPLL给主设备、HCLK(内存,DDR),PCLK(外设片上模块)

EPLL给其它模块

异步模式: OTHERS寄存器设置为异步模式

读入OTHERS内存的值,并bic清0xc0

当arm时钟和Hclk不一样的时候使,要设置成异步 循环判断,等待设置完成

分频设置:要使我们的时钟正常工作,还要设置相应的分频参数,具体如下: 分频参数主要在CLK_DIV0里面设置。 设置CLK_DVIO

设置ARM_RATIO 0 主核分频为1分频

设置HCLCKX2_RATIO 1 将输入的时钟进行2分频

设置HCLK_RATIO 1 再将输入的时钟2分频,能供内存使用

设置PCLK_RATIO 3 其他RATIO的设置

设置流程:

/*************************************************************************/

/*名称:系统时钟设置 */

/*参数:ARM_CLK=532 HCLK=133 HCLKX2=266 PCLK=66.5 */

/*************************************************************************/

#define rAPLL_LOCK (*((volatile unsigned long *)0x7E00F000))

#define rMPLL_LOCK (*((volatile unsigned long *)0x7E00F004))

#define rEPLL_LOCK (*((volatile unsigned long *)0x7E00F008))

#define rAPLL_CON (*((volatile unsigned long *)0x7E00F00C))

#define rMPLL_CON (*((volatile unsigned long *)0x7E00F010))

#define rCLK_SRC (*((volatile unsigned long *)0x7E00F01C))

#define rCLK_DIV0 (*((volatile unsigned long *)0x7E00F020))

#define rCLK_DIV1 (*((volatile unsigned long *)0x7E00F024))

#define rCLK_DIV2 (*((volatile unsigned long *)0x7E00F028))

#define rOTHERS (*((volatile unsigned long *)0x7E00F900))

#define ARM_RATIO 0 /* ARMCLK = DOUTAPLL / (ARM_RATIO + 1) */

#define HCLKX2_RATIO 1 /* HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1) */

#define HCLK_RATIO 1 /* HCLK = HCLKX2 / (HCLK_RATIO + 1) */

#define PCLK_RATIO 3 /* PCLK = HCLKX2 / (PCLK_RATIO + 1) */

#define MPLL_RATIO 0 /* DOUTMPLL = MOUTMPLL / (MPLL_RATIO + 1) */

#define SDIV 1

#define PDIV 3

#define MDIV 266

#define EN 1 //使能PLL

void Clock_Init()

{

rAPLL_LOCK = 0x0000ffff;

rMPLL_LOCK = 0x0000ffff;

rEPLL_LOCK = 0x0000ffff; //时钟锁存时间设定

rOTHERS &= ~( 3 << 6); //将时钟设置成异步模式

while( (rOTHERS & 0xf00) != 0 );//等待进入异步模式

rCLK_DIV0 = ARM_RATIO | (MPLL_RATIO << 4) | (HCLK_RATIO << 8) | (HCLKX2_RATIO << 9) | (PCLK_RATIO << 12);//设置CLK_DIV0的分频参数

rAPLL_CON = SDIV | (PDIV << 8) | (MDIV << 16) | (EN << 31);//设置FOUT=532M

rMPLL_CON = SDIV | (PDIV << 8) | (MDIV << 16) | (EN << 31);//设置FOUT=532M

rCLK_SRC = 0x03;//时钟源选择}在汇编启动代码中,在跳转到main函数之前,加上一下一句,即可设置时钟

bl clock_init

main函数,我就按照韦东山老师的视频教学上说的,写流水灯代码,可以看到如果延时不够,则流水灯跑得非常快。