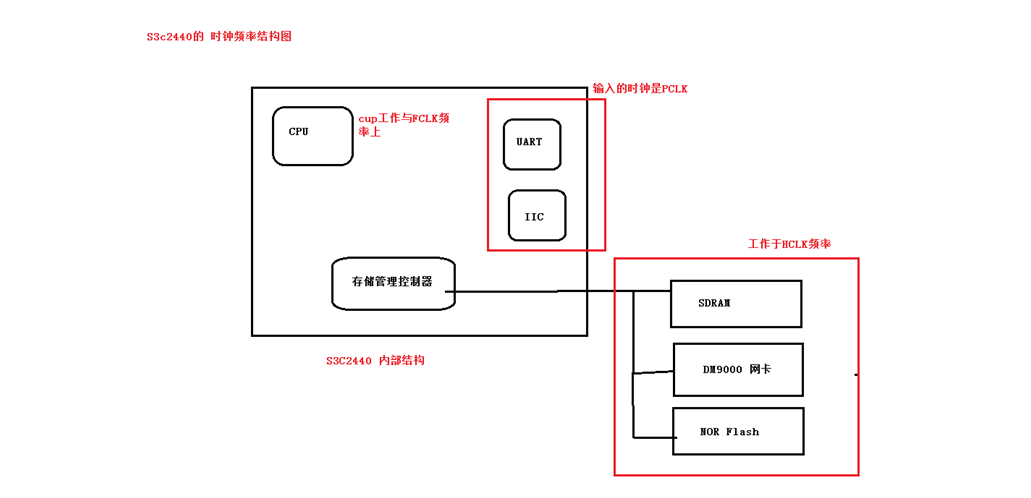

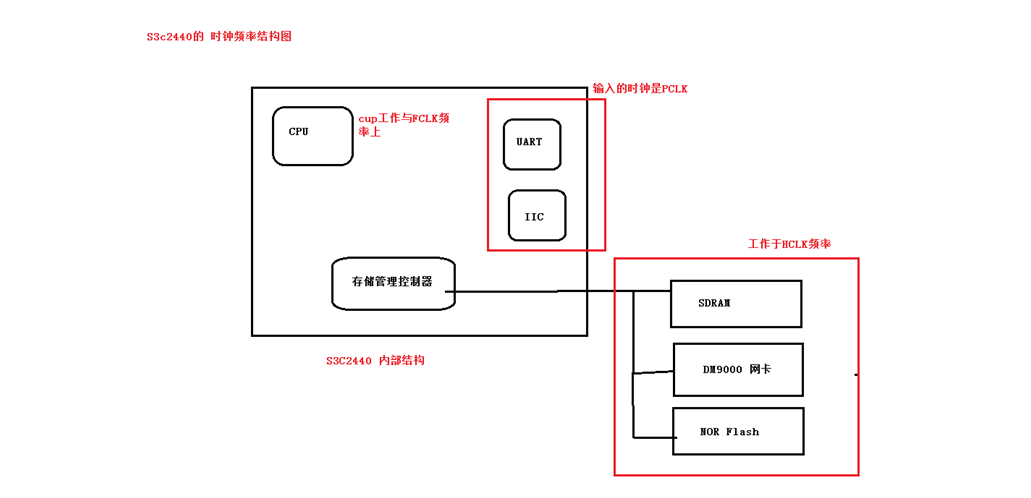

一 , S3c2440 时钟:

S3c2400 cup 最高工作频率为400M => FCLK

存储管理设备 example: SDRAM 网卡 norflash 频率为 100 M~ 133M =>HCLK

S3c2440 内部外设设备 : uart 定时器 IIC 50M => PCLK

1),S3c2440 内部结构:

2),怎么设置 FCLK HCLK PCLK

2),怎么设置 FCLK HCLK PCLK

Jz2440 开发板接的是 12M的晶振 为了提高cup使用频率 设置锁定时间寄存器 相关的寄存器:

设置 MPLL控制寄存器 达到400M : MPLL Mpll( FCLK ) = (2 * m * Fin) / (p * 2S) m = (MDIV + 8), p = (PDIV + 2), s = SDIV

分频HCLK PCLK FCLK 控制寄存器:

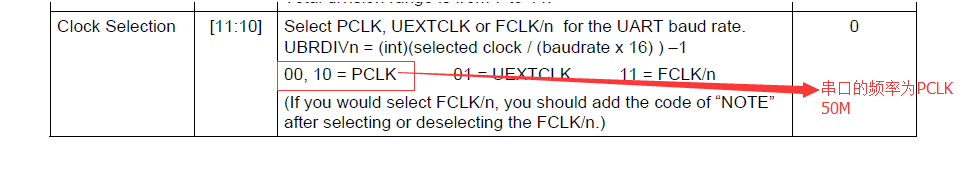

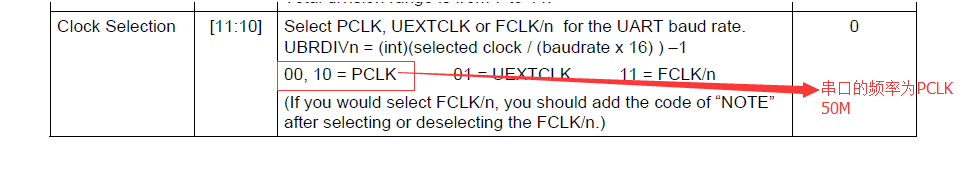

二 , UART 串口

首先如何在PC上使用 串口

1 ,确定使用哪个串口

2 , 设置 波特率 流控 数据位 校验位 停止位

3, 收发数据

USRT的初始化

二 , UART 串口

首先如何在PC上使用 串口

1 ,确定使用哪个串口

2 , 设置 波特率 流控 数据位 校验位 停止位

3, 收发数据

USRT的初始化

2),怎么设置 FCLK HCLK PCLK

2),怎么设置 FCLK HCLK PCLK

#define S3C2410_MPLL_200MHZ ((0x5c<<12)|(0x04<<4)|(0x00))

#define S3C2440_MPLL_200MHZ ((0x5c<<12)|(0x01<<4)|(0x02))

/*

* 对于MPLLCON寄存器,[19:12]为MDIV,[9:4]为PDIV,[1:0]为SDIV

* 有如下计算公式:

* S3C2410: MPLL(FCLK) = (m * Fin)/(p * 2^s)

* S3C2440: MPLL(FCLK) = (2 * m * Fin)/(p * 2^s)

* 其中: m = MDIV + 8, p = PDIV + 2, s = SDIV

* 对于本开发板,Fin = 12MHz

* 设置CLKDIVN,令分频比为:FCLK:HCLK:PCLK=1:2:4,

* FCLK=200MHz,HCLK=100MHz,PCLK=50MHz

*/

void clock_init(void)

{

// LOCKTIME = 0x00ffffff; // 使用默认值即可

CLKDIVN = 0x03; // FCLK:HCLK:PCLK=1:2:4, HDIVN=1,PDIVN=1

/* 如果HDIVN非0,CPU的总线模式应该从“fast bus mode”变为“asynchronous bus mode” */

__asm__(

"mrc p15, 0, r1, c1, c0, 0

" /* 读出控制寄存器 */

"orr r1, r1, #0xc0000000

" /* 设置为“asynchronous bus mode” */

"mcr p15, 0, r1, c1, c0, 0

" /* 写入控制寄存器 */

);

/* 判断是S3C2410还是S3C2440 */

if ((GSTATUS1 == 0x32410000) || (GSTATUS1 == 0x32410002))

{

MPLLCON = S3C2410_MPLL_200MHZ; /* 现在,FCLK=200MHz,HCLK=100MHz,PCLK=50MHz */

}

else

{

MPLLCON = S3C2440_MPLL_200MHZ; /* 现在,FCLK=200MHz,HCLK=100MHz,PCLK=50MHz */

}

}

Jz2440 开发板接的是 12M的晶振 为了提高cup使用频率 设置锁定时间寄存器 相关的寄存器:

设置 MPLL控制寄存器 达到400M : MPLL Mpll( FCLK ) = (2 * m * Fin) / (p * 2S) m = (MDIV + 8), p = (PDIV + 2), s = SDIV

分频HCLK PCLK FCLK 控制寄存器:

二 , UART 串口

首先如何在PC上使用 串口

1 ,确定使用哪个串口

2 , 设置 波特率 流控 数据位 校验位 停止位

3, 收发数据

USRT的初始化

二 , UART 串口

首先如何在PC上使用 串口

1 ,确定使用哪个串口

2 , 设置 波特率 流控 数据位 校验位 停止位

3, 收发数据

USRT的初始化

void uart0_init(void)

{

GPHCON |= 0xa0; // GPH2,GPH3用作TXD0,RXD0

GPHUP = 0x0c; // GPH2,GPH3内部上拉

ULCON0 = 0x03; // 8N1(8个数据位,无较验,1个停止位)

UCON0 = 0x05; // 查询方式,UART时钟源为PCLK

UFCON0 = 0x00; // 不使用FIFO

UMCON0 = 0x00; // 不使用流控

UBRDIV0 = UART_BRD; // 波特率为115200

/* #define PCLK 50000000 // init.c中的clock_init函数设置PCLK为50MHz

*#define UART_CLK PCLK // UART0的时钟源设为PCLK

*#define UART_BAUD_RATE 115200 // 波特率

* #define UART_BRD ((UART_CLK / (UART_BAUD_RATE * 16)) - 1)

*/

}