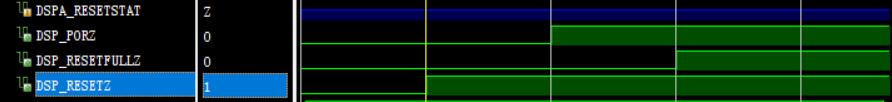

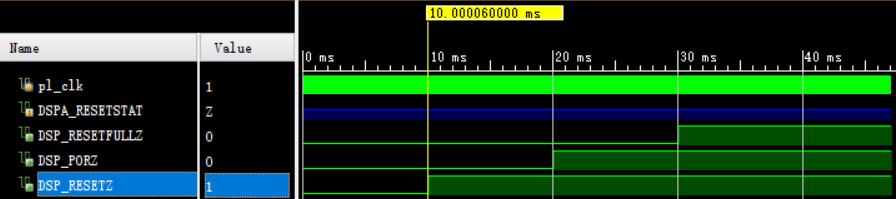

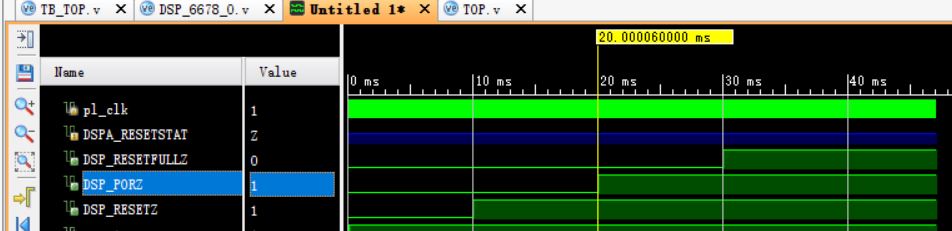

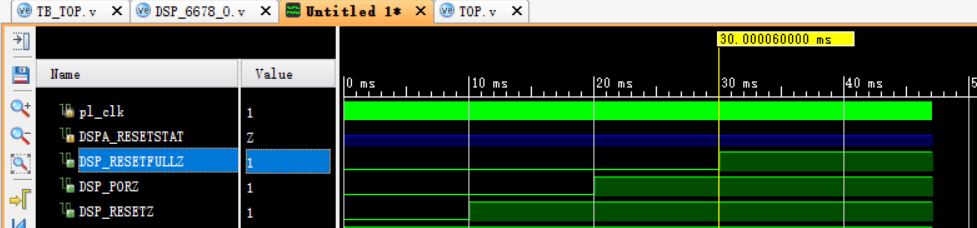

一.复位时序图

二.信号线间隔时间

间隔时间依次为 10ms

三.复位源码

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: fengzihao

//

// Create Date: 2018/01/13 14:21:35

// Design Name:

// Module Name: DSP_6678_0

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module DSP_6678_0(

input reset,

input clk_50m,

input DSPA_RESETSTAT,

output DSP_PORZ,

output DSP_RESETFULLZ,

output DSP_RESETZ

);

reg [18:0] counter1 = 0;

reg [21:0] counter2 = 0;

reg DSP_RESET_N = 0;

reg [18:0] counter3 = 0;

reg DSP_POR_N = 0;

reg [18:0] counter4 = 0;

reg DSP_RESETFULL_N = 0;

assign DSP_PORZ = DSP_POR_N;

assign DSP_RESETZ = DSP_RESET_N;

assign DSP_RESETFULLZ = DSP_RESETFULL_N;

// DSP_RESETZ : low '0' for 5 ms

always@(posedge clk_50m or posedge reset)

begin

if(~reset)

begin

counter2 <= 0;

end

else if((counter2<22'd249999))

begin

counter2 <= counter2+1;

end

else

begin

counter2 <= counter2;

end

end

always@(posedge clk_50m or posedge reset)

begin

begin

if(~reset)

begin

DSP_RESET_N <= 1'b0;

end

else if(counter2==22'd249999)

begin

DSP_RESET_N <= 1'b1;

end

else

begin

DSP_RESET_N <= 1'b0;

end

end

end

// DSP_PORZ : low for about 10 ms

always@(posedge clk_50m or posedge reset)//Switch_FPGA_RESET_N

begin

if(~reset)

begin

counter3 <= 0;

end

else if(DSP_RESET_N&&(counter3<19'd249999))

begin

counter3 <= counter3+1;

end

else

begin

counter3 <= counter3;

end

end

always@(posedge clk_50m or posedge reset)

begin

if(~reset)

begin

DSP_POR_N <= 0;

end

else if(counter3==19'd249999)

begin

DSP_POR_N <= 1;

end

else

begin

DSP_POR_N <= 0;

end

end

// DSP_RESETFULL_N : low for about 15 ms

always@(posedge clk_50m or posedge reset)//Switch_FPGA_RESET_N

begin

if(~reset)

begin

counter4 <= 0;

end

else if(DSP_POR_N && (counter4<19'd249999))

begin

counter4 <= counter4+1;

end

else

begin

counter4 <= counter4;

end

end

always@(posedge clk_50m or posedge reset)

begin

if(~reset)

begin

DSP_RESETFULL_N <= 0;

end

else if(counter4==19'd249999)

begin

DSP_RESETFULL_N <= 1;

end

else

begin

DSP_RESETFULL_N <= 0;

end

end // always@ (posedge clk_50m or posedge reset)

endmodule