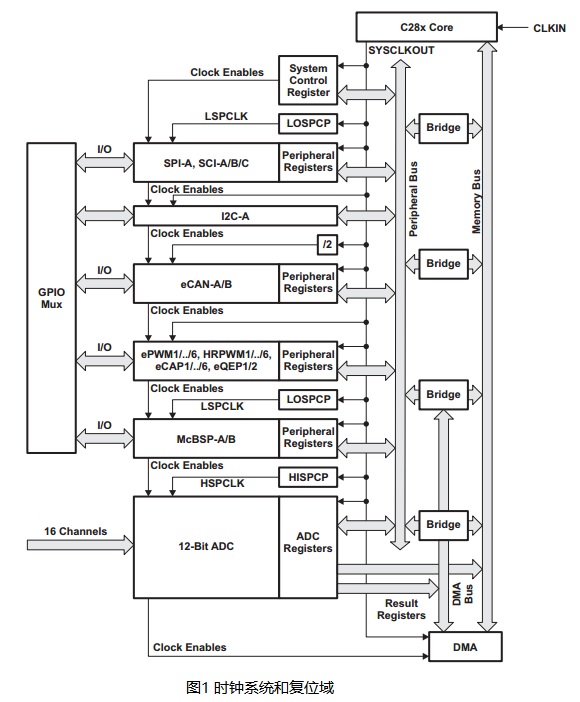

TMS320F28335通过外部时钟信号、OSC和PLL产生倍频时钟信号CLKIN后,CLKIN经过CPU后产生时钟SYSCLKOUT(CLKIN和SYSCLKOUT频率是一样的),SYSCLKOUT给各个片内外设提供时钟信号。为了实现低功耗和提供高低频率时钟信号,需要把SYSCLKOUT进一步分频,本章主要讲解了对SYSCLKOUT分频产生低频时钟信号和高频时钟信号,完成外设时钟初始化的过程。

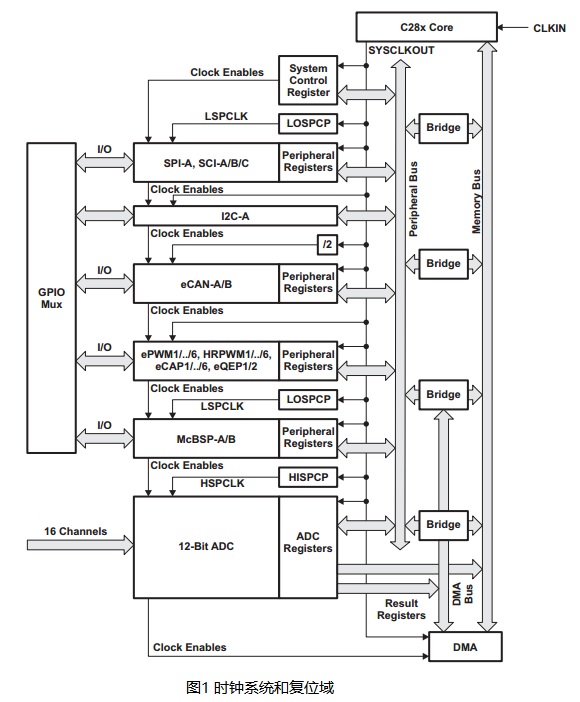

从图1可以看出,时钟CLKIN经过CPU后产生时钟SYSCLKOUT(CLKIN和SYSCLKOUT频率是一样的),SYSCLKOUT给各个片内外设提供时钟;除了SPI、SCI、McBSP模块使用低频时钟,ADC使用高频时钟外,其他外设模块都是采用SYSCLKOUT时钟。为了实现低功耗,必须对每个片内外设时钟进行开关控制;为了实现高低频率时钟,必须对SYSCLKOUT进行不同的分频处理,因此与外设时钟配置相关的寄存器主要有两类:外设时钟控制寄存器PCLKCR和高低频外设时钟分频寄存器SPCP。

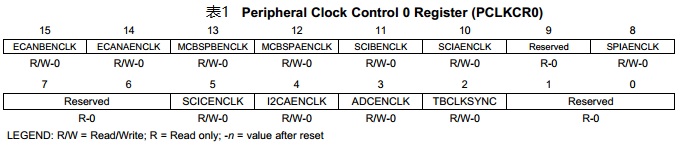

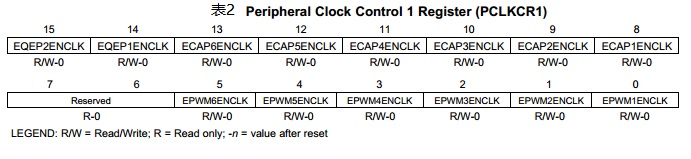

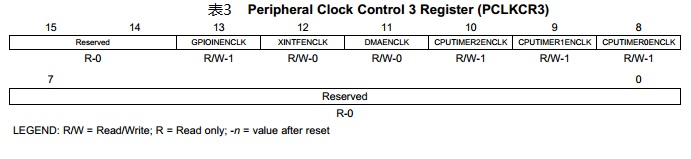

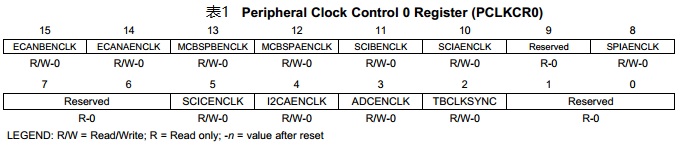

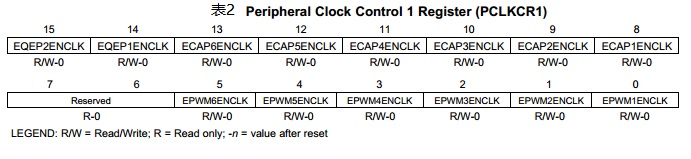

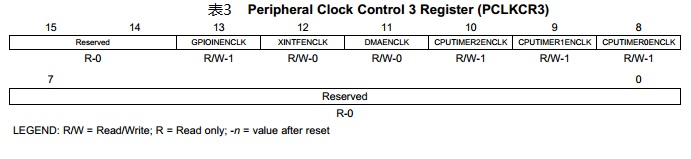

从表1、表2、表3可以看出,默认情况下,除了3个CPU定时器和GPIO口输入采样时钟使能外,其他所有外设的时钟是禁用的。

从表1、表2、表3可以看出,默认情况下,除了3个CPU定时器和GPIO口输入采样时钟使能外,其他所有外设的时钟是禁用的。

**注:

- PCLKCR0、PCLKCR1、PCLKCR3均受ELLOW保护。

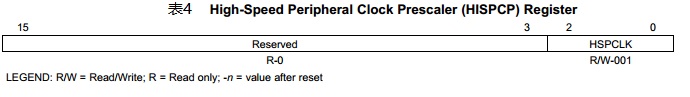

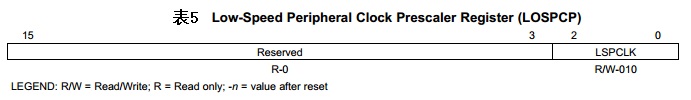

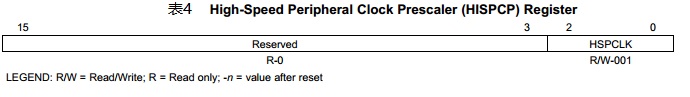

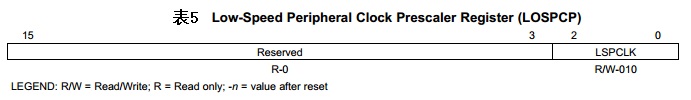

- 不使用某外设模块时,可以禁用该时钟模块的时钟以省电。 ** 产生高低频外设时钟的分频寄存器HISPCP和LOSPCP分别如表4和表5所示。

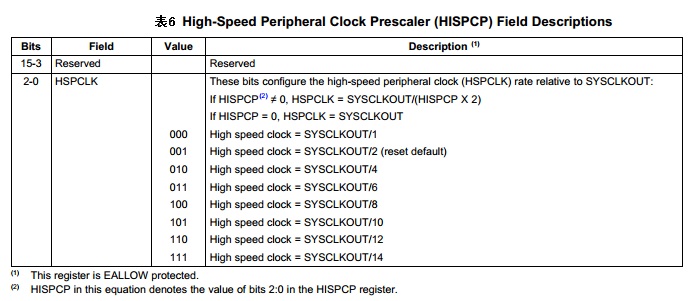

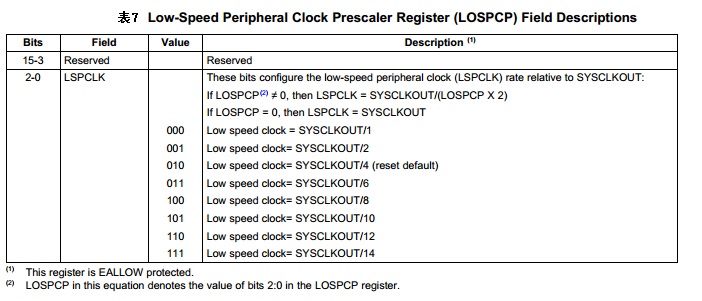

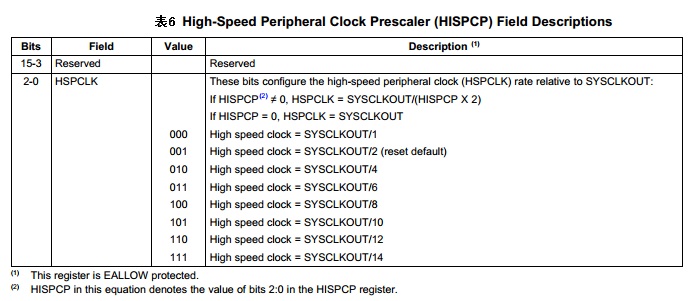

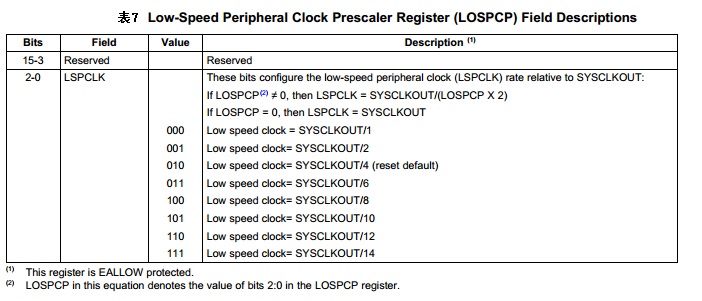

两个寄存器具体位域描述分别如表6和表7所示。

两个寄存器具体位域描述分别如表6和表7所示。

从表4到表7可以看出,16位的高频外设时钟分频寄存器HISPCP和低频外设时钟分频寄存器LOSPCP都只用了低3位;两个寄存器都受ELLOW保护;分频计算方法:当分频系数为0,表示时钟等于SYSCLKOUT/1,当分频系数不为0时,CLK=SYSCLKOUT/(n×2)。

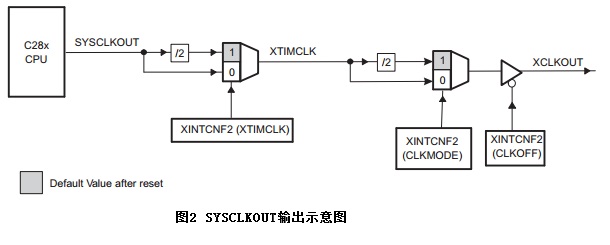

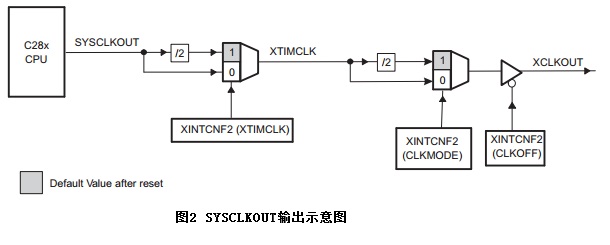

从图2可以看出,上电或复位默认情况下,SYSCLK2分频产生XTIMCLK,XTIMCLK再通过2分频产生XCLKOUT时钟,该时钟信号通过引脚XCLKOUT输出,即默认情况下XCLKOUT=SYSCLK/4=OSCCLK/16,调试时可以观察该引脚的信号以判断设备是否在正确的时钟下工作。

从图2可以看出,上电或复位默认情况下,SYSCLK2分频产生XTIMCLK,XTIMCLK再通过2分频产生XCLKOUT时钟,该时钟信号通过引脚XCLKOUT输出,即默认情况下XCLKOUT=SYSCLK/4=OSCCLK/16,调试时可以观察该引脚的信号以判断设备是否在正确的时钟下工作。

注:

- XCLKOUT引脚上电或者复位默认情况下是激活状态的。

- XCLKOUT引脚没有上拉或者下拉电阻。

- 如果XCLKOUT引脚不使用时,可以通过XINTCNF2[CLKOFF]=1关闭。

- 默认情况下,XTIMCLK=SYSCLKOUT/2,它是外扩模块(外扩FLASH、SRAM等)的时钟

1.时钟系统

时钟系统结构如图1所示。

从图1可以看出,时钟CLKIN经过CPU后产生时钟SYSCLKOUT(CLKIN和SYSCLKOUT频率是一样的),SYSCLKOUT给各个片内外设提供时钟;除了SPI、SCI、McBSP模块使用低频时钟,ADC使用高频时钟外,其他外设模块都是采用SYSCLKOUT时钟。为了实现低功耗,必须对每个片内外设时钟进行开关控制;为了实现高低频率时钟,必须对SYSCLKOUT进行不同的分频处理,因此与外设时钟配置相关的寄存器主要有两类:外设时钟控制寄存器PCLKCR和高低频外设时钟分频寄存器SPCP。

第一类寄存器是外设时钟控制寄存器PCLKCR,它包括16位的PCLKCR0、PCLKCR1、PCLKCR3(不知道为什么跳过了PCLKCR2??),主要是控制使能和禁用外设时钟;

第二类寄存器是高低频外设时钟分频寄存器,它包括高频外设时钟分频寄存器16位的HISPCP(High-Speed Peripheral Clock Prescaler Register)和低频外设时钟分频寄存器16位的LOSPCP(Low-Speed Peripheral Clock Prescaler Register)

2.与外设时钟配置相关的寄存器

控制片内外设时钟开关的外设时钟控制寄存器PCLKCR0、PCLKCR1、PCLKCR3如表1、表2、表3所示。

从表1、表2、表3可以看出,默认情况下,除了3个CPU定时器和GPIO口输入采样时钟使能外,其他所有外设的时钟是禁用的。

从表1、表2、表3可以看出,默认情况下,除了3个CPU定时器和GPIO口输入采样时钟使能外,其他所有外设的时钟是禁用的。 **注:

- PCLKCR0、PCLKCR1、PCLKCR3均受ELLOW保护。

- 不使用某外设模块时,可以禁用该时钟模块的时钟以省电。 ** 产生高低频外设时钟的分频寄存器HISPCP和LOSPCP分别如表4和表5所示。

两个寄存器具体位域描述分别如表6和表7所示。

两个寄存器具体位域描述分别如表6和表7所示。

从表4到表7可以看出,16位的高频外设时钟分频寄存器HISPCP和低频外设时钟分频寄存器LOSPCP都只用了低3位;两个寄存器都受ELLOW保护;分频计算方法:当分频系数为0,表示时钟等于SYSCLKOUT/1,当分频系数不为0时,CLK=SYSCLKOUT/(n×2)。

3.时钟输出

SYSCLKOUT可以按1、2、4分频从TMS320F28335的XCLKOUT引脚输出,SYSCLKOUT输出示意图如2所示。 从图2可以看出,上电或复位默认情况下,SYSCLK2分频产生XTIMCLK,XTIMCLK再通过2分频产生XCLKOUT时钟,该时钟信号通过引脚XCLKOUT输出,即默认情况下XCLKOUT=SYSCLK/4=OSCCLK/16,调试时可以观察该引脚的信号以判断设备是否在正确的时钟下工作。

从图2可以看出,上电或复位默认情况下,SYSCLK2分频产生XTIMCLK,XTIMCLK再通过2分频产生XCLKOUT时钟,该时钟信号通过引脚XCLKOUT输出,即默认情况下XCLKOUT=SYSCLK/4=OSCCLK/16,调试时可以观察该引脚的信号以判断设备是否在正确的时钟下工作。 注:

- XCLKOUT引脚上电或者复位默认情况下是激活状态的。

- XCLKOUT引脚没有上拉或者下拉电阻。

- 如果XCLKOUT引脚不使用时,可以通过XINTCNF2[CLKOFF]=1关闭。

- 默认情况下,XTIMCLK=SYSCLKOUT/2,它是外扩模块(外扩FLASH、SRAM等)的时钟

4.外设时钟初始化代码

此初始化代码主要来自TI官方例程,注释是个人理解。/*

*函数名称:InitPeripheralClocks

*输入参数:无

*输出参数:无

*函数功能:初始化外设时钟模块,主要包括产生高低速时钟、开关所需片内外设模块时*钟等

*/

void InitPeripheralClocks(void)

{

EALLOW;

// 高低频外设时钟分频寄存器HISPCP/LOSPCP设置,正常情况下采用默认值,即高频时钟为SYSCLKOUT/2,低速时钟为SYSCLKOUT/4

SysCtrlRegs.HISPCP.all = 0x0001;

SysCtrlRegs.LOSPCP.all = 0x0002;

// 时钟输出引脚XCLKOUT设置,默认情况XCLKOUT = SYSCLKOUT/4

// XTIMCLK = SYSCLKOUT/2

XintfRegs.XINTCNF2.bit.XTIMCLK = 1;//extern interface clock<->XinfCLK

// XCLKOUT = XTIMCLK/2

XintfRegs.XINTCNF2.bit.CLKMODE = 1;

// Enable XCLKOUT

XintfRegs.XINTCNF2.bit.CLKOFF = 0;

// 给所选用外设使能外设时钟

// 如果不使用某外设模块,禁用它的时钟以省电

// 下面代码要根据自己使用的外设模块进行相应的修改

SysCtrlRegs.PCLKCR0.bit.ADCENCLK = 1; // ADC

// *重要提醒*

// ADC_cal()函数, 可以从TI保留的OTP中复制ADC校验值,并将校验值赋值给ADCREFSEL和ADCOFFTRIM寄存器,该过程在BOOT ROM中自动地完成

//如果在调试过程中,BOOT ROM代码旁路未使用,那么必须显示调用下面 ADC_cal()函数(推荐显示调用)

//在调用 ADC_cal()前,必须使能ADC时钟

// 有关ADC更多的信息参见设备数据手册

ADC_cal();

//本例中使能了所有片内外设模块时钟

SysCtrlRegs.PCLKCR0.bit.I2CAENCLK = 1; // I2C

SysCtrlRegs.PCLKCR0.bit.SCIAENCLK = 1; // SCI-A

SysCtrlRegs.PCLKCR0.bit.SCIBENCLK = 1; // SCI-B

SysCtrlRegs.PCLKCR0.bit.SCICENCLK = 1; // SCI-C

SysCtrlRegs.PCLKCR0.bit.SPIAENCLK = 1; // SPI-A

SysCtrlRegs.PCLKCR0.bit.MCBSPAENCLK = 1; // McBSP-A

SysCtrlRegs.PCLKCR0.bit.MCBSPBENCLK = 1; // McBSP-B

SysCtrlRegs.PCLKCR0.bit.ECANAENCLK=1; // eCAN-A

SysCtrlRegs.PCLKCR0.bit.ECANBENCLK=1; // eCAN-B

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the ePWM

SysCtrlRegs.PCLKCR1.bit.EPWM1ENCLK = 1; // ePWM1

SysCtrlRegs.PCLKCR1.bit.EPWM2ENCLK = 1; // ePWM2

SysCtrlRegs.PCLKCR1.bit.EPWM3ENCLK = 1; // ePWM3

SysCtrlRegs.PCLKCR1.bit.EPWM4ENCLK = 1; // ePWM4

SysCtrlRegs.PCLKCR1.bit.EPWM5ENCLK = 1; // ePWM5

SysCtrlRegs.PCLKCR1.bit.EPWM6ENCLK = 1; // ePWM6

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the ePWM

SysCtrlRegs.PCLKCR1.bit.ECAP3ENCLK = 1; // eCAP3

SysCtrlRegs.PCLKCR1.bit.ECAP4ENCLK = 1; // eCAP4

SysCtrlRegs.PCLKCR1.bit.ECAP5ENCLK = 1; // eCAP5

SysCtrlRegs.PCLKCR1.bit.ECAP6ENCLK = 1; // eCAP6

SysCtrlRegs.PCLKCR1.bit.ECAP1ENCLK = 1; // eCAP1

SysCtrlRegs.PCLKCR1.bit.ECAP2ENCLK = 1; // eCAP2

SysCtrlRegs.PCLKCR1.bit.EQEP1ENCLK = 1; // eQEP1

SysCtrlRegs.PCLKCR1.bit.EQEP2ENCLK = 1; // eQEP2

SysCtrlRegs.PCLKCR3.bit.CPUTIMER0ENCLK = 1; // CPU Timer 0

SysCtrlRegs.PCLKCR3.bit.CPUTIMER1ENCLK = 1; // CPU Timer 1

SysCtrlRegs.PCLKCR3.bit.CPUTIMER2ENCLK = 1; // CPU Timer 2

SysCtrlRegs.PCLKCR3.bit.DMAENCLK = 1; // DMA Clock

SysCtrlRegs.PCLKCR3.bit.XINTFENCLK = 1; // XTIMCLK

SysCtrlRegs.PCLKCR3.bit.GPIOINENCLK = 1; // GPIO input clock

EDIS;

}- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75