一.说明DSP Builder的主要功能

定义:Altera可编程逻辑器件(PLD)

中的DSP系统设计需要高级算法和

HDL开发工具,中文名为DSP

系统设计开发工具。

功能:①支持系统、算法和硬件设计共享一个公共开发平台,从而缩短了

DSP设计周期。②DSP Builder

包括比特和周期精度的Simulink模块,涵盖了算法和存储功能等基本操作。③使用

DSP Builder模型中的MegaCore功能实现复杂功能的集成。

二.说明DSP Builder的设计流程

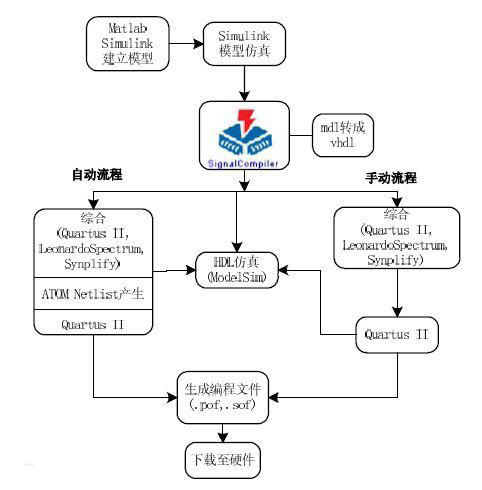

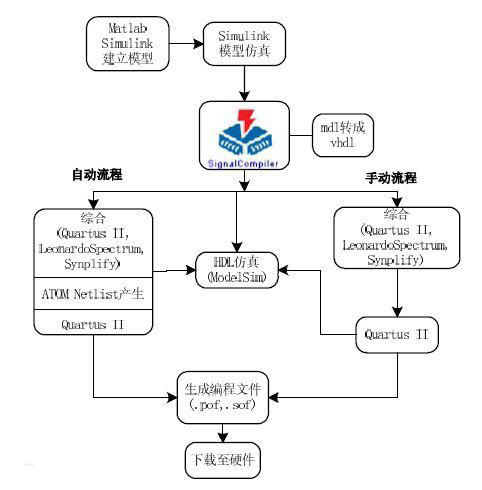

基于

DSP Builder的设计流程是一个完全自顶向下的设计流程,包括从系统描述到硬件实现都可以在一个完整的设计环境中完成。其具体开发流程如图所示,整个DSP Builder的设计过程可分为以下几个步骤:

①利用

Simulink模块及DSP Builder模块在MATLAB/Simulink中对DSP系统进行建模,并对各模块进行相应的参数设置,同时基于Simulink平台仿真验证所搭建DSP系统的功能。②利用

DSP Builder工具箱中的Signal Compiler模块,对所建立的模型进行编译,将Simulink模块文件(. mdl)转换成RTL级的VHDL代码描述以及用于综合、仿真、编译的tcl脚本。③在得到

VHDL文件后,可以选择自动流程或手工流程进行下一步设计。如果采用自动流程,则几乎可以忽略硬件的具体实现过程,选择让DSP Builder

自动调用Quartus II等EDA软件。④针对第二步生成的

VHDL,进行硬件上的仿真,利用自动生成的ModelSim的tcl脚本和仿真激励文件所做的仿真为功能仿真,而当由Quartus II编译后生成的VHDL仿真激励文件和ModelSim tcl脚本进行的仿真为时序仿真。

三.论述Matlab,Simulink,DSP Builder,ModelSim,QuartusII几种软件工具之间的关系

所设计的模型进行

Simulink系统级仿真,并将输出的图像结果与MATLAB理论结果进行对比,以验证设计的准确性,由于Simulink中的仿真是属于系统级的,是对.mdl文件进行的仿真,而生成的VHDL语言是RTL级的,是针对具体的硬件结构的,这两者有可能存在软件理解上的差异,转换后的VHDL代码实现可能与.mdl模型的实现情况不完全相符,所以在进行Simulink仿真之后,还需要进行ModelSim仿真,检测各控制信号和数据信号,以验证所生成VHDL代码的正确性,最后给出测试结果分析。

①Matlab/Simulink

建模 ②系统仿真

③DSP Builder

完成VHDL转换、综合、适配④ModelSim

对TestBench功能仿真 ⑤Quartus II

直接完成适配(进行优化设置) ⑥Quaruts II

完成时序仿真 ⑦引脚锁定

⑧下载

/配置与嵌入式逻辑分析仪实时测试⑨对配置器件编程,设计完成。

Matlab

,Simulink,DSP Builder,ModelSim,QuartusII这几种软件工具相互作用,层层递进,致使实验结果与实际误差最小,且最优化。

①Matlab/Simulink建模 ②系统仿真 ③DSP Builder完成VHDL转换、综合、适配④ModelSim对TestBench功能仿真 ⑤Quartus II直接完成适配(进行优化设置) ⑥Quaruts II完成时序仿真 ⑦引脚锁定 ⑧下载/配置与嵌入式逻辑分析仪实时测试⑨对配置器件编程,设计完成。

①Matlab/Simulink建模 ②系统仿真 ③DSP Builder完成VHDL转换、综合、适配④ModelSim对TestBench功能仿真 ⑤Quartus II直接完成适配(进行优化设置) ⑥Quaruts II完成时序仿真 ⑦引脚锁定 ⑧下载/配置与嵌入式逻辑分析仪实时测试⑨对配置器件编程,设计完成。

Matlab,Simulink,DSP Builder,ModelSim,QuartusII这几种软件工具相互作用,层层递进,致使实验结果与实际误差最小,且最优化。

Matlab,Simulink,DSP Builder,ModelSim,QuartusII这几种软件工具相互作用,层层递进,致使实验结果与实际误差最小,且最优化。