PLL作用就是对外部时钟进行倍频,降低产生高频时钟信号的成本。但是倍频配置的时候,需要在特定的条件下更改,因此需要检测PLL工作的各种状态信号,因此PLL有两个配置相关寄存器,PLL状态寄存器PLLSTS和PLL控制寄存器PLLCR。通过对状态寄存器PLLSTS的判断,可以判断PLL的工作状态,在特定的工作状态下,对PLL控制寄存器PLLCR进行配置,最后产生合适的时钟信号CLKIN输入给CPU,完成整个过程的倍频。本文详细介绍了PLL模块,并对初始化过程和初始化代码进行了分析。

基于 PLL 的时钟模块提供两种操作模式:

基于 PLL 的时钟模块提供两种操作模式:

• 晶振操作模式:允许使用一个外部晶振/谐振器来提供到器件的时基。

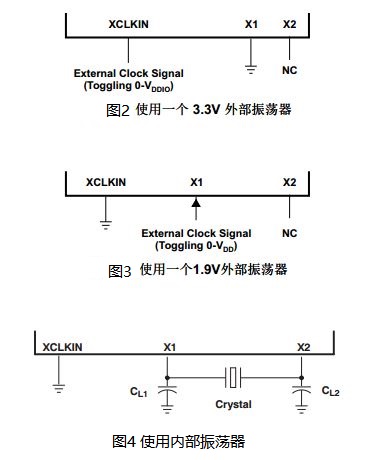

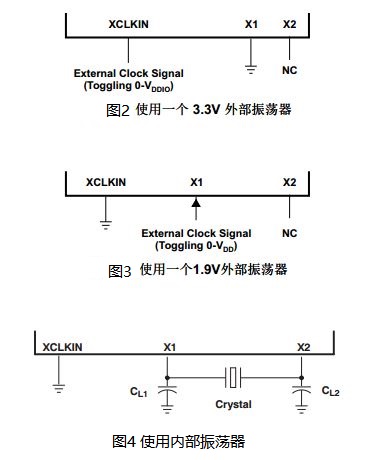

• 外部时钟源操作模式:允许旁通内部振荡器被,时钟由一个 X1 或者 XCLKIN 引脚上的外部时钟源输入生成。 三种输入时钟配置如图2、图3、图4所示

30MHz 外部石英晶振的典型技术规范如下:

30MHz 外部石英晶振的典型技术规范如下:

• 基本模式、 并联谐振

• CL( 负载电容) =12pF

• CL1=CL2=24pF

• C并联=6pF

• ESR 范围 = 25 至 40Ω

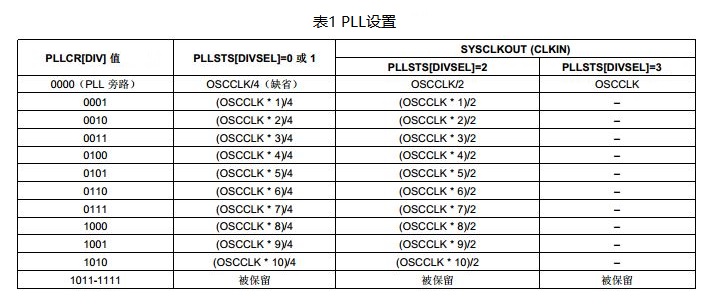

分频系数的选择如表2所示。

分频系数的选择如表2所示。

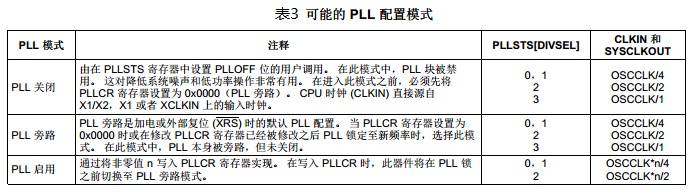

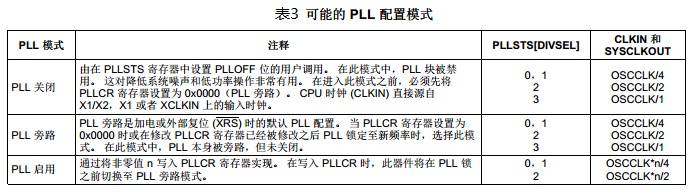

PLL可能的配置模式如表3所示。

PLL可能的配置模式如表3所示。

注:

注:

(1)默认情况下,分频系数为4

(2)在改变PLLCR[DIV]倍频系数前,必须满足两个条件:

(4)在写入 PLLCR 寄存器之前, 安全装置模块(看门狗)应该被禁用。

(5)在 PLL 模块稳定后,重新启用安全装置模块(看门狗),重启的时间为 131072 个 OSCCLK 周期。

(6)在 PLL (VCOCLK) 的输出频率不超过300MHz 时候,选择输入时钟和 PLLCR[DIV] 位。

(7)当PLL激活时,即PLL不是旁路(PLLCR[DIV]!=0),必须需要分频器,即分频系数不能为1(PLLSTS[DIVSEL]!=3),这是因为确保反馈给内核的时钟具有正确的占空比。

(8)只有外部复位信号RST和安全装置(看门狗)产生复位信号时,PLLCR和PLLSTS才会复位到默认值,而调试器和Missing clock detect logic产生的复位信号不会使两者复位到默认值。

(9)PLLCR和PLLSTS是受ELLOW保护的。

特别注意:倍频时一定要分频,不倍频时才允许不分频。

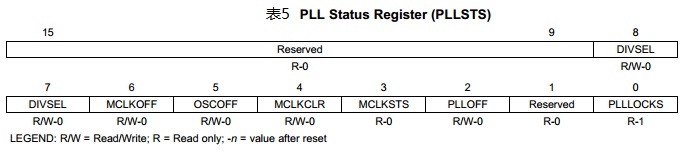

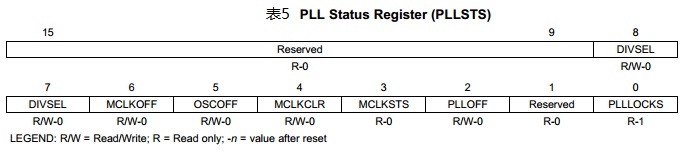

PLL状态寄存器PLLSTS如表5所示。

PLL状态寄存器PLLSTS如表5所示。

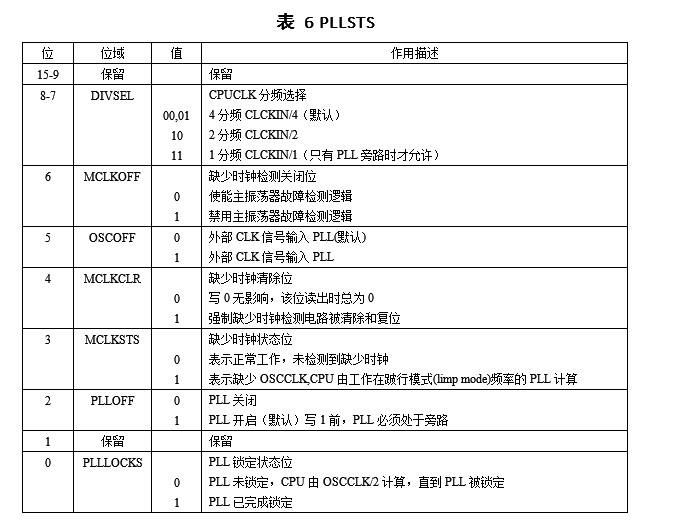

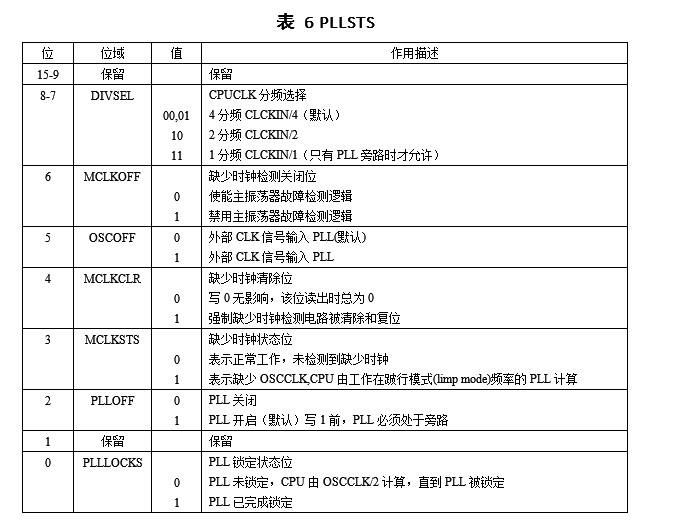

PLLSTS各位的描述如表6所示

PLLSTS各位的描述如表6所示

注:跛行模式(limp mode)系统出现问题的时候,控制逻辑能够根据对应的条件进行判断,安排另外的一套控制电平,使得必须控制的负载按照既定的逻辑运行。

注:跛行模式(limp mode)系统出现问题的时候,控制逻辑能够根据对应的条件进行判断,安排另外的一套控制电平,使得必须控制的负载按照既定的逻辑运行。

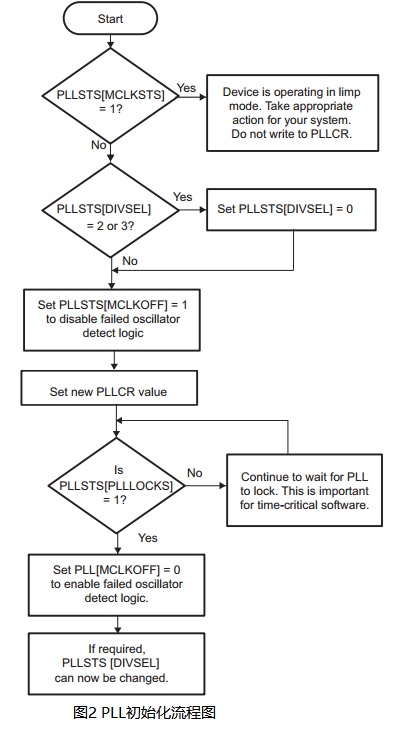

根据流程图,大致可以描述PLL的初始化过程为:

(1)确保存在OSCCLK,系统能正常工作,即判断PLLSTS[MCLKSTS]==1?

(2)改变PLLCR[DIV]前,确保PLLSTS[DIVSEL]==0

(3)改变PLLCR[DIV]前,禁用主振荡器故障检测逻辑模块,即PLLCR[MCLKOFF]=1

(4)根据需要,改变PLLCR[DIV]

(5)判断PLL是否稳定锁定,即PLLSTS[PLLLOCKS]==1?

(6)使能主振荡器故障检测逻辑模块,即PLLCR[MCLKOFF]=0

(7)根据需要,改变PLLSTS[DIVSEL] PLL初始化的代码如下(来自官方例程,主要对其注释分析和讲解)。

http://www.ti.com.cn/cn/lit/ug/sprufb0d/sprufb0d.pdf

1.OSC和PLL模块

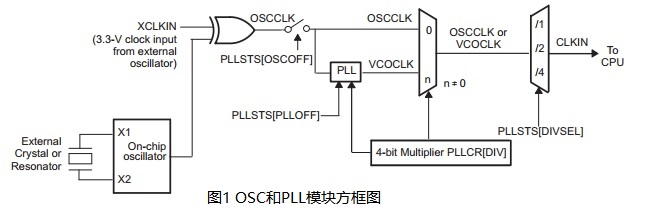

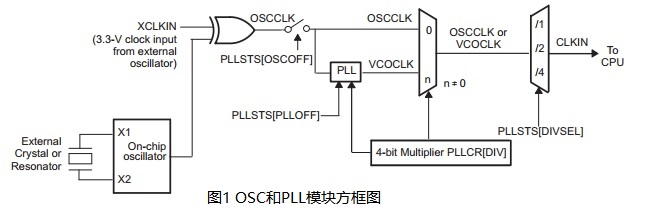

OSC和PLL模块方框图如图1所示。 基于 PLL 的时钟模块提供两种操作模式:

基于 PLL 的时钟模块提供两种操作模式: • 晶振操作模式:允许使用一个外部晶振/谐振器来提供到器件的时基。

• 外部时钟源操作模式:允许旁通内部振荡器被,时钟由一个 X1 或者 XCLKIN 引脚上的外部时钟源输入生成。 三种输入时钟配置如图2、图3、图4所示

30MHz 外部石英晶振的典型技术规范如下:

30MHz 外部石英晶振的典型技术规范如下: • 基本模式、 并联谐振

• CL( 负载电容) =12pF

• CL1=CL2=24pF

• C并联=6pF

• ESR 范围 = 25 至 40Ω

2.基于 PLL 的时钟模块

TMS320F23885上有一个片载、基于PLL倍频器的时钟模块,它提供所有的时钟信号以及实现对低功耗模式的控制。PLL作为DSP的时钟重要组成部分,它除了提高系统内部SYSCLKOUT的频率之外,还有一个重要的用途就是监视外部时钟是不是很好的为DSP内部提供系统时钟。与PLL配置相关的寄存器有两个:PLL状态寄存器PLLSTS和PLL控制寄存器PLLCR,两个寄存器具体的讲解参见第3节。

如果PLL处于使能状态,需要监视PPLSTS寄存器中的MCLKSTS位的状态。如果MCLKSTS被置位,则软件要采集恰当的措施保证系统不出现事故,该措施包括使系统停机、复位等。

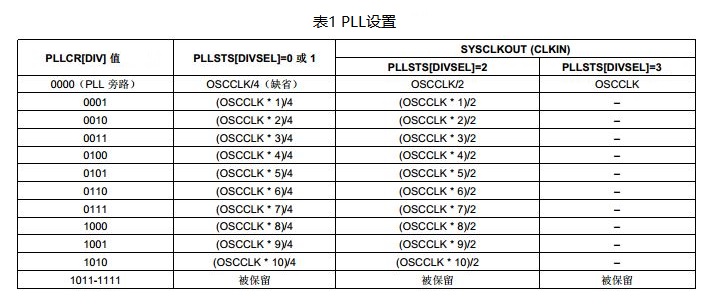

两个寄存器中最关键的位域分别为 2位的PLLSTS[DIVSEL]和4位的PLLCR[DIV]。比如TMS320F23885最大工作时钟为150MHz,通常外部晶振频率为30MHz,先将30MHz进行10倍频变成300MHz,再对300MHz进行2分频得到150MHz的时钟。(官方例程里产生150MHz的方式) PLL的设置如表1所示。

PLLSTS[DIVSEL]选择CPU时钟的分频系数(/4,/2,/1),PLLCR[DIV] 选择CPU时钟的倍频系数(*1,*2,……,*10)。

分频系数的选择如表2所示。

分频系数的选择如表2所示。  PLL可能的配置模式如表3所示。

PLL可能的配置模式如表3所示。  注:

注: (1)默认情况下,分频系数为4

(2)在改变PLLCR[DIV]倍频系数前,必须满足两个条件:

- PLLSTS[DIVSEL]必须为0,而PLLSTS[DIVSEL]改变时,PLL必须完成锁定状态,即PLLSTS[PLLOCKS]必须为1

- DSP不能工作在limp mode下,即PLLSTS[MCLKSTS]必须为0

(4)在写入 PLLCR 寄存器之前, 安全装置模块(看门狗)应该被禁用。

(5)在 PLL 模块稳定后,重新启用安全装置模块(看门狗),重启的时间为 131072 个 OSCCLK 周期。

(6)在 PLL (VCOCLK) 的输出频率不超过300MHz 时候,选择输入时钟和 PLLCR[DIV] 位。

(7)当PLL激活时,即PLL不是旁路(PLLCR[DIV]!=0),必须需要分频器,即分频系数不能为1(PLLSTS[DIVSEL]!=3),这是因为确保反馈给内核的时钟具有正确的占空比。

(8)只有外部复位信号RST和安全装置(看门狗)产生复位信号时,PLLCR和PLLSTS才会复位到默认值,而调试器和Missing clock detect logic产生的复位信号不会使两者复位到默认值。

(9)PLLCR和PLLSTS是受ELLOW保护的。

特别注意:倍频时一定要分频,不倍频时才允许不分频。

3.PLL配置相关的寄存器

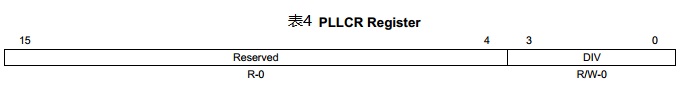

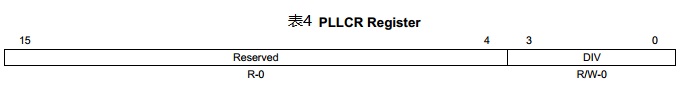

PLL控制寄存器PLLCR如表4所示。 PLL状态寄存器PLLSTS如表5所示。

PLL状态寄存器PLLSTS如表5所示。  PLLSTS各位的描述如表6所示

PLLSTS各位的描述如表6所示  注:跛行模式(limp mode)系统出现问题的时候,控制逻辑能够根据对应的条件进行判断,安排另外的一套控制电平,使得必须控制的负载按照既定的逻辑运行。

注:跛行模式(limp mode)系统出现问题的时候,控制逻辑能够根据对应的条件进行判断,安排另外的一套控制电平,使得必须控制的负载按照既定的逻辑运行。

4.PLL的初始化

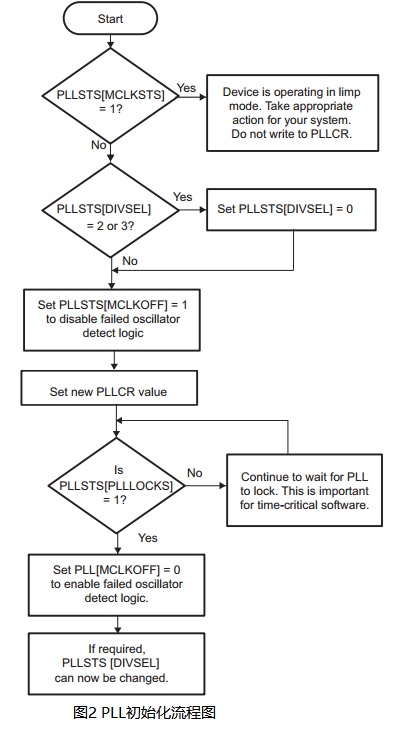

PLL初始化流程图如图2所示。

根据流程图,大致可以描述PLL的初始化过程为:

(1)确保存在OSCCLK,系统能正常工作,即判断PLLSTS[MCLKSTS]==1?

(2)改变PLLCR[DIV]前,确保PLLSTS[DIVSEL]==0

(3)改变PLLCR[DIV]前,禁用主振荡器故障检测逻辑模块,即PLLCR[MCLKOFF]=1

(4)根据需要,改变PLLCR[DIV]

(5)判断PLL是否稳定锁定,即PLLSTS[PLLLOCKS]==1?

(6)使能主振荡器故障检测逻辑模块,即PLLCR[MCLKOFF]=0

(7)根据需要,改变PLLSTS[DIVSEL] PLL初始化的代码如下(来自官方例程,主要对其注释分析和讲解)。

/*

* 函数名称:InitPll

* 函数输入:倍频参数val,分频参数divsel

* val取值为0到10,表示倍频数;divsel取值0到4,0和1表示4分频,2表示2分频,3表示不分频

* 函数输出:无

* 函数调用:InitPll(10,2);

* 先将外部时钟倍频10倍,在分频1/2,最后产生的时钟CLKIN输入CPU28x

*/

void InitPll(unsigned short div, unsigned short divsel)

{

// 确保PLL不是工作在limp mode下,即有外部时钟进入PLL

if (SysCtrlRegs.PLLSTS.bit.MCLKSTS != 0)

{

//检测到无外部时钟,软件要采集恰当的措施保证系统不出现事故,该措施包括

//使系统停机、复位等

//用适合的函数替换下面一行

// SystemShutdown(); function.

asm(" ESTOP0");

}

// PLLCR从0x0000改变前,PLLSTS[DIVSEL]必须为0

// 外部RST复位信号会使PLLSTS[DIVSEL]复位

// 此时分频为1/4

if (SysCtrlRegs.PLLSTS.bit.DIVSEL != 0)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 0;

EDIS;

}

// 前面条件都满足后,可以改变PLLCR[DIV]

if (SysCtrlRegs.PLLCR.bit.DIV != val)

{

EALLOW;

// 在设置PLLCR[DIV]前,要禁用主振荡器检测逻辑

//Missing clock detect logic

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1;

SysCtrlRegs.PLLCR.bit.DIV = div;

EDIS;

//等待PLL稳定且处于锁定状态,即PLLSTS[LOCKS]置位

//等待稳定的时间可能略长,需要禁用看门狗或者循环喂狗

//屏蔽注释,禁用看门够

DisableDog();

while(SysCtrlRegs.PLLSTS.bit.PLLLOCKS != 1)

{

//屏蔽注释,喂狗

// ServiceDog();

}

EALLOW;

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 0;

EDIS;

}

// 如果需要分频1/2

if((divsel == 1)||(divsel == 2))

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = divsel;

EDIS;

}

//注意:下面代码只有在PLL是旁路或者关闭模式时,才可被执行,其他模式禁止。

//倍频时一定要分频,不倍频时才允许不分频

//如果需要切换分频到1/1

// * 首先从默认1/4分频切换到1/2分频,让电源稳定

// 稳定所需要的时间依赖于系统运行速度,此处延时50us只是作为一个特例

// * 稳定后,再切换到1/1

if(divsel == 3)

{

EALLOW;

SysCtrlRegs.PLLSTS.bit.DIVSEL = 2;

DELAY_US(50L);

SysCtrlRegs.PLLSTS.bit.DIVSEL = 3;

EDIS;

}

}- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

5.本章小结

本章介绍OSC和PLL模块,阐述了二种外部时钟输入的操作模式,然后对外部时钟进行倍频分析,即PLL模块,对PLL模块的寄存器和操作进行了详细的分析,最后给出了PLL初始化代码并对代码进行了注释分析。对基本设置特别要强调的是PLL倍频时一定要分频,不倍频时才允许不分频。参考文献

官方资料《TMS320x2833x, 2823x System Control and Interrupts》http://www.ti.com.cn/cn/lit/ug/sprufb0d/sprufb0d.pdf

- 顶

- 0

- 踩