这是翻译TI官方文档《KeyStone Architecture Universal Parallel Port (uPP)》SPRUHG9有关通用并行端口uPP的内容(除寄存器部分),寄存器部分大家可以自己看,现在手头上正在做uPP与FPGA的图像数据通信。等程序调通了,会贴出部分来分享一下开发与调试经验。

转载请注明出处:http://blog.csdn.net/hw5226349/ 1.1 外设的功能 通用并行端口外设(uPP)是一种专用数据线和最小的控制信号的多通道高速并行接口。设计用于每通道高达16bits数据宽度的ADCs、DACs传输,也可以用于FPAG和其他uPP外设。它可以工作在接收模式下,发射模式,或双工模式,其中,在它的各个通道操作相反的方向的传输。 1.2 功能 UPP外设提供一个高速并行数据总线的几个重要特点: •两个独立的通道带独立的数据总线 •通道可在相同或相反的方向同时工作

•I / O速度高达75 MHz的每个通道8-16位数据宽度

•内部DMA - 离开CPU EDMA免费

•简单的协议与几个控制引脚(配置:2-4每通道)

•单和双数据速率(使用一个或时钟信号的两个边)

•双倍数据速率规定的37.5 MHz的最大时钟速度

•多种数据打包格式9-15位数据宽度 •数据交错模式(单信道只)

请注意,图1-1显示了一个特定的配置:通道A接收通道B传输。但是,每个信道可以操作在任何一个方向。

单通道接收模式

单通道发送模式

数字回环模式(用于自测)

数据交叉单通道发送模式 图1-2,图1-3,图1-4,图通过UPP周边的各种配置1-5显示了简化的数据路径。注意,这些图是示例,并不代表所有可能的配置。

2.1 时钟产生与控制 uPP外设使用两个单独的时钟:模块时钟(控制其内部逻辑),以及运行在发送模式或者接口通道的发送时钟。这些时钟都是可配置的。不管是模块时钟,还是发送时钟都能可以比二分之一的设备CPU时钟速度更快。请参见特定器件的数据手册,了解更多信息。各通道的时钟引脚,I / O时钟,独立地得到根据它的操作方向。 2.1.1 发送模式(单倍速率)

I/O时钟计算公式:

固定除数限制了I / O时钟,最大速度是四分之一设备CPU时钟速度。 2.1.2 接收模式(单倍速率) 该通道需要一个外部时钟来驱动它的时钟引脚。输入时钟不可分频,其最大允许速度为四分之一(¼)CPU的时钟速度。 2.1.3 双倍速率 UPP外设支持两个I / O的时钟方案: •SDR - 单数据率 •DDR - 双倍数据速率 SDR时钟数据来自于I/O时钟的DATA引脚产生的上升沿或下降沿。 DDR,数据的时序来自于I / O时钟的上升和下降沿。然而,DDR模式用于发送和接收模式 ,规定了最低时钟是(¼)CPU时钟 。操作速度传输模式在每个数据速率的各种因子列于表2-1。 在接收模式下,一个通道的I / O时钟由外部源产生的,但以相同的速度规定范围。

2.2 信号描述 每个UPP通道都有自己的一套控制和数据信号。表2-2列出每一个信号,并简要介绍了它们的功能。信号名称与设备略有不同。用于精确信号名称的设备特定数据手册。2.5节阐述了uPP协议。

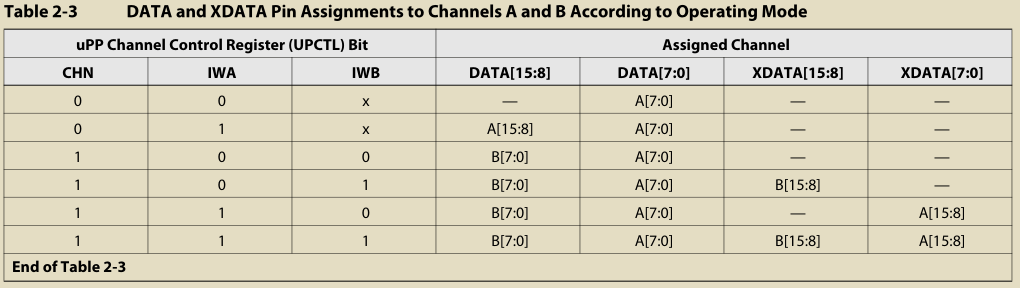

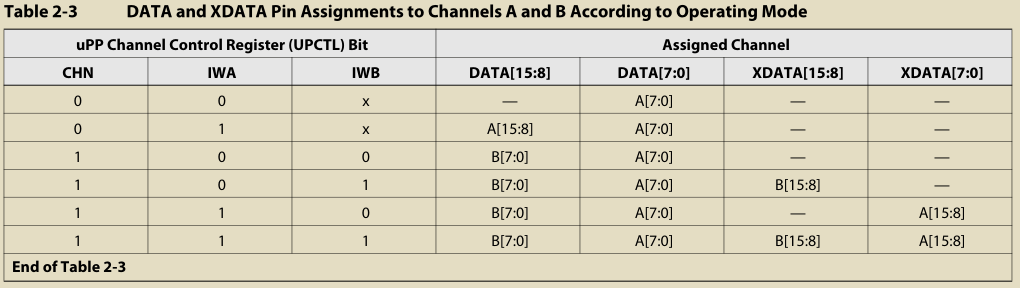

注意,DATA和XDATA引脚不是专用对单个I / O通道在相同的方式作为控制信号。由于实际原因,UPP数据引脚信道分配不是静态的。相反,使用由每个I / O信道的数据引脚(A,B)取决于UPP外设的操作模式。 表2-3总结了DATA和XDATA引脚分配给每个信道的各种操作模式,以及有关的寄存器的设置。有关这些引脚的更多信息,请参阅设备的数据手册。

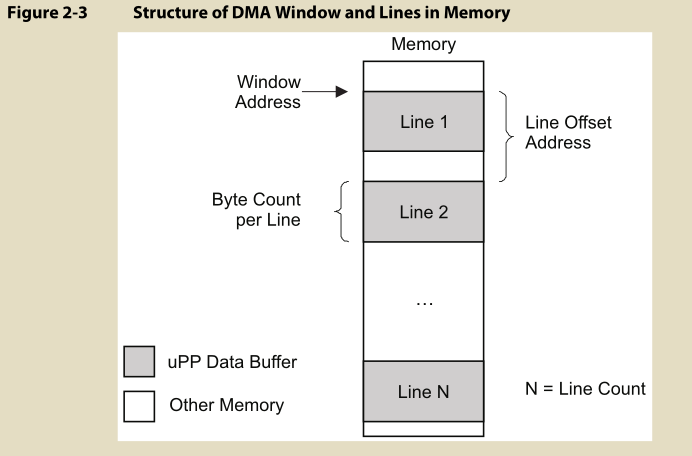

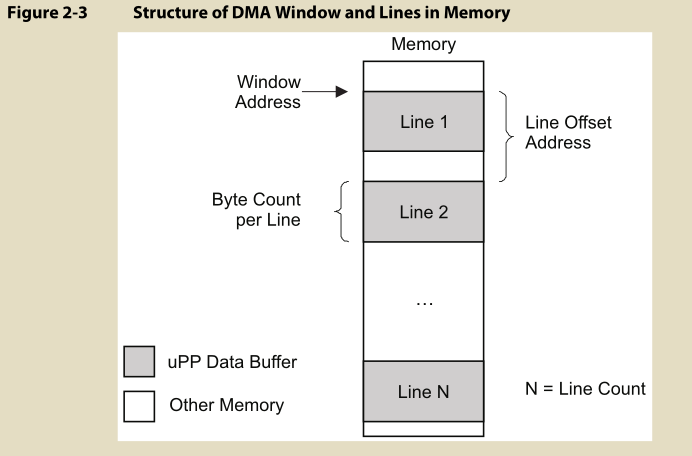

2.3 引脚复用 丰富的引脚复用是用来适应最大数量的外围功能的最小可能的封装。引脚复用是控制在设备复位和软件可编程寄存器设置的硬件配置相结合。如何确定引脚复用影响UPP周围,看到具体器件的数据手册。 2.4 内部DMA控制器描述 UPP外设包括一个内部的DMA控制器独立于任何设备的DMA,如EDMA。内部DMA控制器由两个DMA通道,I和Q,在所有工作模式下 ,移动数据to/from uPP的外设接口(I/O)的通道 。本节介绍了如何程序内部的DMA通道。 2.4.1 DMA编程概念 uPP内部的DMA控制器使用类似的EDMA进行2D传输的简化编程模型。 (See the KeyStone Architecture CommunicationsInfrastructure Digital Processor Enhanced Direct Memory Access (EDMA3) Controller User's Guide (SPRUGS5) for more information). 。每个DMA通道可以用四个参数进行配置:窗口地址,字节数,行数和行偏移地址。图2-3显示了这些参数定义的典型DMA窗口。 •窗口地址Window Address(UPxD0.ADDR)–在数据缓冲区中的第一个字节的内存地址。当uPP工作在接收模式中,DMA通道开始从这个地址 “写”并从uPP I/O通道需要输入的数据。当uPP工作在发射模式中,DMA通道开始从这个地址“读”并将数据传递到UPP I/O通道。窗口的地址可以驻留在任何可用的存储空间(包括EMIF),但它必须与一个64位的边界(即,低3位必须为0)。不对齐的地址都会自动调整到一个适当的对齐值时写的UPxD0。 •字节数Byte Count(UPxD1.BCNT) – 每Line的Byte数。字节数必须是偶数。 •行数Line Count(UPxD1.LNCNT) – 每Window的Line数。转移的总字节数等于二,其中每行的字节数是一个字节,而我是行计数。 •线偏移地址Line Offset Address(UPxD2.LNOFFSET) –偏移地址的第一个字节之间的连续线。线偏移地址不能超过65528(fff8h)字节,内存中必须对齐 64位的边界(即,低3位必须为0)。

该Line偏移地址的某些值对数据缓冲区的结构有特殊的影响: • Line Offset Address = Byte Count – 数据缓冲区是一个连续的块在内存中的大小等于(Line数)X(Byte数)。 • Line Offset Address = 0 – 数据缓冲区为一个Line的Byte数。如果I/O通道为传输模式,该Line被多次发送(Line Count)直到DMA传输完成。如果I/O通道为接收模式,这个缓冲区将被输入的数据反复覆盖。 在一个DMA传输的编程中,写DMA通道描述寄存器适当的域,UPIDn对应DMA 通道I,UPQDn对应DMA通道Q。如果相关的I/O通道的初始化和闲置,DMA传输和I/O事务立即开始。2.6节描述如何一步一步配置I/O DMA通道和开始一个uPP传递。 每个DMA通道前一个DMA传输(由第一个描述符)仍在运行时,允许第二个描述符去排队。UPxS2.PEND位指示可能有一个新的DMA参数集被写入到DMA描述寄存器。每个DMA通道可以有一个活动的传输和一个排队的传输。这允许每个I/O通道通过DMA传输边界进行不间断的、连续的事务。 内部DMA控制器不支持自动重装DMA传输描述符。每个描述符集必须通过软件明确地写到UPxDn寄存器。 所有uPP中断事件起源于内部DMA控制器。2.8节列出并解释了所有uPP中断事件。 内部DMA控制器总是在64字节的脉冲串中写入数据。但是,DMA读取操作具有可配置的脉冲串长度,这可能根据使用的uPP阈值配置寄存器(UPTCR)的RDSIZEI和RDSIZEQ位来设置每个通道。DMA通道等待,直到指定的字节数离开其内部缓冲区,在执行从内存中读取另一个脉冲串之前。 注意,UPTCR寄存器的TXSIZEA和TXSIZEB位不是DMA参数;相反,它们为uPP接口通道控制传输阈值。 2.4.2 数据交替模式(Data Interleave Mode) 数据交替模式是一种将两个DMA通道都映射到单个接口通道的特殊配置。由于uPP外设只有两个DMA通道,所以数据交替模式只能使用在uPP外设的单通道模式下。根据不同条件,数据交替模式有两种形式: 1.单倍速率交替--只用于发送 – UPCTL.CHN = 0 (single-channel mode) – UPCTL.DRA = 0 (single data rate) – UPCTL.MODE = 1 (transmit mode) – UPCTL.SDRTXIL = 1 (enable SDR transmit interleave) – UPCTL.DDRDEMUX = 0 (disable DDR interleave) 2.双倍速率交替--发送或接收 – UPCTL.CHN = 0 (single-channel mode)

– UPCTL.DRA = 1 (double data rate)

– UPCTL.MODE = 0 or 1 (receive or transmit mode; not duplex)

– UPCTL.SDRTXIL = 0 (disable SDR transmit interleave) – UPCTL.DDRDEMUX = 1 (enable DDR interleave) 2.1节中讲过SDR和DDR的区别描述。 在数据交替模式下,只有I/O通道A被用。单通道关联到两个数据缓冲区,被它们各自的DMA通道(I和Q)服务。 在SDR交替模式下,START信号被用作缓冲区选择线:START=1表示当前字来自DMA通道I;START=0表示当前字来自DMA通道Q。 在DDR交替模式下,由通道I开始从数据缓冲区轮流取出每个字:Channel I Word 0, Channel Q Word 0, Channel I Word 1, Channel Q Word 1, 等. 2.5节显示两种数据交错模式的信号图。 2.4.3 接口与DMA通道映射 通常情况下,DMA通道的I和Q各自被映射到接口通道A和B中。数据交错模式是个例外,因为它分配两个DMA通道服务接口通道A。表2-4概括了各种工作模式DMA通道映射。

2.5 协议描述 uPP外设由两个独立通道,每个具有其自己的数据线和控制信号。一个通道可以被配置去运行在发送模式或者接收模式,并使用uPP信道控制寄存器(UPCTL)去使用8或16数据线(8位或16位模式)。一个通道使用uPP接口配置寄存器(UPICR)也可以被配置为忽略某些控制信号。每个uPP默认为8位模式,并使用所有四个控制信号,除非另外进行配置。表2-5总结了在接收和发送模式所需要的基本操作的信号。下面的小节描述每个信号的作用。

2.5.1 DATA[7:0]信号 在8位模式中,DATA [7:0]包括该通道的整个数据总线。在16位模式,DATA [7:0]包括16位字的最低-显著位。该通道的数据宽度使用UPCTL的IWX位选中。 在发送模式中,这些管脚是输出 ,为通道的相应的DMA通道提供传输数据 。当通道空闲,他们的行为取决于UPICR的TRISx位。这些引脚可以配置为驱动空闲值(的TRISx=0,在UPP接口idle值寄存器(UPIVR)VALx域),或在一个高阻抗状态,空闲时(TRISx=1)。 在接收模式中,这些管脚是输入,提供数据到通道相应的DMA通道。 注意,DATA信号映射不同的DATA和XDATA管脚关于各种UPP配置。参见2.2节以获取更多信息。 2.5.2 DATA[15:8]信号 在8位模式中,DATA [15:8]不使用。在16位模式下,DATA [15:8]组成的16位字的最高8位。该通道的数据宽度使用UPCTL的IWX位选中。通一个道还可以被配置为使用其数据仅部分[15:8]引脚,它允许从8到16位的任何总的数据宽度。2.5.8节描述了数据格式和包装中的9位至15位的配置。 在使用时,方向和DATA的行为:在[158]发送和接收模式中的相同数据的方向和行为[7:0]。 注意,DATA信号映射不同的DATA和XDATA管脚关于各种UPP配置。参见2.2节以获取更多信息。 2.5.3 START信号 uPP发送器使起始信号时,它传送一个数据线的第一个字。 A线在通道的相关DMA通道来定义的;更多关于DMA编程概念,见2.4。START信号为高电平有效默认,但其极性由UPICR的STARTPOLx位控制。 在发射模式中,START是一个输出信号,并且总是驱动;在接收模式下,START是一个输入信号,并且可以使用在UPICR的STARTX位禁用。 当通道被配置为发送模式启用数据交织( 在UPCTL中SDRTXIL=1),START信号功能完全改变。 START信号,现在断言在由DMA通道一见2.5.7节这个另类的行为提供了每一个数据字。 2.5.4 ENABLE信号

2.5.5 WAIT信号 在数据传输过程中, WAIT信号允许接收者申请临时暂停。当接收者断言一个WAIT,发送者以暂停发送作为响应,直到WAIT释放。接收者忽略所有传入的数据,直到WAIT被释放。一旦WAIT被释放,发送者可以恢复对下一个字传输。如图2-5所示等待信号的时序。该WAIT信号是高电平有效默认,但其极性由UPICR所述WAITPOLx位控制。 在发送模式下,WAIT是(i)输入信号,UPICP的WAITx位可能被禁用;在接收模式下,WAIT是一个(o)输出信号。 2.5.6 CLOCK信号 2.5.7 信号时序图 在下面的图中,信号被标记(i)表明信号输入到uPP;(o)表明信号从uPP输出。从单个DMA通道的数据字被指定的Dx,而数据字必须来自特定DMA通道指定Ix或Qx去分别指示DMA通道I或Q。有关DMA通道和数据的交错模式的更多信息,请参见2.4节。 所有信号图绘制在默认状态信号极性。除了数据,所有信号都在uPP接口配置寄存器(UPICR)中独立配置。

注意:START断言--来自DMA通道I的每个数据字。 2.5.8 数据格式 uPP外设在UPP通道控制寄存器(UPCTL)的IWX和DPWx中设置,可支持使用8位到16位之间的任何数据字的宽度。对于8位操作,UPP读取/写入存储器的8位字;16位运算,UPP读取/写入内存的16位字。 对于N位操作(8

•右对齐,零扩展- 数据占用的N个LSB。在(16- N)的最高位被清0。

•右对齐,符号扩展- 数据占用的N个LSB。的(16- N)个MSB都相同的值(N- 1)位。

•左对齐,零填充- 数据占用N个MSB。在(16- N)LSB被清零。

表2-6列出了一些示例数据为N =12(即12位操作)。在发射模式中,传送的每个数据字从存储器打包版本是使用分配给UPP信道的所有16个数据引脚。在接收模式中,每个输入数据字(仅使用N个数据引脚)的填充版本存储在存储器中。

2.6 初始化和操作 uPP必须正确地初始化去确保操作成功。 注意 - 当初始化UPP外设的uPP接口配置寄存器(UPICR)编程必须使用一个单一的,32位的写。一个接一个的写UPICR字段可能会导致意想不到的结果。 本节提供一步步指导初始化和运行UPP外设的各种模式。这些说明给出假定该设备刚出来的上电复位(POR)状态。 步骤2-1 1.对适当的引脚进行复用设置。请参见特定器件的数据手册和/或引脚多路复用实用程序以获取更多信息。 2. 使能uPP外设的电源和时钟。请参见特定器件的数据手册。 3.将uPP外设控制寄存器(UPPCR)的SWRST位为1,使得uPP处于软件复位。 4.等待至少200器件时钟周期,然后清除SWRST位为0,以使模块脱离复位。 5.编程UPP配置寄存器:UPCTL,UPICR,UPIVR,UPTCR和UPDLB。每个寄存器的基本功能是简介如下;有关详细信息,请参阅第3节。 5a UPCTL- 发送/接收选择(见表2-7),数据宽度,数据格式,数据速率,数据交织使能 5b UPICR- 信号使能,信号反相,时钟分频(仅发送模式) 5c UPIVR- 空闲值(仅发送模式) 5d UPTCR- I / O传输阈值(仅发送模式),DMA读脉冲串大小 5e UPDLB- 数字环回(见表2-7) 6.设置uPP中断使能设置寄存器(UPIES)中断产生所需的事件。注册一个中断服务例程(ISR)如果需要的话;否则,轮询是必需的。 7.设置uPP外设控制寄存器(UPPCR)的EN位为1,打开uPP外设。 8.为uPP使用去分配和/或初始化数据缓冲器。 9.设置uPP DMA通道描述符寄存器去使用带有它们第一个传输的DMA通道:UPID0-2和/或UPQD0-2。 10.留意中断事件。根据需要重新编程DMA(检查UPP DMA通道状态寄存器中的PEND位(UPxS2)为0)。 10a 如果轮询,检查UPIES。读一位为1表示相应的事件已经发生. 相应位写1来清除。 10b 如果使用ISR,检查UPIES的ISR中。根据伪代码在第2.6.4节结构的ISR。 2.6.2 配置示例 uPP外设是灵活的,有多个正交配置选择。表2-7总结了选择所述模块的基本操作模式。 注意 - 数字回路(DLB)模式是一种配置,uPP内部外设路线数据和控制信号从一个通道到另一个通道。DLB只能当外设被配置在双工模式时被用(即,UPCTL.MODE=2h或3h)。DLB是用于调试目的主要是有用的,并且需要信道之间没有物理连接。标准UPP引脚多路复用必须应用,即使管脚不被使用。

除了表2-7中,有几个选择,(每通道)进行:

•数据宽度 - 8位,9位至16位 •数据包装 - 9位到15位数据宽度 •数据速率 - 单倍,双倍 •数据交替 -只有单通道模式 •时钟分频 - 只发送模式 •单独控制信号使 •单独控制信号的极性 •空闲价值 - 只发送模式 •发送阈值 - 只发送模式 •DMA读脉冲串大小 表2-8列出了一个例子设置UPP参数为双工模式0。此配置会将UPP外设设置为通道A接收通道B发送的双工模式。每个信道使用16位接口与不同的数据格式。

2.6.3 系统调优技巧 uPP外设可以高速运行,以非常高的速度传输数据。当工作接近其上限的uPP,调整某些参数可以帮助减少错误的发生率和发生服务uPP数据的软件开销。表2-9列出了几个参数,可以在系统优化非常有用。一个参数被定义为一个“粗”调节,如果改变参数直接改变外设吞吐量。“精”调节不改变外设的吞吐量,但它确实影响到一般的系统性能。

2.6.4 中断服务程序示例 以下伪代码用于写入uPP中断服务路由(ISR)函数的模板。请注意,UPP组合所有事件到单个CPU中断,同时如果前面的中断仍然没有从ISR返回,一个新的中断将不调用ISR。为了允许进一步调用ISR,结束中断UPP寄存器(UPEOI)必须写入零值。因此,ISR应检查多个事件,在处理每一个事件后应继续复查,直到没有更多的事件被发现。然后,它在返回之前必须写UPEOI=0。 [cpp] view plain copy

2.7 复位注意事项 以下各节讨论软硬件复位的行为。 2.7.1 软件复位 软件复位清零uPP内部状态机,但不重置的UPP寄存器的内容。下面的过程进行的UPP外设的软件复位。 步骤2-2: 1.向uPP外设控制寄存器(UPPCR)EN位写0(禁用uPP)。 2.查看UPPCR中DB位为活动;等到DMA控制器处于非活动状态/空闲。 3.编写UPPCR中SWRST位为1(地方UPP软件复位)。 4.编写UPPCR中SWRST位为0(UPP带来了软件复位)。 2.7.2 硬件复位 当处理器复位管脚有效,整个处理器复位,并保持复位状态,直到RESET引脚释放。作为器件复位的一部分,UPP状态机复位,UPP寄存器被强制为默认状态(见第3节)。 2.8 中断支持 UPP外设生成八个中断事件,都依赖于内部的DMA通道I和Q。UPP外设自动将所有中断事件到一个单一芯片级的中断。个别事件可能使用UPP中断使能设置寄存器(UPIES)和禁用使用UPP中断使能清除寄存器(UPIEC)启用。只有启用的事件产生中断和中断使能状态寄存器(UPIER)断言位。禁用事件不会产生中断,但做断言中断原始状态寄存器(UPISR)位。 一个中断服务例程(ISR)可以被分配给处理UPP芯片级使用的中断控制器模块中断。如果发生在靠近UPP事件彼此,单个CPU的中断(并在ISR单个调用)可以代表多个中断事件。因此,UPP ISR必须符合一定的结构要求: •在ISR必须能够返回前处理多个事件。 •在ISR必须处理后续事件,在事件发生后,但它返回之前,调用它。 •在ISR必须写00h到结束中断UPP寄存器(UPEOI)返回之前。这使得后续UPP事件产生CPU中断。 2.6节提供了展示这些要求的样品ISR。 2.8.1 Line结束事件(EOL)

2.8.2 Window结束事件(EOW)

2.8.3 内部总线错误事件(ERR)

2.8.4 欠载或溢出事件(UOR) 2.8.5 DMA编程错误事件(DPE) 2.9 电源管理 该UPP外设在非活动期间可以放置在降低功耗的模式以节省电源。有关电源管理的信息,请参阅该设备的数据手册。

2.10 仿真注意事项 如果满足三个条件,UPP外设停止运行: •外设禁用–UPP外设控制寄存器(UPPCR)中EN位为0。 •时钟停止–UPP承认从设备电源管理模块的时钟停止请求。 •仿真暂停 - JTAG仿真器停止芯片,当UPPCR中FREE = 0,SOFT = 1。 对于除FREE和SOFT的其他设置,在仿真停止器件uPP外设将继续运行。 当UPP遇到了停止状态,在停止前,完成当前DMA脉冲串事务(如果有效)。 配置为发送模式的I/ O通道,立即置位其引脚为高阻抗状态,并保留其内部状态机的状态。除非某些复位事件发生时(参见2.7节),该通道可以恢复它离开的位置,当停止状态被清除。 一个I / O通道配置在接收模式立即断言其WAIT信号(见第2.5.5节),并捕获一个附加数据字。只要停止条件仍然存在,而且输入的数据字都被忽略。 2.11 发送和接收FIFOs 每个UPP外设I/ O通道有一个512字节的FIFO。在接收模式中,FIFO被分成8个64字节的块。在发送模式中,FIFO被分成可以设置为64,128,或256字节的块,由TXSIZEA或TXSIZEB字段在UPP阈配置寄存器(UPTCR)配置。传输不会开始直到通道已装载足够的数据来填充至少一个完整的FIFO块。 内部DMA通道还可以使用UPTCR中RDSIZEI或RDSIZEQ字段配置,去使用64,128或256个字节的读取阈值。DMA写操作的阈值固定为64个字节。

转载请注明出处:http://blog.csdn.net/hw5226349/ 1.1 外设的功能 通用并行端口外设(uPP)是一种专用数据线和最小的控制信号的多通道高速并行接口。设计用于每通道高达16bits数据宽度的ADCs、DACs传输,也可以用于FPAG和其他uPP外设。它可以工作在接收模式下,发射模式,或双工模式,其中,在它的各个通道操作相反的方向的传输。 1.2 功能 UPP外设提供一个高速并行数据总线的几个重要特点: •两个独立的通道带独立的数据总线 •通道可在相同或相反的方向同时工作

•I / O速度高达75 MHz的每个通道8-16位数据宽度

•内部DMA - 离开CPU EDMA免费

•简单的协议与几个控制引脚(配置:2-4每通道)

•单和双数据速率(使用一个或时钟信号的两个边)

•双倍数据速率规定的37.5 MHz的最大时钟速度

•多种数据打包格式9-15位数据宽度 •数据交错模式(单信道只)

请注意,图1-1显示了一个特定的配置:通道A接收通道B传输。但是,每个信道可以操作在任何一个方向。

单通道接收模式

单通道发送模式

数字回环模式(用于自测)

数据交叉单通道发送模式 图1-2,图1-3,图1-4,图通过UPP周边的各种配置1-5显示了简化的数据路径。注意,这些图是示例,并不代表所有可能的配置。

2.1 时钟产生与控制 uPP外设使用两个单独的时钟:模块时钟(控制其内部逻辑),以及运行在发送模式或者接口通道的发送时钟。这些时钟都是可配置的。不管是模块时钟,还是发送时钟都能可以比二分之一的设备CPU时钟速度更快。请参见特定器件的数据手册,了解更多信息。各通道的时钟引脚,I / O时钟,独立地得到根据它的操作方向。 2.1.1 发送模式(单倍速率)

I/O时钟计算公式:

固定除数限制了I / O时钟,最大速度是四分之一设备CPU时钟速度。 2.1.2 接收模式(单倍速率) 该通道需要一个外部时钟来驱动它的时钟引脚。输入时钟不可分频,其最大允许速度为四分之一(¼)CPU的时钟速度。 2.1.3 双倍速率 UPP外设支持两个I / O的时钟方案: •SDR - 单数据率 •DDR - 双倍数据速率 SDR时钟数据来自于I/O时钟的DATA引脚产生的上升沿或下降沿。 DDR,数据的时序来自于I / O时钟的上升和下降沿。然而,DDR模式用于发送和接收模式 ,规定了最低时钟是(¼)CPU时钟 。操作速度传输模式在每个数据速率的各种因子列于表2-1。 在接收模式下,一个通道的I / O时钟由外部源产生的,但以相同的速度规定范围。

2.2 信号描述 每个UPP通道都有自己的一套控制和数据信号。表2-2列出每一个信号,并简要介绍了它们的功能。信号名称与设备略有不同。用于精确信号名称的设备特定数据手册。2.5节阐述了uPP协议。

注意,DATA和XDATA引脚不是专用对单个I / O通道在相同的方式作为控制信号。由于实际原因,UPP数据引脚信道分配不是静态的。相反,使用由每个I / O信道的数据引脚(A,B)取决于UPP外设的操作模式。 表2-3总结了DATA和XDATA引脚分配给每个信道的各种操作模式,以及有关的寄存器的设置。有关这些引脚的更多信息,请参阅设备的数据手册。

2.3 引脚复用 丰富的引脚复用是用来适应最大数量的外围功能的最小可能的封装。引脚复用是控制在设备复位和软件可编程寄存器设置的硬件配置相结合。如何确定引脚复用影响UPP周围,看到具体器件的数据手册。 2.4 内部DMA控制器描述 UPP外设包括一个内部的DMA控制器独立于任何设备的DMA,如EDMA。内部DMA控制器由两个DMA通道,I和Q,在所有工作模式下 ,移动数据to/from uPP的外设接口(I/O)的通道 。本节介绍了如何程序内部的DMA通道。 2.4.1 DMA编程概念 uPP内部的DMA控制器使用类似的EDMA进行2D传输的简化编程模型。 (See the KeyStone Architecture CommunicationsInfrastructure Digital Processor Enhanced Direct Memory Access (EDMA3) Controller User's Guide (SPRUGS5) for more information). 。每个DMA通道可以用四个参数进行配置:窗口地址,字节数,行数和行偏移地址。图2-3显示了这些参数定义的典型DMA窗口。 •窗口地址Window Address(UPxD0.ADDR)–在数据缓冲区中的第一个字节的内存地址。当uPP工作在接收模式中,DMA通道开始从这个地址 “写”并从uPP I/O通道需要输入的数据。当uPP工作在发射模式中,DMA通道开始从这个地址“读”并将数据传递到UPP I/O通道。窗口的地址可以驻留在任何可用的存储空间(包括EMIF),但它必须与一个64位的边界(即,低3位必须为0)。不对齐的地址都会自动调整到一个适当的对齐值时写的UPxD0。 •字节数Byte Count(UPxD1.BCNT) – 每Line的Byte数。字节数必须是偶数。 •行数Line Count(UPxD1.LNCNT) – 每Window的Line数。转移的总字节数等于二,其中每行的字节数是一个字节,而我是行计数。 •线偏移地址Line Offset Address(UPxD2.LNOFFSET) –偏移地址的第一个字节之间的连续线。线偏移地址不能超过65528(fff8h)字节,内存中必须对齐 64位的边界(即,低3位必须为0)。

该Line偏移地址的某些值对数据缓冲区的结构有特殊的影响: • Line Offset Address = Byte Count – 数据缓冲区是一个连续的块在内存中的大小等于(Line数)X(Byte数)。 • Line Offset Address = 0 – 数据缓冲区为一个Line的Byte数。如果I/O通道为传输模式,该Line被多次发送(Line Count)直到DMA传输完成。如果I/O通道为接收模式,这个缓冲区将被输入的数据反复覆盖。 在一个DMA传输的编程中,写DMA通道描述寄存器适当的域,UPIDn对应DMA 通道I,UPQDn对应DMA通道Q。如果相关的I/O通道的初始化和闲置,DMA传输和I/O事务立即开始。2.6节描述如何一步一步配置I/O DMA通道和开始一个uPP传递。 每个DMA通道前一个DMA传输(由第一个描述符)仍在运行时,允许第二个描述符去排队。UPxS2.PEND位指示可能有一个新的DMA参数集被写入到DMA描述寄存器。每个DMA通道可以有一个活动的传输和一个排队的传输。这允许每个I/O通道通过DMA传输边界进行不间断的、连续的事务。 内部DMA控制器不支持自动重装DMA传输描述符。每个描述符集必须通过软件明确地写到UPxDn寄存器。 所有uPP中断事件起源于内部DMA控制器。2.8节列出并解释了所有uPP中断事件。 内部DMA控制器总是在64字节的脉冲串中写入数据。但是,DMA读取操作具有可配置的脉冲串长度,这可能根据使用的uPP阈值配置寄存器(UPTCR)的RDSIZEI和RDSIZEQ位来设置每个通道。DMA通道等待,直到指定的字节数离开其内部缓冲区,在执行从内存中读取另一个脉冲串之前。 注意,UPTCR寄存器的TXSIZEA和TXSIZEB位不是DMA参数;相反,它们为uPP接口通道控制传输阈值。 2.4.2 数据交替模式(Data Interleave Mode) 数据交替模式是一种将两个DMA通道都映射到单个接口通道的特殊配置。由于uPP外设只有两个DMA通道,所以数据交替模式只能使用在uPP外设的单通道模式下。根据不同条件,数据交替模式有两种形式: 1.单倍速率交替--只用于发送 – UPCTL.CHN = 0 (single-channel mode) – UPCTL.DRA = 0 (single data rate) – UPCTL.MODE = 1 (transmit mode) – UPCTL.SDRTXIL = 1 (enable SDR transmit interleave) – UPCTL.DDRDEMUX = 0 (disable DDR interleave) 2.双倍速率交替--发送或接收 – UPCTL.CHN = 0 (single-channel mode)

– UPCTL.DRA = 1 (double data rate)

– UPCTL.MODE = 0 or 1 (receive or transmit mode; not duplex)

– UPCTL.SDRTXIL = 0 (disable SDR transmit interleave) – UPCTL.DDRDEMUX = 1 (enable DDR interleave) 2.1节中讲过SDR和DDR的区别描述。 在数据交替模式下,只有I/O通道A被用。单通道关联到两个数据缓冲区,被它们各自的DMA通道(I和Q)服务。 在SDR交替模式下,START信号被用作缓冲区选择线:START=1表示当前字来自DMA通道I;START=0表示当前字来自DMA通道Q。 在DDR交替模式下,由通道I开始从数据缓冲区轮流取出每个字:Channel I Word 0, Channel Q Word 0, Channel I Word 1, Channel Q Word 1, 等. 2.5节显示两种数据交错模式的信号图。 2.4.3 接口与DMA通道映射 通常情况下,DMA通道的I和Q各自被映射到接口通道A和B中。数据交错模式是个例外,因为它分配两个DMA通道服务接口通道A。表2-4概括了各种工作模式DMA通道映射。

2.5 协议描述 uPP外设由两个独立通道,每个具有其自己的数据线和控制信号。一个通道可以被配置去运行在发送模式或者接收模式,并使用uPP信道控制寄存器(UPCTL)去使用8或16数据线(8位或16位模式)。一个通道使用uPP接口配置寄存器(UPICR)也可以被配置为忽略某些控制信号。每个uPP默认为8位模式,并使用所有四个控制信号,除非另外进行配置。表2-5总结了在接收和发送模式所需要的基本操作的信号。下面的小节描述每个信号的作用。

2.5.1 DATA[7:0]信号 在8位模式中,DATA [7:0]包括该通道的整个数据总线。在16位模式,DATA [7:0]包括16位字的最低-显著位。该通道的数据宽度使用UPCTL的IWX位选中。 在发送模式中,这些管脚是输出 ,为通道的相应的DMA通道提供传输数据 。当通道空闲,他们的行为取决于UPICR的TRISx位。这些引脚可以配置为驱动空闲值(的TRISx=0,在UPP接口idle值寄存器(UPIVR)VALx域),或在一个高阻抗状态,空闲时(TRISx=1)。 在接收模式中,这些管脚是输入,提供数据到通道相应的DMA通道。 注意,DATA信号映射不同的DATA和XDATA管脚关于各种UPP配置。参见2.2节以获取更多信息。 2.5.2 DATA[15:8]信号 在8位模式中,DATA [15:8]不使用。在16位模式下,DATA [15:8]组成的16位字的最高8位。该通道的数据宽度使用UPCTL的IWX位选中。通一个道还可以被配置为使用其数据仅部分[15:8]引脚,它允许从8到16位的任何总的数据宽度。2.5.8节描述了数据格式和包装中的9位至15位的配置。 在使用时,方向和DATA的行为:在[158]发送和接收模式中的相同数据的方向和行为[7:0]。 注意,DATA信号映射不同的DATA和XDATA管脚关于各种UPP配置。参见2.2节以获取更多信息。 2.5.3 START信号 uPP发送器使起始信号时,它传送一个数据线的第一个字。 A线在通道的相关DMA通道来定义的;更多关于DMA编程概念,见2.4。START信号为高电平有效默认,但其极性由UPICR的STARTPOLx位控制。 在发射模式中,START是一个输出信号,并且总是驱动;在接收模式下,START是一个输入信号,并且可以使用在UPICR的STARTX位禁用。 当通道被配置为发送模式启用数据交织( 在UPCTL中SDRTXIL=1),START信号功能完全改变。 START信号,现在断言在由DMA通道一见2.5.7节这个另类的行为提供了每一个数据字。 2.5.4 ENABLE信号

2.5.5 WAIT信号 在数据传输过程中, WAIT信号允许接收者申请临时暂停。当接收者断言一个WAIT,发送者以暂停发送作为响应,直到WAIT释放。接收者忽略所有传入的数据,直到WAIT被释放。一旦WAIT被释放,发送者可以恢复对下一个字传输。如图2-5所示等待信号的时序。该WAIT信号是高电平有效默认,但其极性由UPICR所述WAITPOLx位控制。 在发送模式下,WAIT是(i)输入信号,UPICP的WAITx位可能被禁用;在接收模式下,WAIT是一个(o)输出信号。 2.5.6 CLOCK信号 2.5.7 信号时序图 在下面的图中,信号被标记(i)表明信号输入到uPP;(o)表明信号从uPP输出。从单个DMA通道的数据字被指定的Dx,而数据字必须来自特定DMA通道指定Ix或Qx去分别指示DMA通道I或Q。有关DMA通道和数据的交错模式的更多信息,请参见2.4节。 所有信号图绘制在默认状态信号极性。除了数据,所有信号都在uPP接口配置寄存器(UPICR)中独立配置。

注意:START断言--来自DMA通道I的每个数据字。 2.5.8 数据格式 uPP外设在UPP通道控制寄存器(UPCTL)的IWX和DPWx中设置,可支持使用8位到16位之间的任何数据字的宽度。对于8位操作,UPP读取/写入存储器的8位字;16位运算,UPP读取/写入内存的16位字。 对于N位操作(8

2.6 初始化和操作 uPP必须正确地初始化去确保操作成功。 注意 - 当初始化UPP外设的uPP接口配置寄存器(UPICR)编程必须使用一个单一的,32位的写。一个接一个的写UPICR字段可能会导致意想不到的结果。 本节提供一步步指导初始化和运行UPP外设的各种模式。这些说明给出假定该设备刚出来的上电复位(POR)状态。 步骤2-1 1.对适当的引脚进行复用设置。请参见特定器件的数据手册和/或引脚多路复用实用程序以获取更多信息。 2. 使能uPP外设的电源和时钟。请参见特定器件的数据手册。 3.将uPP外设控制寄存器(UPPCR)的SWRST位为1,使得uPP处于软件复位。 4.等待至少200器件时钟周期,然后清除SWRST位为0,以使模块脱离复位。 5.编程UPP配置寄存器:UPCTL,UPICR,UPIVR,UPTCR和UPDLB。每个寄存器的基本功能是简介如下;有关详细信息,请参阅第3节。 5a UPCTL- 发送/接收选择(见表2-7),数据宽度,数据格式,数据速率,数据交织使能 5b UPICR- 信号使能,信号反相,时钟分频(仅发送模式) 5c UPIVR- 空闲值(仅发送模式) 5d UPTCR- I / O传输阈值(仅发送模式),DMA读脉冲串大小 5e UPDLB- 数字环回(见表2-7) 6.设置uPP中断使能设置寄存器(UPIES)中断产生所需的事件。注册一个中断服务例程(ISR)如果需要的话;否则,轮询是必需的。 7.设置uPP外设控制寄存器(UPPCR)的EN位为1,打开uPP外设。 8.为uPP使用去分配和/或初始化数据缓冲器。 9.设置uPP DMA通道描述符寄存器去使用带有它们第一个传输的DMA通道:UPID0-2和/或UPQD0-2。 10.留意中断事件。根据需要重新编程DMA(检查UPP DMA通道状态寄存器中的PEND位(UPxS2)为0)。 10a 如果轮询,检查UPIES。读一位为1表示相应的事件已经发生. 相应位写1来清除。 10b 如果使用ISR,检查UPIES的ISR中。根据伪代码在第2.6.4节结构的ISR。 2.6.2 配置示例 uPP外设是灵活的,有多个正交配置选择。表2-7总结了选择所述模块的基本操作模式。 注意 - 数字回路(DLB)模式是一种配置,uPP内部外设路线数据和控制信号从一个通道到另一个通道。DLB只能当外设被配置在双工模式时被用(即,UPCTL.MODE=2h或3h)。DLB是用于调试目的主要是有用的,并且需要信道之间没有物理连接。标准UPP引脚多路复用必须应用,即使管脚不被使用。

除了表2-7中,有几个选择,(每通道)进行:

•数据宽度 - 8位,9位至16位 •数据包装 - 9位到15位数据宽度 •数据速率 - 单倍,双倍 •数据交替 -只有单通道模式 •时钟分频 - 只发送模式 •单独控制信号使 •单独控制信号的极性 •空闲价值 - 只发送模式 •发送阈值 - 只发送模式 •DMA读脉冲串大小 表2-8列出了一个例子设置UPP参数为双工模式0。此配置会将UPP外设设置为通道A接收通道B发送的双工模式。每个信道使用16位接口与不同的数据格式。

2.6.3 系统调优技巧 uPP外设可以高速运行,以非常高的速度传输数据。当工作接近其上限的uPP,调整某些参数可以帮助减少错误的发生率和发生服务uPP数据的软件开销。表2-9列出了几个参数,可以在系统优化非常有用。一个参数被定义为一个“粗”调节,如果改变参数直接改变外设吞吐量。“精”调节不改变外设的吞吐量,但它确实影响到一般的系统性能。

2.6.4 中断服务程序示例 以下伪代码用于写入uPP中断服务路由(ISR)函数的模板。请注意,UPP组合所有事件到单个CPU中断,同时如果前面的中断仍然没有从ISR返回,一个新的中断将不调用ISR。为了允许进一步调用ISR,结束中断UPP寄存器(UPEOI)必须写入零值。因此,ISR应检查多个事件,在处理每一个事件后应继续复查,直到没有更多的事件被发现。然后,它在返回之前必须写UPEOI=0。 [cpp] view plain copy

- Function upp_isr

- {

- interrupt_status = UPIER

- while (interrupt_status != 0)

- {

- if (interrupt_status.EOLI)

- {

- UPIER.EOLI = 1 // clear EOLI

- // Handle EOLI...

- }

- if (interrupt_status.EOWI)

- {

- UPIER.EOWI = 1 // clear EOWI

- // Handle EOWI...

- }

- if (interrupt_status.ERRI)

- {

- UPIER.ERRI = 1 // clear ERRI

- // Handle ERRI...

- }

- if (interrupt_status.UORI)

- {

- UPIER.UORI = 1 // clear UORI

- // Handle UORI...

- }

- if (interrupt_status.DPEI)

- {

- UPIER.DPEI = 1 // clear DPEI

- // Handle DPEI...

- }

- if (interrupt_status.EOLQ)

- {

- UPIER.EOLQ = 1 // clear EOLQ

- // Handle EOLQ...

- }

- if (interrupt_status.EOWQ)

- {

- UPIER.EOWQ = 1 // clear EOWQ

- // Handle EOWQ...

- }

- if (interrupt_status.ERRQ)

- {

- UPIER.ERRQ = 1 // clear ERRQ

- // Handle ERRQ...

- }

- if (interrupt_status.UORQ)

- {

- UPIER.UORQ = 1 // clear UORQ

- // Handle UORQ...

- }

- if (interrupt_status.DPEQ)

- {

- UPIER.DPEQ = 1 // clear DPEQ

- // Handle DPEQ...

- }

- // loop again if any interrupts are left

- interrupt_status = UPIER

- } // end of while

- // write end of interrupt vector to allow future calls

- UPEOI = 0

- } // end of function

2.7 复位注意事项 以下各节讨论软硬件复位的行为。 2.7.1 软件复位 软件复位清零uPP内部状态机,但不重置的UPP寄存器的内容。下面的过程进行的UPP外设的软件复位。 步骤2-2: 1.向uPP外设控制寄存器(UPPCR)EN位写0(禁用uPP)。 2.查看UPPCR中DB位为活动;等到DMA控制器处于非活动状态/空闲。 3.编写UPPCR中SWRST位为1(地方UPP软件复位)。 4.编写UPPCR中SWRST位为0(UPP带来了软件复位)。 2.7.2 硬件复位 当处理器复位管脚有效,整个处理器复位,并保持复位状态,直到RESET引脚释放。作为器件复位的一部分,UPP状态机复位,UPP寄存器被强制为默认状态(见第3节)。 2.8 中断支持 UPP外设生成八个中断事件,都依赖于内部的DMA通道I和Q。UPP外设自动将所有中断事件到一个单一芯片级的中断。个别事件可能使用UPP中断使能设置寄存器(UPIES)和禁用使用UPP中断使能清除寄存器(UPIEC)启用。只有启用的事件产生中断和中断使能状态寄存器(UPIER)断言位。禁用事件不会产生中断,但做断言中断原始状态寄存器(UPISR)位。 一个中断服务例程(ISR)可以被分配给处理UPP芯片级使用的中断控制器模块中断。如果发生在靠近UPP事件彼此,单个CPU的中断(并在ISR单个调用)可以代表多个中断事件。因此,UPP ISR必须符合一定的结构要求: •在ISR必须能够返回前处理多个事件。 •在ISR必须处理后续事件,在事件发生后,但它返回之前,调用它。 •在ISR必须写00h到结束中断UPP寄存器(UPEOI)返回之前。这使得后续UPP事件产生CPU中断。 2.6节提供了展示这些要求的样品ISR。 2.8.1 Line结束事件(EOL)

2.8.2 Window结束事件(EOW)

2.8.3 内部总线错误事件(ERR)

2.8.4 欠载或溢出事件(UOR) 2.8.5 DMA编程错误事件(DPE) 2.9 电源管理 该UPP外设在非活动期间可以放置在降低功耗的模式以节省电源。有关电源管理的信息,请参阅该设备的数据手册。

2.10 仿真注意事项 如果满足三个条件,UPP外设停止运行: •外设禁用–UPP外设控制寄存器(UPPCR)中EN位为0。 •时钟停止–UPP承认从设备电源管理模块的时钟停止请求。 •仿真暂停 - JTAG仿真器停止芯片,当UPPCR中FREE = 0,SOFT = 1。 对于除FREE和SOFT的其他设置,在仿真停止器件uPP外设将继续运行。 当UPP遇到了停止状态,在停止前,完成当前DMA脉冲串事务(如果有效)。 配置为发送模式的I/ O通道,立即置位其引脚为高阻抗状态,并保留其内部状态机的状态。除非某些复位事件发生时(参见2.7节),该通道可以恢复它离开的位置,当停止状态被清除。 一个I / O通道配置在接收模式立即断言其WAIT信号(见第2.5.5节),并捕获一个附加数据字。只要停止条件仍然存在,而且输入的数据字都被忽略。 2.11 发送和接收FIFOs 每个UPP外设I/ O通道有一个512字节的FIFO。在接收模式中,FIFO被分成8个64字节的块。在发送模式中,FIFO被分成可以设置为64,128,或256字节的块,由TXSIZEA或TXSIZEB字段在UPP阈配置寄存器(UPTCR)配置。传输不会开始直到通道已装载足够的数据来填充至少一个完整的FIFO块。 内部DMA通道还可以使用UPTCR中RDSIZEI或RDSIZEQ字段配置,去使用64,128或256个字节的读取阈值。DMA写操作的阈值固定为64个字节。