Hexagon DSP所提供的指令集

本文将介绍Hexagon DSP开发中需要使用指令的语法,类,包以及并行的各种形式,我们将以六个角度来探究Hexagon DSP指令。

l 指令语法

l 指令类

l 指令包

l 指令内联

l 复合指令集

l 多普勒指令集

指令语法

大多数的处理器指令具有如下的语法结构:

Dest = instr_name(source1,source2,…)[:option1][:option2]…

右边定义的变量被右边的值所赋值,例如:

R2 = add(R3,R1) //AddR3 and R1, assign result to R2

下图列出了在Hexagon处理器指令集中常用的符号

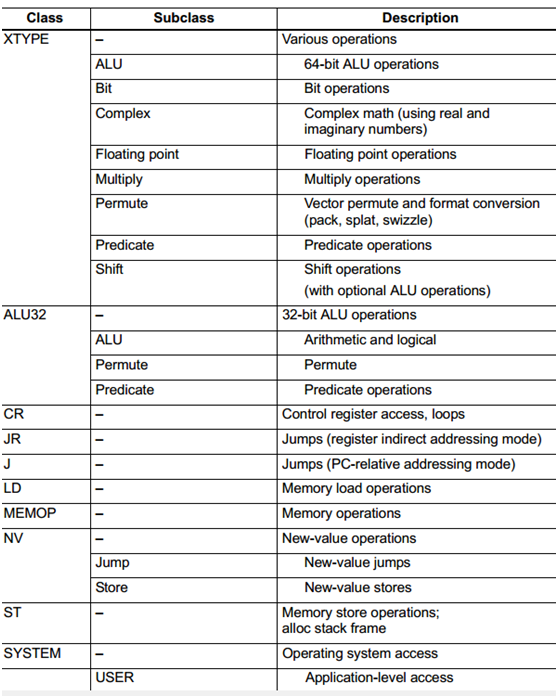

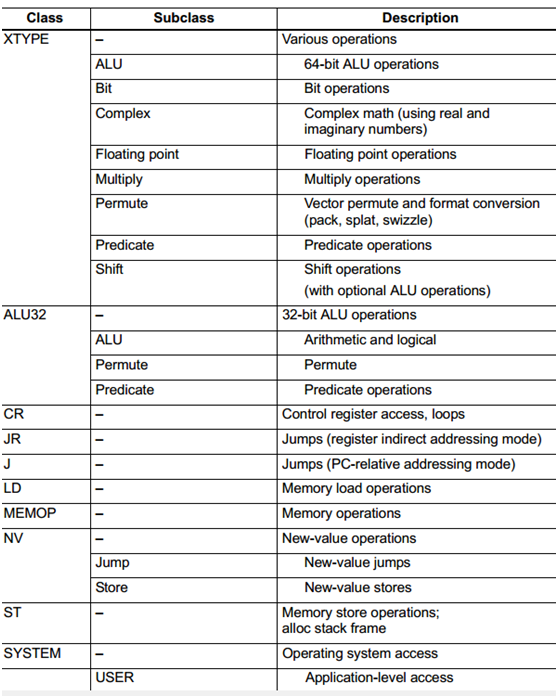

指令类 Hexagon处理器指令集被划分成了特定的指令类。类的不同决定了指令可以被如何以并行方式结合。 指令类与指令的类型相符合。例如ALU32类包含操作32位操作数的ALU指令。 下图列出了指令类以及子类:

指令包 指令可以被并在一起组成单独的指令包,指令包可以被并行的执行。指令包可以包含1,2,3,4个指令。 指令包必须在软件中清楚的定义。指令包通过使用花括号包含并以汇编语言表示,例如: { R0=R1; R2=R3; } 各种各样的规则以及限制规定了什么样类型的指令可以被组合,以及这些组合如何在包中出现。指令包的格式受到如下的具体限制: l 资源限制决定了包中可以出现多少种特殊类型的指令。Hexagon处理器具有定点计算的执行单元:每个指令在每个特定的单元上执行,每个单元一次只可以执行一个指令。因此,打比方来说,因为Hexagon处理器包含了两个load单元,一个包含了三个load命令的指令就是非法的。详细细节会在下一篇给出 l 组合限制是一组适用于以上并优于资源限制的规则。详细细节会在下一篇给出 l 独立限制保证了不会有先写后写磁头的风险。详细细节会在下一篇给出 l 顺序限制表明了指令包中的指令顺序。详细细节会在下一篇给出 l 对齐限制表明了内存中包的位置。这些规则的详细细节会在下一篇给出 注意:单独的指令在Hexagon处理器中被认为是包含了一个指令的指令包 包执行语义 包被定义为具有并行执行语义。也就是说,指令包的执行行为被定义如下: l 首先,包中所有的指令并行的读他们的源寄存器 l 其次,包中所有的指令都会执行 l 最后,包中所有的指令将会并行的写入其目标寄存器 例如,如下的指令: { R2= R3 ; R3 = R2 ; } 在第一阶段,寄存器R3和R2从寄存器文件中读取出来。接着,在执行完后,R2被写回R3的旧值,而R3的值被写回R2的旧值。因此,R2和R3的值被交换了。 序列语义 任何长度的包都可以被在代码中自由的混合。包可以被认为是一个原子单位:本质上来说,一个单独的大“指令”。从程序角度来说,一个包或者完全执行,要么不会执行;绝对不会部分执行。例如,如果一个包导致了内存异常,那么这个异常点在包之前就会被报错。 一个包含了多个导入或存储的指令可能会需要外部系统的服务。例如,假设一个需要执行两个导入操作同时未击中缓存的情况。这个包需要主存系统所提供的数据: l 从主存系统角度来说,这两个要求是串行执行的。 l 从程序角度来说,两个导入指令必须在包可以执行前完成 因此,从程序角度来说这个包是原子性的。 指令包有一个单独的程序计数器地址,这个地址指向包的开始位置。指针不能在包的中点执行。 从架构上来说,下一个包执行前包执行的完成包括了寄存器以及主存的更新。因此,应用程序不能暴露在流水线下。 指令的内联 为了支持程序中关键程序段的有效编写,C编译器支持直接在C代码中表达Hexagon处理器的内联。如下的案例显示了指令内联如何用来表示XTYPE指令“Rdd = vminh(Rtt,Rss)”;

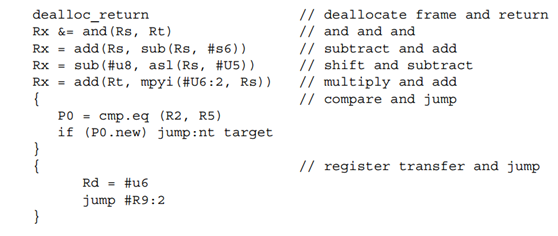

内联支持如下的指令类: l ALU32 l XTYPE l CR(分支预测操作) l SYSTEM(同步) 复合指令 Hexagon处理器支持复合指令,可以将一对共同使用的指令解码至一个指令。例如,下行每个都为一个复合指令:

使用复合指令可以减少编码尺寸并增加编码性能 开普勒指令 为了减少指令尺寸,Hexagon处理器支持开普勒指令集,该指令集将一对共同使用的指令集编码于32位的指令容器 与复合指令不同,开普勒指令不会有非常不同的语法(汇编代码与复合指令一样)。集合器负责识别何种指令可以被编码成单独的开普勒指令而不是两个一般的指令字。 为了将两种指令合成一个32位的字,开普勒被限制为常用指令的子集(导入指令,存储指令,分支指令,ALU)以及最常见的寄存器操作。

指令类 Hexagon处理器指令集被划分成了特定的指令类。类的不同决定了指令可以被如何以并行方式结合。 指令类与指令的类型相符合。例如ALU32类包含操作32位操作数的ALU指令。 下图列出了指令类以及子类:

指令包 指令可以被并在一起组成单独的指令包,指令包可以被并行的执行。指令包可以包含1,2,3,4个指令。 指令包必须在软件中清楚的定义。指令包通过使用花括号包含并以汇编语言表示,例如: { R0=R1; R2=R3; } 各种各样的规则以及限制规定了什么样类型的指令可以被组合,以及这些组合如何在包中出现。指令包的格式受到如下的具体限制: l 资源限制决定了包中可以出现多少种特殊类型的指令。Hexagon处理器具有定点计算的执行单元:每个指令在每个特定的单元上执行,每个单元一次只可以执行一个指令。因此,打比方来说,因为Hexagon处理器包含了两个load单元,一个包含了三个load命令的指令就是非法的。详细细节会在下一篇给出 l 组合限制是一组适用于以上并优于资源限制的规则。详细细节会在下一篇给出 l 独立限制保证了不会有先写后写磁头的风险。详细细节会在下一篇给出 l 顺序限制表明了指令包中的指令顺序。详细细节会在下一篇给出 l 对齐限制表明了内存中包的位置。这些规则的详细细节会在下一篇给出 注意:单独的指令在Hexagon处理器中被认为是包含了一个指令的指令包 包执行语义 包被定义为具有并行执行语义。也就是说,指令包的执行行为被定义如下: l 首先,包中所有的指令并行的读他们的源寄存器 l 其次,包中所有的指令都会执行 l 最后,包中所有的指令将会并行的写入其目标寄存器 例如,如下的指令: { R2= R3 ; R3 = R2 ; } 在第一阶段,寄存器R3和R2从寄存器文件中读取出来。接着,在执行完后,R2被写回R3的旧值,而R3的值被写回R2的旧值。因此,R2和R3的值被交换了。 序列语义 任何长度的包都可以被在代码中自由的混合。包可以被认为是一个原子单位:本质上来说,一个单独的大“指令”。从程序角度来说,一个包或者完全执行,要么不会执行;绝对不会部分执行。例如,如果一个包导致了内存异常,那么这个异常点在包之前就会被报错。 一个包含了多个导入或存储的指令可能会需要外部系统的服务。例如,假设一个需要执行两个导入操作同时未击中缓存的情况。这个包需要主存系统所提供的数据: l 从主存系统角度来说,这两个要求是串行执行的。 l 从程序角度来说,两个导入指令必须在包可以执行前完成 因此,从程序角度来说这个包是原子性的。 指令包有一个单独的程序计数器地址,这个地址指向包的开始位置。指针不能在包的中点执行。 从架构上来说,下一个包执行前包执行的完成包括了寄存器以及主存的更新。因此,应用程序不能暴露在流水线下。 指令的内联 为了支持程序中关键程序段的有效编写,C编译器支持直接在C代码中表达Hexagon处理器的内联。如下的案例显示了指令内联如何用来表示XTYPE指令“Rdd = vminh(Rtt,Rss)”;

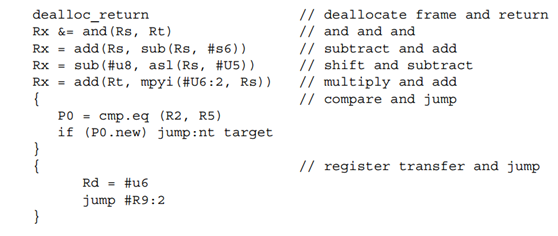

内联支持如下的指令类: l ALU32 l XTYPE l CR(分支预测操作) l SYSTEM(同步) 复合指令 Hexagon处理器支持复合指令,可以将一对共同使用的指令解码至一个指令。例如,下行每个都为一个复合指令:

使用复合指令可以减少编码尺寸并增加编码性能 开普勒指令 为了减少指令尺寸,Hexagon处理器支持开普勒指令集,该指令集将一对共同使用的指令集编码于32位的指令容器 与复合指令不同,开普勒指令不会有非常不同的语法(汇编代码与复合指令一样)。集合器负责识别何种指令可以被编码成单独的开普勒指令而不是两个一般的指令字。 为了将两种指令合成一个32位的字,开普勒被限制为常用指令的子集(导入指令,存储指令,分支指令,ALU)以及最常见的寄存器操作。